**TECHNICAL MANUAL**

# DIRECT SUPPORT, GENERAL SUPPORT, AND DEPOT MAINTENANCE MANUAL

**RADIO SET**

AN/GRC-144

(NSN 5820-00-926-7356)

This copy is a reprint which includes current pages from Changes 1 through 5.

HEADQUARTERS, DEPARTMENT OF THE ARMY

**AUGUST 1971**

### WARNING

DEATH or SERIOUS INJURY may result from hazards in this equipment, unless the proper safety measures are observed. READ and OBSERVE the referenced warnings concerning the following hazards in this equipment.

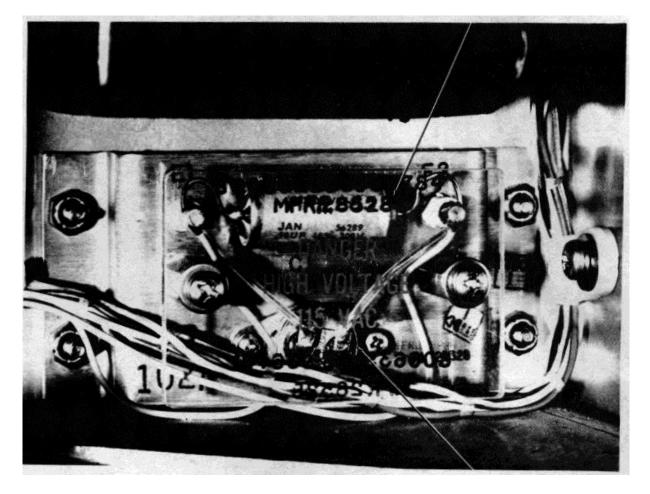

115 vac (para 3-4, 3-6, 3-12, 3-25, and 3-48)

HEADQUARTERS DEPARTMENT OF THE ARMY WASHINGTON, DC, 13 MAY 1985

Direct Support, General Support and

Depot Maintenance Manual

RADIO SETS AN/GRC-144(V)1 (NSN 5820-01-048-9110)

AN/GRC-144(V)2 (NSN 5820-01-061-7029)

AN/GRC-144(V)3 (NSN 5820-01-100-3093)

AND AN/GRC-144(V)4 (NSN 5820-01-099-7798)

TM 11-5820-695-35, 26 August 1971, is changed as follows:

- 1. Title of the manual is changed as shown above.

- 2. New or changed material is indicated by a vertical bar in the margin of the page.

- 3. Added or revised illustrations are indicated by a vertical bar in front of the figure caption.

- 4. Remove and insert pages as indicated below.

| Remove            | Insert                            |

|-------------------|-----------------------------------|

| i through vii     | i through xiv                     |

| 1-1               | 1-1 and 1-2                       |

| 2-1 through 2-4   | 2-1 through 2-4.2                 |

| None              | 2-6.1 through 2-6.3/(2-6.4 blank) |

| 2-7 through 2-10  | 2-7 through 2-10                  |

| 2-10.3 and 2-10.4 | 2-10.3 and 2-10.4                 |

#### Change

No. 6

| Remove              | Insert                                |

|---------------------|---------------------------------------|

| 2-16.1 and 2-16.2   | 2-16.1 through 2-16.14                |

| 2-23 through 2-24.2 | 2-23 through 2-24.17/(2-24.18 blank)  |

| 2-27 through 2-30   | 2-27 through 2-30.1/(2-30.2 blank)    |

| 2-43 through 2-46   | 2-43 through 2-46                     |

| 2-50.1 through 2-52 | 2-50.1 through 2-52                   |

| None                | 2-54.1/(2-54.2 blank)                 |

| 2-55 and 2-56       | 2-55 and 2-56                         |

| 2-59 through 2-62.1 | 2-59 through 2-62.3/(2-62.4 blank)    |

| 2-65 and 2-66       | 2-65 through 2-66.1/(2-66.2 blank)    |

| 2-71 through 2-74   | 2-71 through 2-74.2                   |

| None                | 2-108.1 and 2-108.2                   |

| 2-109 through 2-116 | 2-109 through 2-116.1/(2/116.2 blank) |

| None                | 2-121 through 2-141/(2-142 blank)     |

| 3-1 through 3-4     | 3-1 through 3-4                       |

| 3-7 through 3-12    | 3-6.1 through 3-12.1/(3-12.2 blank)   |

| 3-15 through 3-20   | 3-15 through 3-20                     |

| 3-25 and 3-26       | 3-25 and 3-26                         |

| 3-29 through 3-34   | 3-29 through 3-34                     |

| None                | 3-36.1/(3-36.2 blank)                 |

| None                | 3-38.1/(3-38.2 blank)                 |

| None                | 3-44.1/(3-44.2 blank)                 |

| None                | 3-50.3/(3-50.4 blank)                 |

| 3-51 through 3-62   | 3-51 through 3-62                     |

|                     |                                       |

| Remove            | Insert                               |

|-------------------|--------------------------------------|

| None              | 3-66.1 and 3-66.2                    |

| 3-71 and 3-72     | 3-71 and 3-72                        |

| None              | 3-74.1 through 3-74.5/(3-74.6 blank) |

| 3-75 through 3-84 | 3-75 through 3-84                    |

| 3-87 through 3-96 | 3-87 through 3-96                    |

| None              | 3-101 through 3-115/(3-116 blank)    |

| 4-1 and 4-2       | 4-1 through 4-2.1/(4-2.2 blank)      |

| 4-5 through 4-8   | 4-5 through 4-8.1/(4-8.2 blank)      |

| None              | 4-18.1/(4-18.2 blank)                |

| None              | 4-48.3 and 4-48.4                    |

| None              | 4-50.1 and 4-50.2                    |

| None              | 4-52.1/(4-52.2 blank)                |

| 5-1               | 5-1 and 5-2                          |

| 5-5               | 5-5                                  |

| None              | 5-5.1                                |

| None              | 5-13.1                               |

| None              | 5-18.3 and 5-18.5                    |

| 5-19              | 5-19                                 |

| None              | 5-23.1                               |

| None              | 5-35.1 through 5-35.7                |

| 5-37              | 5-37                                 |

| None              | 5-41.1                               |

| None              | 5-43.1                               |

| None              | 5-49.1                               |

| Remove                                                              | Insert                              |

|---------------------------------------------------------------------|-------------------------------------|

| None                                                                | 5-62.3 through 5-62.13              |

| None                                                                | 5-65.1                              |

| None                                                                | 5-89.3 through 5-89.35              |

| None                                                                | 5-125.1                             |

| None                                                                | 5-127.1                             |

| None                                                                | 5-143.1 and 5-143.3                 |

| None                                                                | 5-157.1                             |

| 5-159                                                               | 5-159                               |

| 5-181                                                               | 5-181                               |

| None                                                                | 5-184.3 through 5-184.19            |

| None                                                                | 5-198.1 and 5-198.3                 |

| None                                                                | 5-202.1 and 5-202.3                 |

| None                                                                | 5-215 through 5-265                 |

| A-1                                                                 | A-1/(A-2 blank)                     |

| Index 1 through Index 10                                            | Index 1 through 21/(Index 22 blank) |

| File this change sheet in front of the publication for reference pu | urposes.                            |

By Order of the Secretary of the Army:

Official

5.

JOHN A. WICKHAM JR. General, United States Army Chief of Staff

DONALD J. DELANDRO Brigadier General, United States Army The Adjutant General

DISTRIBUTION:

To be distributed in accordance with DA Form 12-51 literature requirements for the AN/GRC-144(V)

| CHANGE | ) |

|--------|---|

|        | ) |

)

No. 5

#### DS, GS, AND DEPOT MAINTENANCE MANUAL

#### RADIO SET AN/GRC-144(V)1 (NSN 5820-00-926-7356)

TM 11-5820-695-35, 26 August 1971, Is changed as follows

- 1. New or changed material Is indicated by a vertical bar in the margin of the page.

- 2. Added or revised illustrations are Indicated by a vertical bar in front of the figure caption.

- 3. Remove and insert pages as indicated below

#### Remove

#### Insert

| i and ii           | Warning Pages a and b<br>i and ii |

|--------------------|-----------------------------------|

| 1-0<br>1-1         | 1-1                               |

| 2-55 through 2-58  | 2-55 through 2-58                 |

| 2-75 through 2-78  | 2-75 through 2-78                 |

| 3-19 and 3-20      | 3-19 and 3-20                     |

|                    | 3-34.1 and 3-34.2                 |

| 3-49 and 3-50      | 3-49 and 3-50                     |

|                    | 3-50.1 and 3-50.2                 |

| 3-57 and 3-58      | 3-57 and 3-58                     |

| 3-73 and 3-74      | 3-73 and 3-74                     |

| 4-3 and 4-4        | 4-3 and 4-4                       |

| FO 5-17            | FO 5-17                           |

| FO 5-22            | FO 5-22                           |

| FO 5-27            | FO 5-27                           |

| FO 5-31            | FO 5-31                           |

| FO 5-33            | FO 5-33                           |

| FO 5-36            | FO 5-36                           |

| FO 5-37            | FO 5-37                           |

| FO 5-38            | FO 5-38                           |

| FO 5-62<br>FO 5-63 | FO 5-62<br>FO 5-63                |

| FO 5-03<br>FO 5-73 | FO 5-63<br>FO 5-73                |

| FO 5-74            | FO 5-74                           |

|                    | 10374                             |

4. File this change sheet in the front of this publication for reference purposes.

By Order of the Secretary of the Army

Official:

E. C. MEYER General, United States Army Chief of Staff

ROBERT M. JOYCE Major General, United States Army The Adjutant General

DISTRIBUTION:

To be distributed in accordance with DA Form 12-51 Direct and General Support Maintenance requirements for AN/GRC-144

2

3

4

5

SAFETY STEPS TO FOLLOW IF SOMEONE IS THE VICTIM OF ELECTRICAL SHOCK

DO NOT TRY TO PULL OR GRAB THE INDIVIDUAL

IF POSSIBLE, TURN OFF THE ELECTRICAL POWER

IF YOU CANNOT TURN OFF THE ELECTRICAL POWER, PULL, PUSH, OR LIFT THE PERSON TO SAFETY USING A DRY WOODEN POLE OR A DRY ROPE OR SOME OTHER INSULATING MATERIAL

SEND FOR HELP AS SOON AS POSSIBLE

AFTER THE INJURED PERSON IS FREE OF CONTACT WITH THE SOURCE OF ELECTRICAL SHOCK, MOVE THE PERSON A SHORT DISTANCE AWAY AND IMMEDIATELY START ARTIFICIAL RESUSCITATION

#### WARNING HIGH VOLTAGE is used in this equipment DEATH ON CONTACT MAY RESULT IF SAFETY PRECAUTIONS ARE NOT OBSERVED DO NOT SERVICE OR ADJUST ALONE

Maintenance adjustments of this equipment are made with power applied. Be careful when working near the interior of the equipment, or near the ac power distribution.

Do not attempt internal service or adjustment unless another person, capable of rendering first aid or resuscitation, is present.

A periodic review of safety precautions in TB 385-4, safety precautions for Maintenance of Electrical/Electronic Equipment, is recommended. When the equipment is operated with covers removed, DO NOT TOUCH exposed connections or components. MAKE CERTAIN you are not grounded when making connections or adjusting components inside the test instrument.

# DON'T TAKE CHANCES!!

Operator and maintenance personnel should also be familiar with the requirements of TB SIG 291 before attempting installation or operation of the equipment covered in this manual. Failure to follow the requirements of TB SIG 291 could result in injury or DEATH.

#### WARNING

Fumes of TRICHLOROTRIFLUOROETHANE are poisonous. Provide adequate ventilation whenever you use TRICHLOROTRIFLUOROETHANE. Do not use solvent near heat or open flame. TRICHLOROTRIFLUOROETHANE will not burn, but heat changes the gas into poisonous, irritating fumes. DO NOT breathe the fumes or vapors. TRICHLOROTRIFLUOROETHANE dissolves natural skin oils. DO NOT get the solvent on your skin, use gloves, sleeves and an apron which the solvent cannot penetrate. If the solvent is taken internally, consult a physician immediately.

Change 5 b

No. 11-5820-695-35

#### Direct Support, General Support and Depot Maintenance Manual RADIO SETS AN/GRC-144(V)1 (NSN 5820-01-048-9110) AN/GRC-144(V)2 (NSN 5820-01-061-7029) AN/GRC-144(V)3 (NSN 5820-01-100-3303) AND AN/GRC-144(V)4 (NSN 5820-01-099-7798)

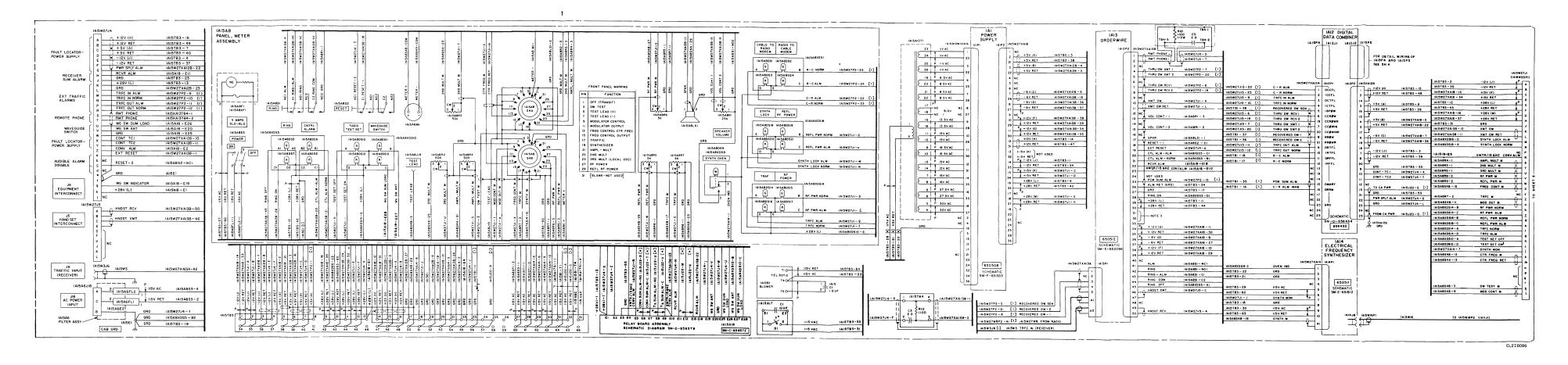

| CHAPTER  | 1.          | INTRODUCTION                                                                                        | Paragraph<br>1-1 - 1-7       | Page<br>1-1 - 1-2              |

|----------|-------------|-----------------------------------------------------------------------------------------------------|------------------------------|--------------------------------|

| CHAPTER  | 2.          | FUNCTIONING OF EQUIPMENT                                                                            |                              |                                |

| Section  | I.          | Functions of Radio Sets AN/GRC-144<br>(V), AN/GRC-144(V)3 and AN/GRC-                               |                              |                                |

|          | П.          | 144(V)4<br>Functioning of Transmitter,<br>Radio T-1054(P)/GRC-144(V) and                            | 2-1 - 2-26                   | 2-1 - 2-52                     |

|          | III.        | T-1054(P)A/GRC-144(V) Circuits<br>Functioning of Receiver, Radio<br>R-1467(P)/GRC-144(V) and R-1467 | 2-27 - 2-64.1                | 2-54.1 - 2.108.2               |

|          | IV.         | (P)A/GRC-144(V) Circuits<br>Functioning of Indicator, Antenna                                       | 2-65 - 2-77                  | 2-109 - 2-118                  |

|          |             | Alignment ID-1708/GRC Circuits                                                                      | 2-78 - 2-79                  | 2-120                          |

|          | V.          | Functioning of Waveguide Switch<br>Position Indicator Circuits                                      | 2-80                         | 2-121 - 2-125                  |

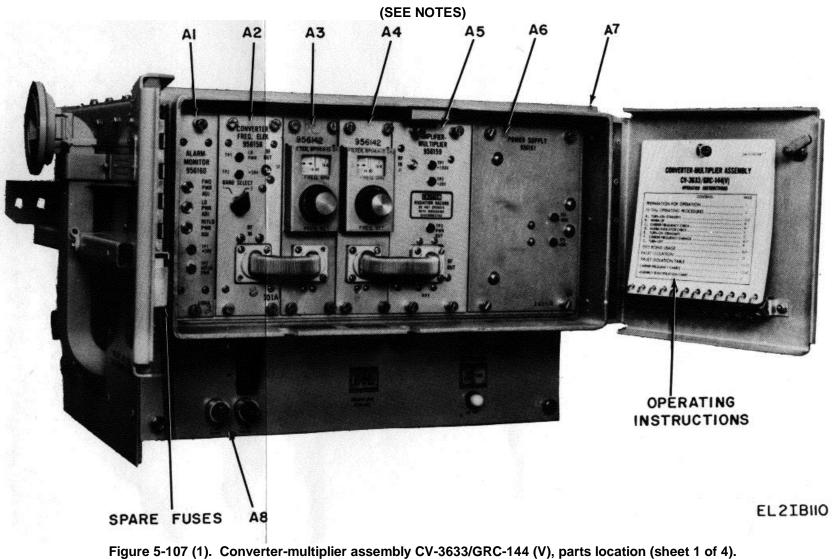

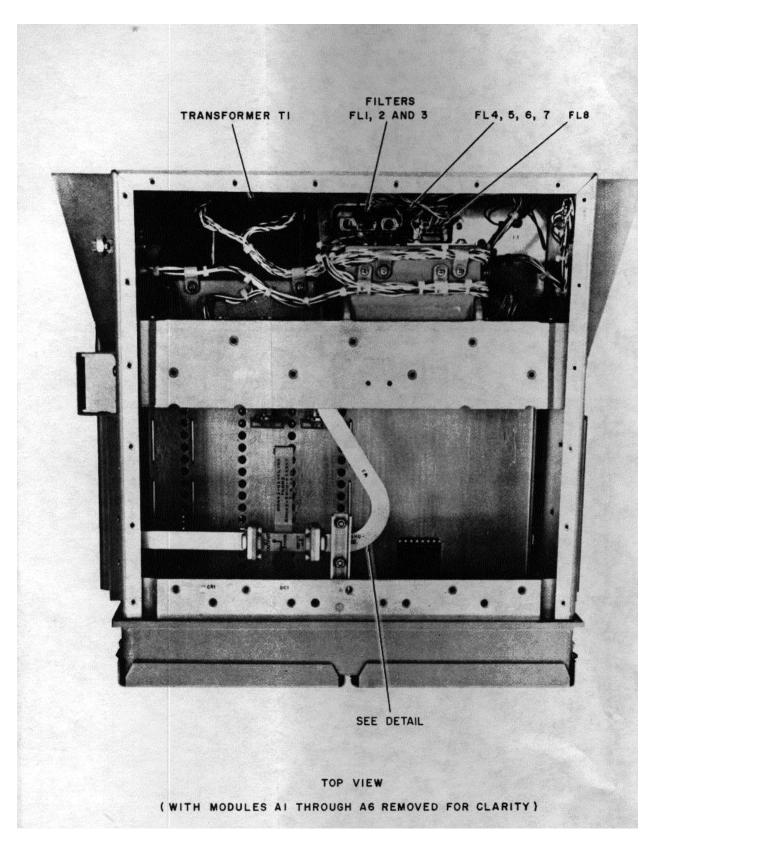

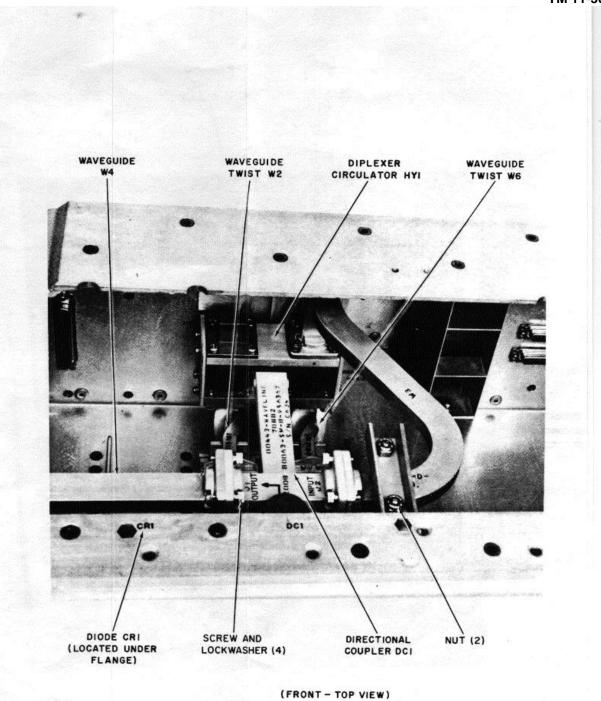

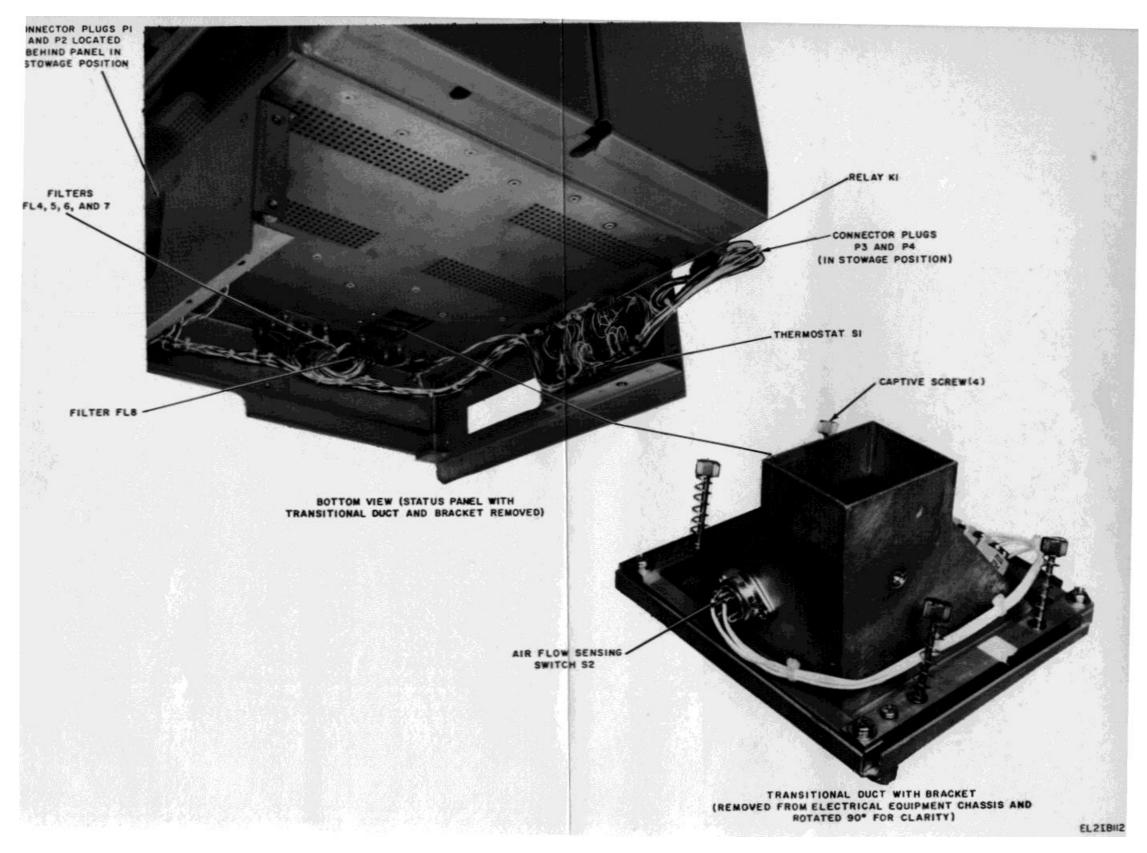

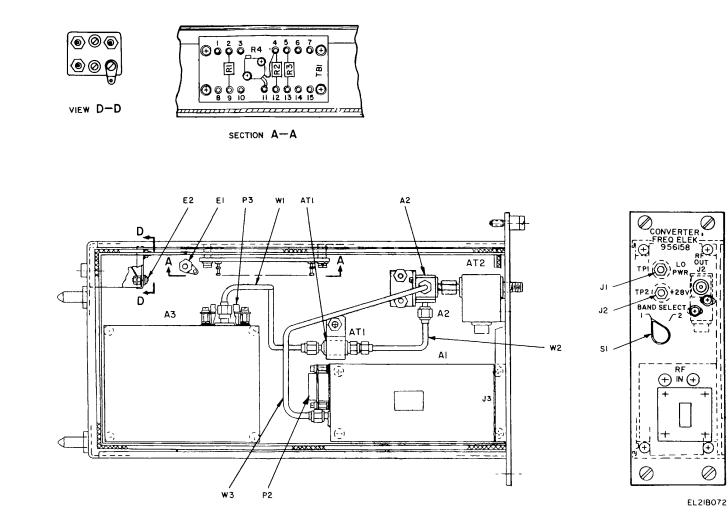

|          | VI.         | Functioning of Converter-Multiplier<br>Assembly CV-3633/GRC-144(V)                                  |                              |                                |

|          |             | Circuits                                                                                            | 2-81 - 2-87                  | 2-126 - 2-141                  |

| CHAPTER  | 3.          | DIRECT SUPPORT MAINTENANCE                                                                          |                              |                                |

| Section  | ١.          | General                                                                                             | 3-1 - 3-3                    | 3-1 - 3-2.1                    |

|          | II.         | Troubleshooting                                                                                     | 3-4 - 3-18.4                 | 3-2.2 - 3-30.7                 |

|          | III.<br>IV. | Repairs<br>Calibration and adjustment                                                               | 3-19 - 3-53.6<br>3-54 - 3-67 | 3-30.8 - 3-74.6<br>3-75 - 3-83 |

|          | V.          | Direct support testing procedures                                                                   | 3-68 - 3-79                  | 3-83 - 3-115                   |

| CHAPTER  | 4.          | DEPOT MAINTENANCE                                                                                   |                              |                                |

| Section  | ١.          | Repairs                                                                                             | 4-1 - 4-13                   | 4-1 - 4-9                      |

|          | II.         | Testing procedures                                                                                  | 4-14 - 4-16                  | 4-9 - 4-59                     |

| CHAPTER  | 5.          | DIAGRAMS5-                                                                                          | 15-5                         | 5-1 - 5-265                    |

| APPENDIX | Α.          | REFERENCES                                                                                          |                              | A-1                            |

| INDEX    |             |                                                                                                     |                              | Index 1                        |

# LIST OF ILLUSTRATIONS

| Figure<br><u>Number</u> | Title                                                                                                                                       | <u>Page</u>      |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------|

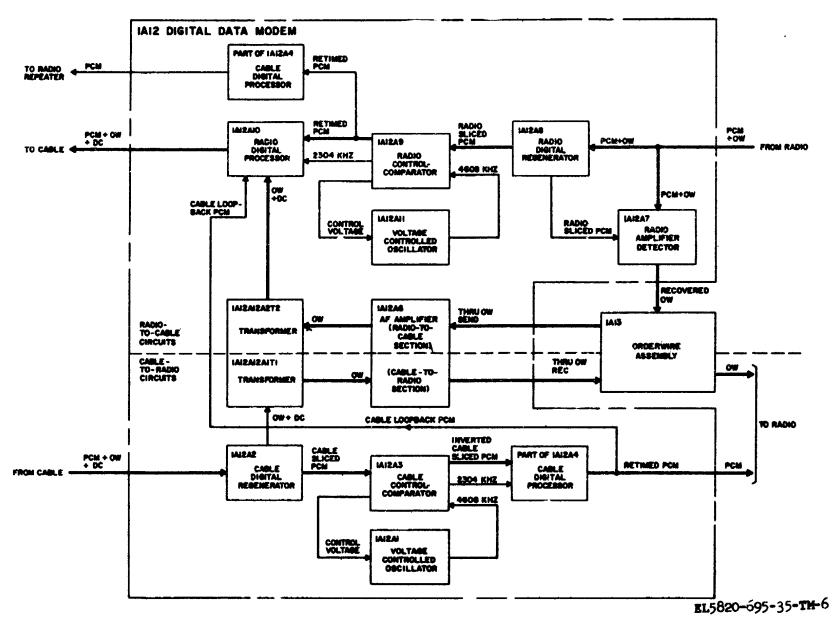

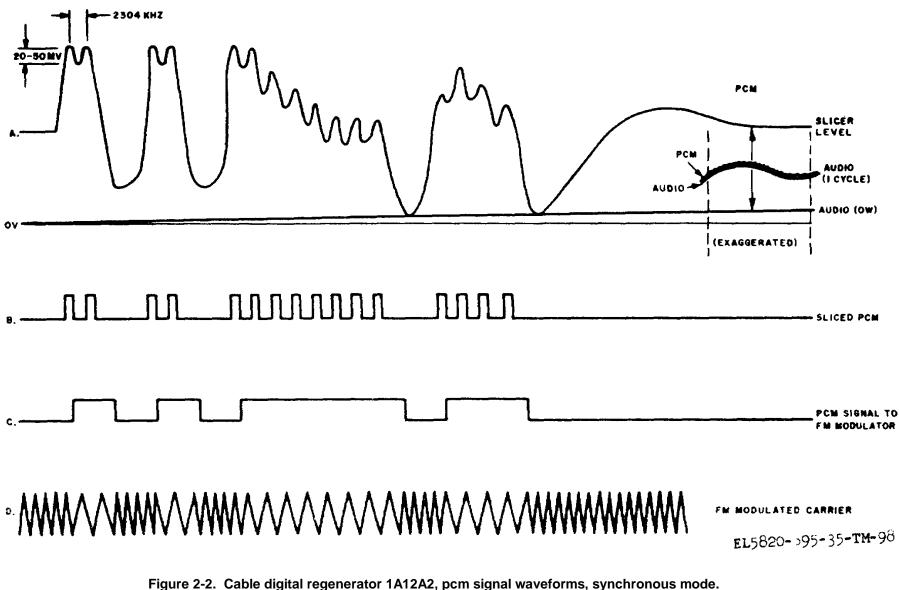

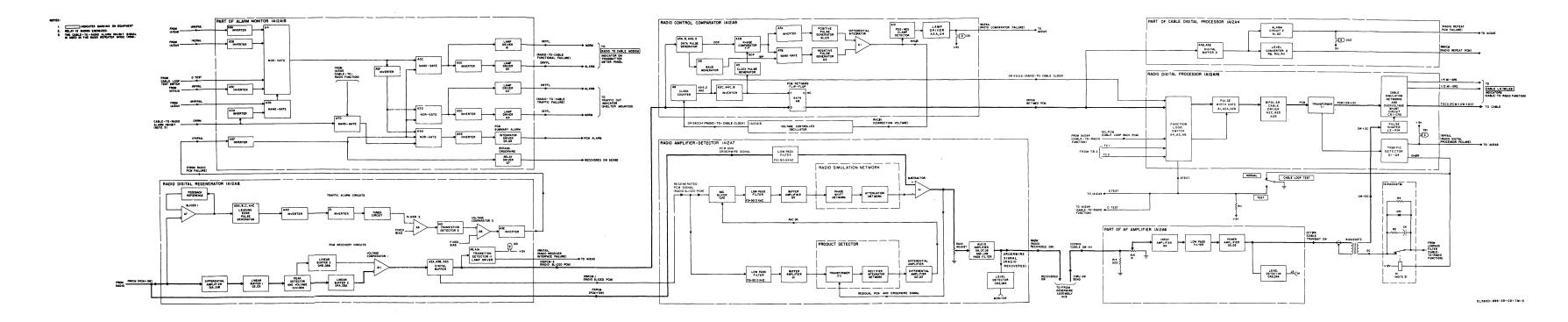

| 2-1                     | Digital data modem 1A12, overall block diagram                                                                                              |                  |

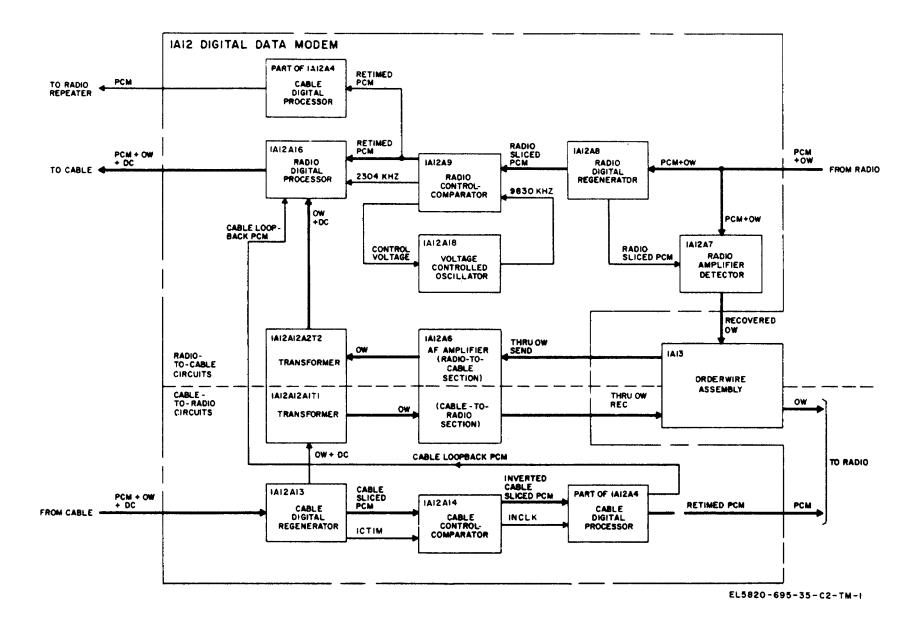

| 2-1.1                   | synchronous mode<br>Digital data modem 1A12, overall block diagram                                                                          | 2-10.2           |

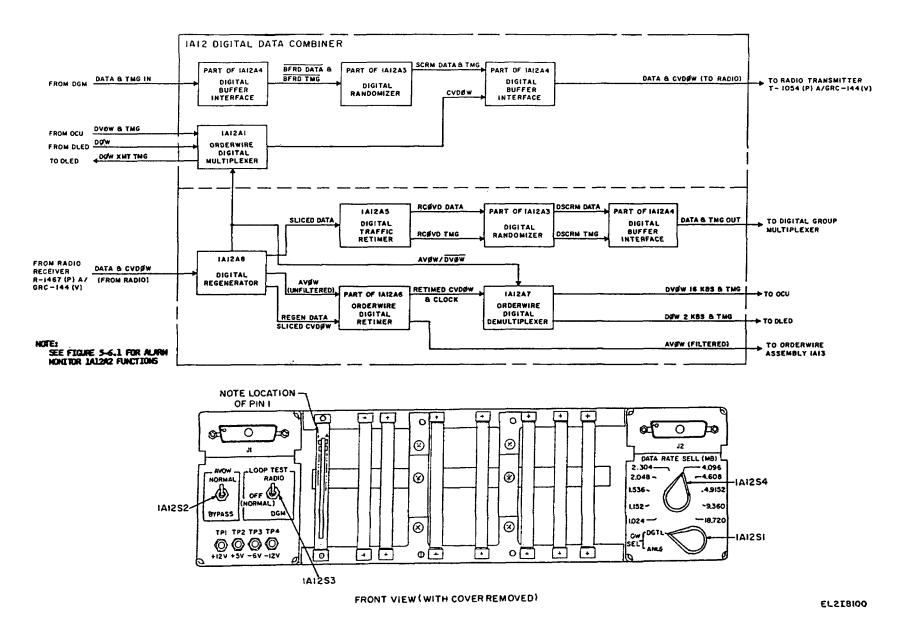

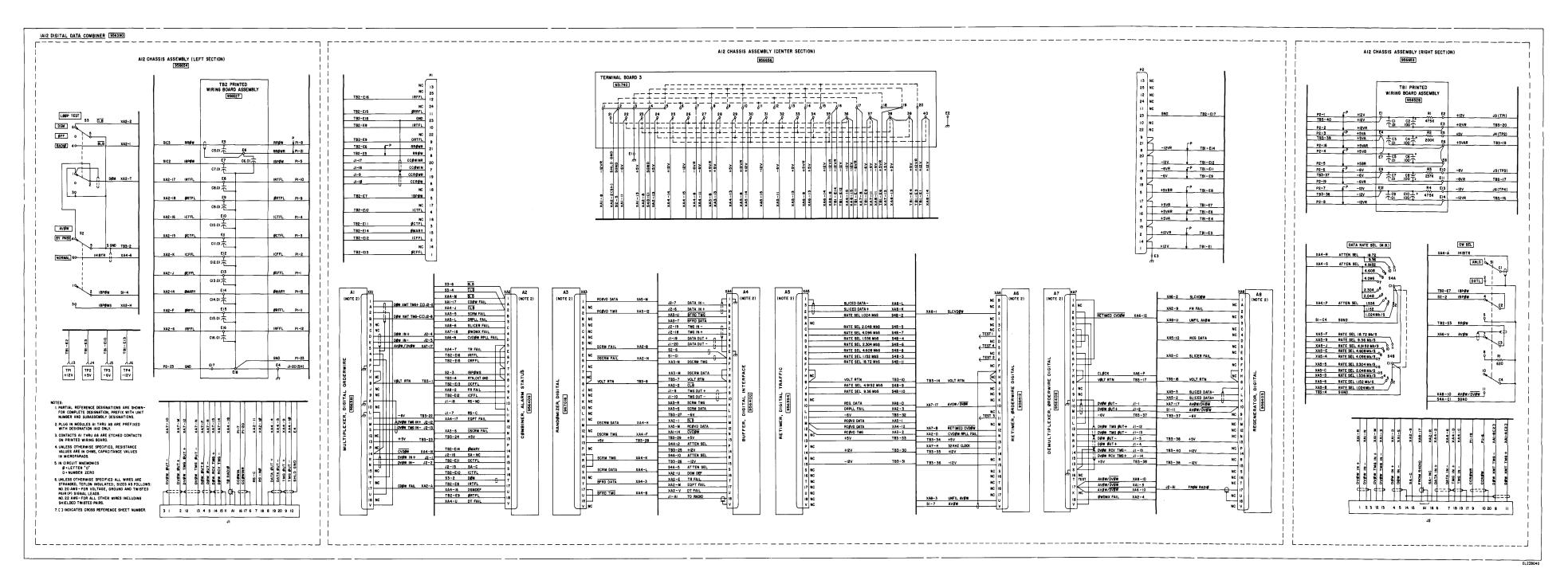

| 2-1.2<br>2-2            | asynchronous mode<br>Digital data combiner 1A12, overall block diagram<br>Cable digital regenerator 1A12A2, PCM signal                      | 2-10.3<br>2-10.4 |

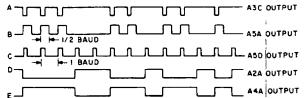

| 2-2.1                   | waveforms synchronous mode<br>Cable digital regenerator 1A12A12, PCM signal                                                                 | 2-11             |

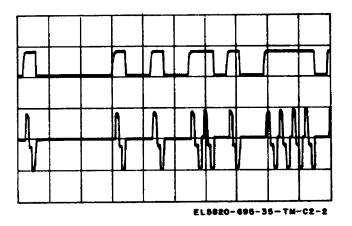

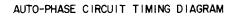

| 2-2.2                   | waveform asynchronous mode<br>Digital data combiner 1A12 waveforms                                                                          | 2-12.2<br>2-16.5 |

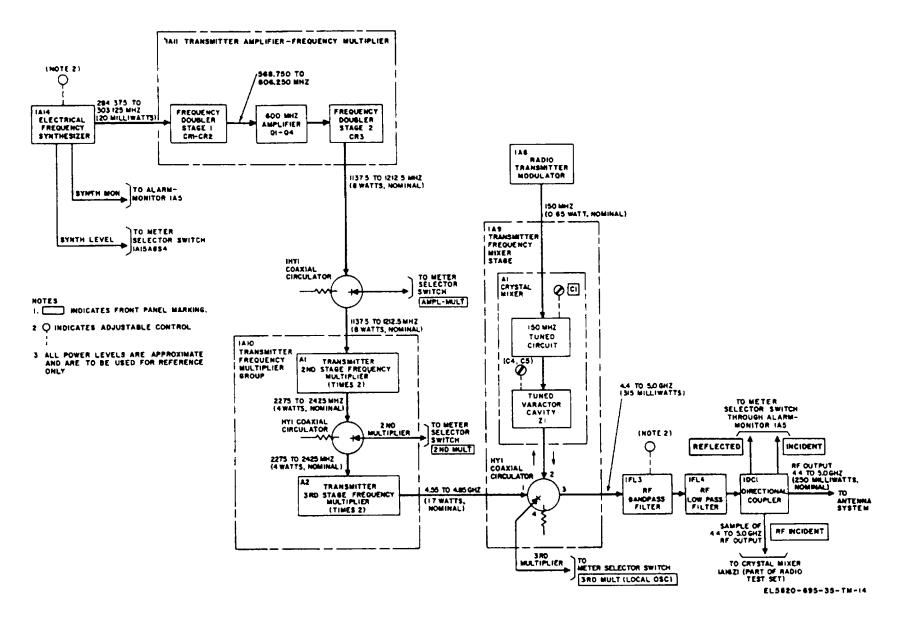

| 2-3                     | Transmitter. Radio T-1054I(P/GRC-144'(V)I; local oscillator<br>and mixer circuits, functional block diagram                                 | 2-30.1           |

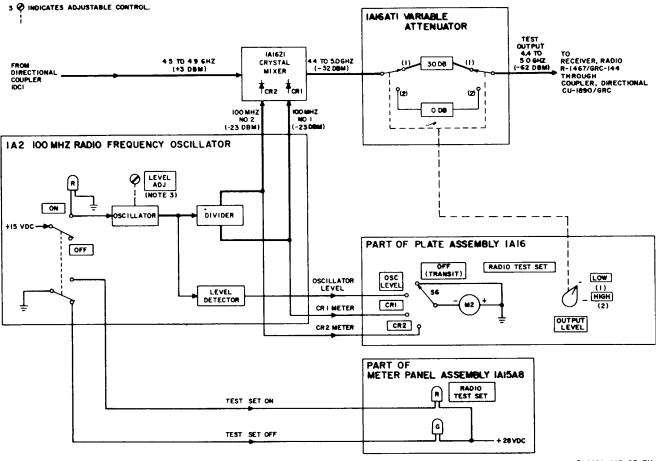

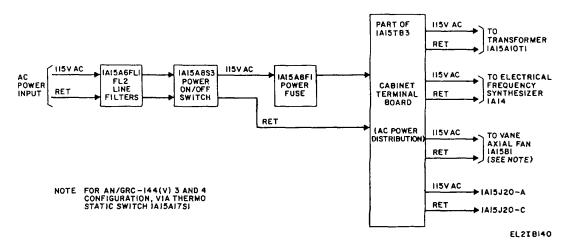

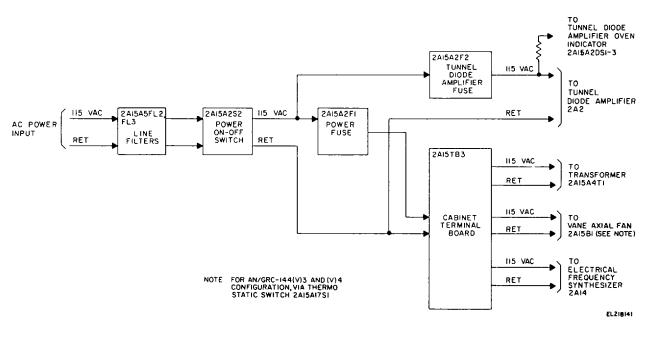

| 2-4<br>2-5              | Radio test set (P/O 1A16), block diagram<br>Transmitter, Radio T-1054(P)/G(C-144(V) and<br>T-1054(P)A/GRC-144(V) primary power distribution | 2-43             |

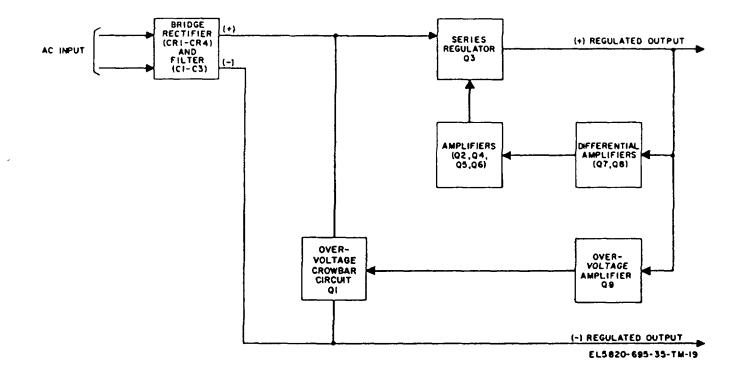

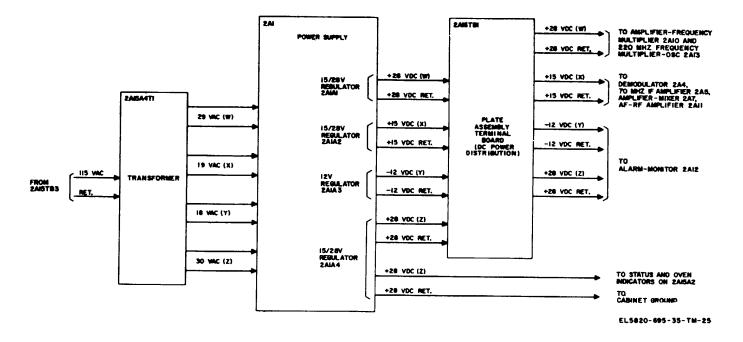

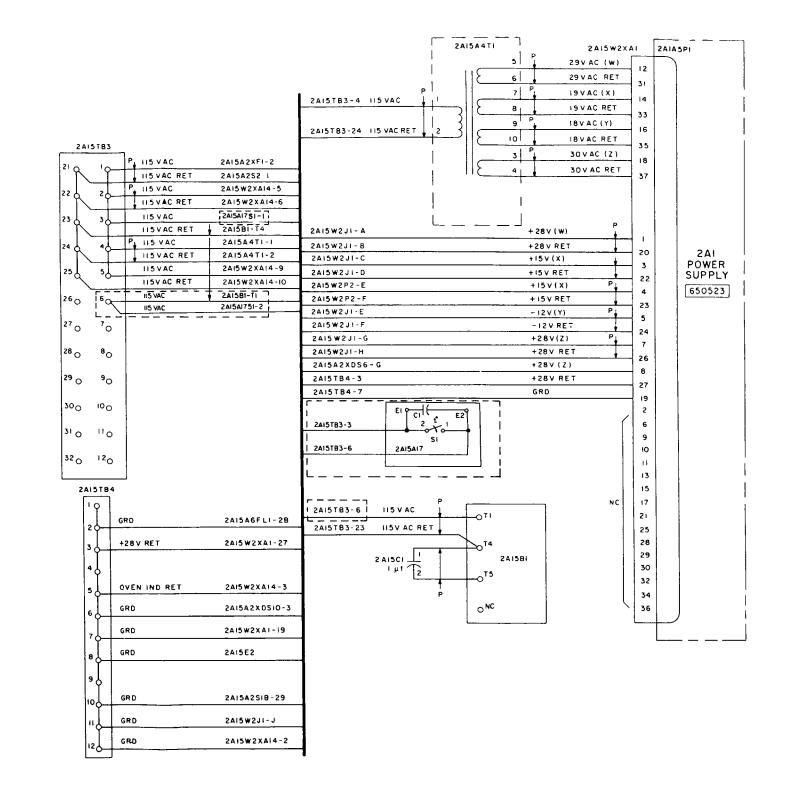

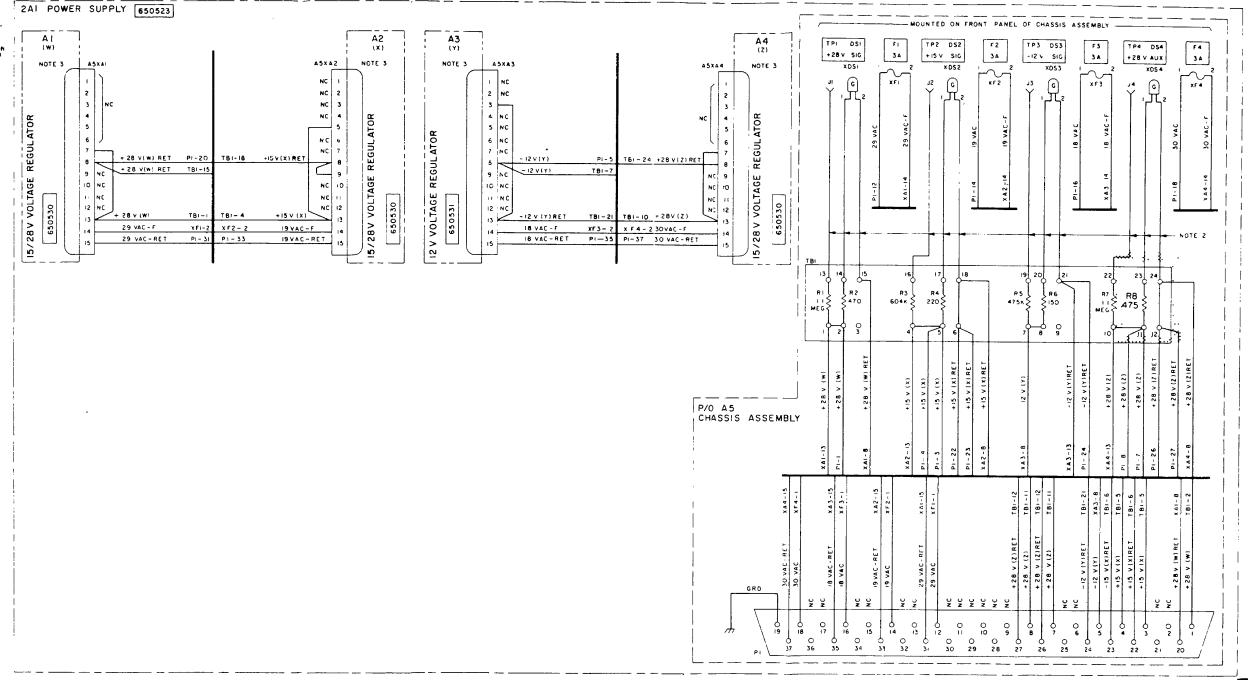

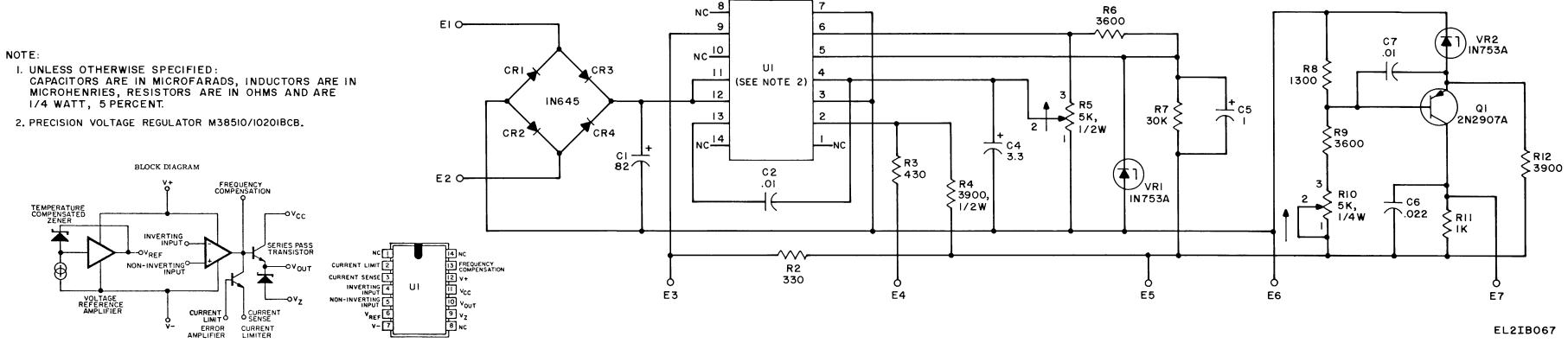

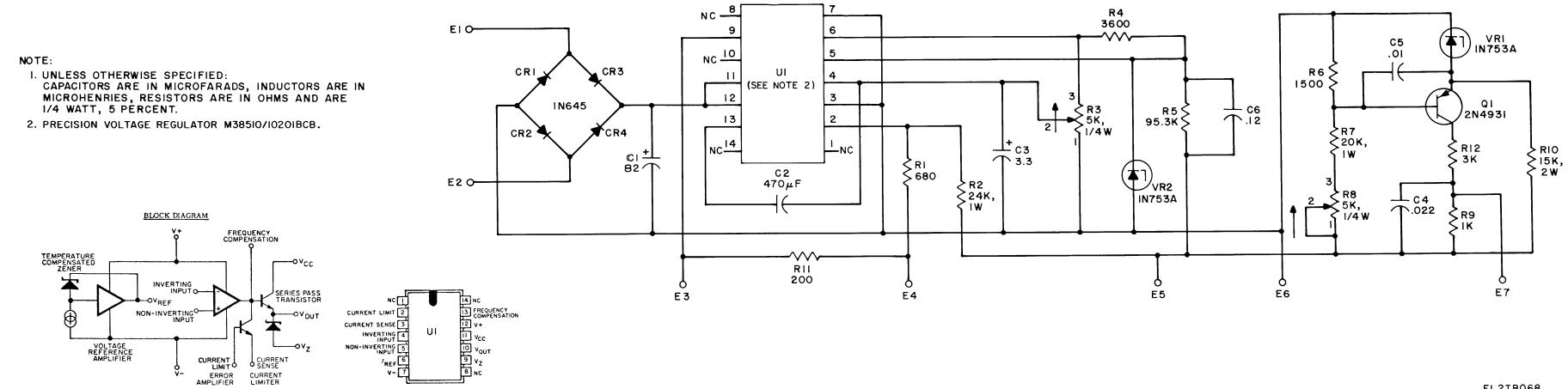

| 2-6<br>∎2-7             | block diagram<br>Typical voltage regulator 1A1A1-1A1A12 block diagram<br>Receiver Radio R-1467(P)/GRC-144(V) and                            | 2-44.1<br>2-44.1 |

|                         | R-1467(P)A/GRC-144(V) primary power distribution<br>block diagram                                                                           | 2-52             |

| 2-8                     | Receiver, Radio R-1467(P)/GRC-144(V) DC power distr                                                                                         | 2-54             |

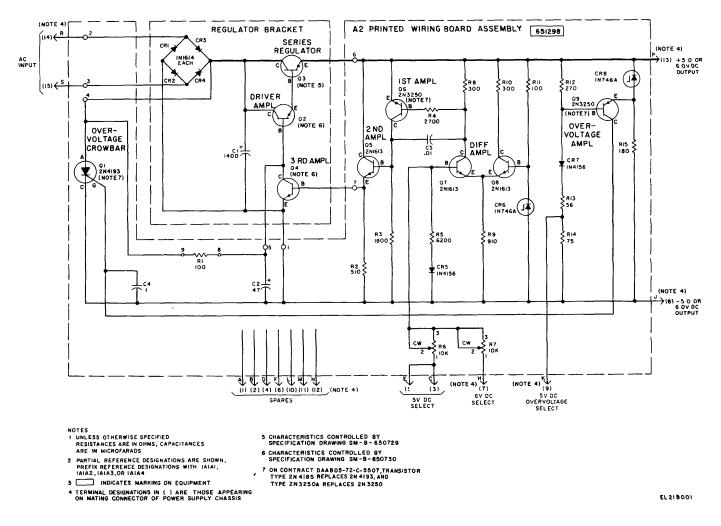

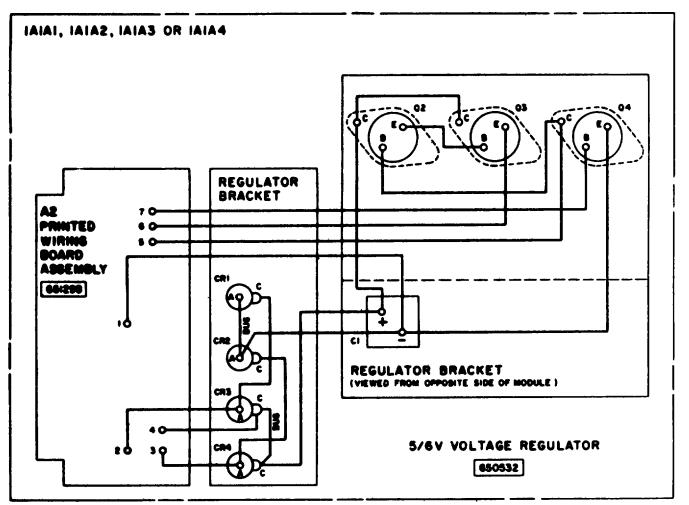

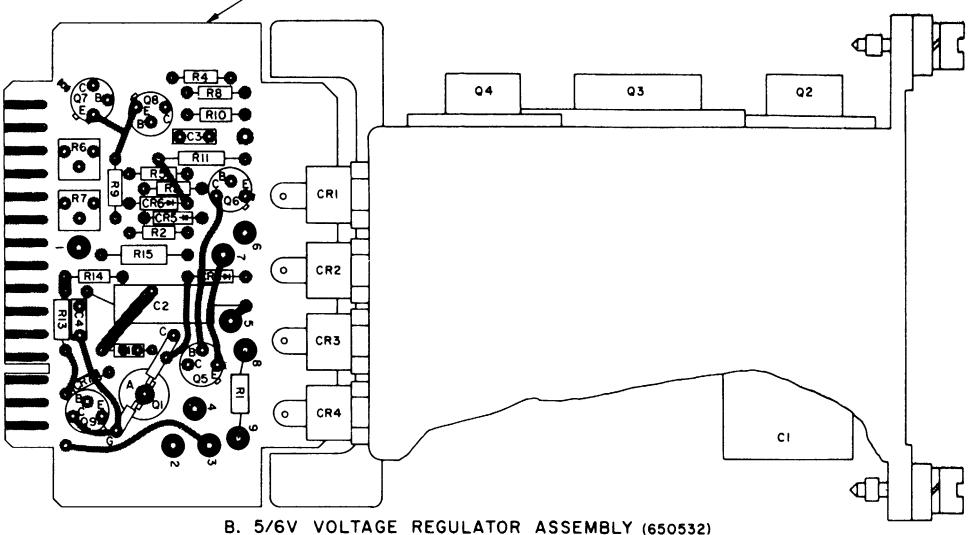

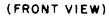

| 2-9                     | 5/6 V voltage regulator 1A1A1 through 1A1A4<br>schematic diagram                                                                            | 2-56             |

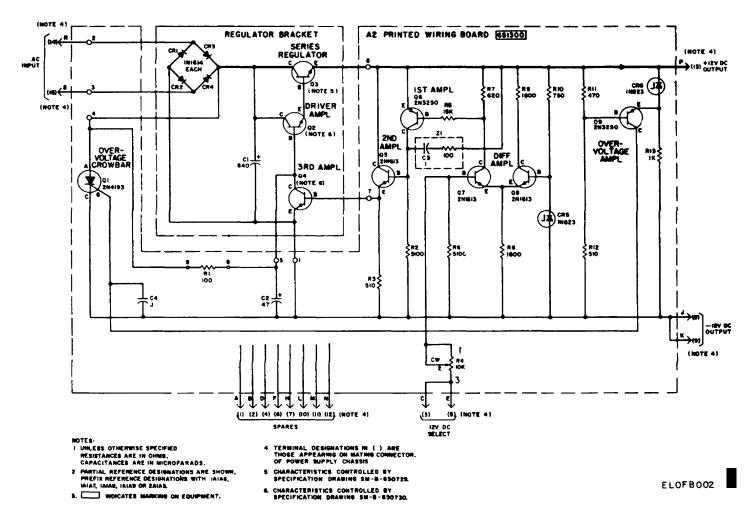

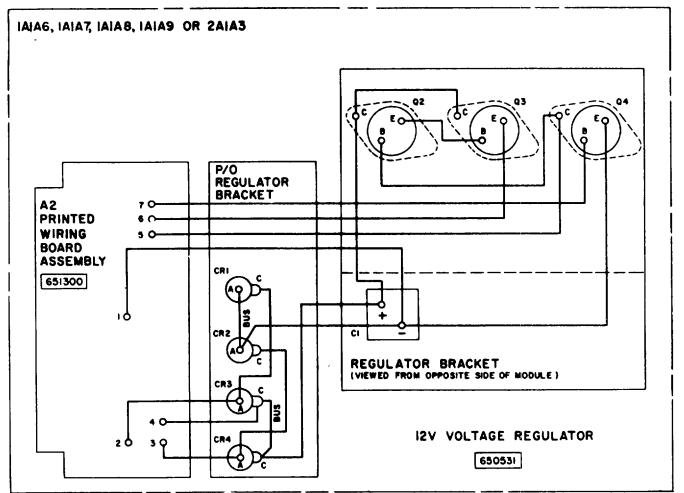

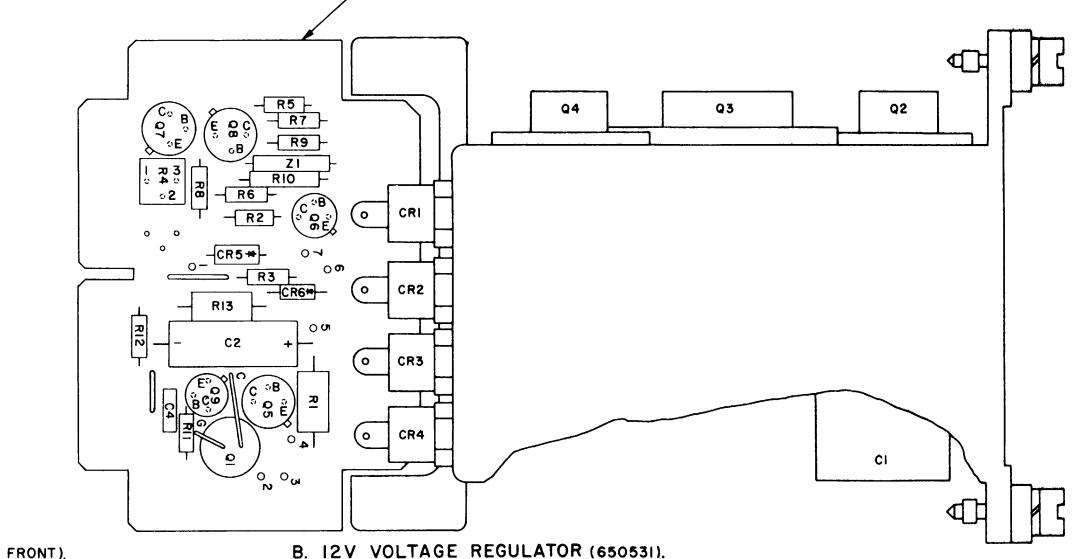

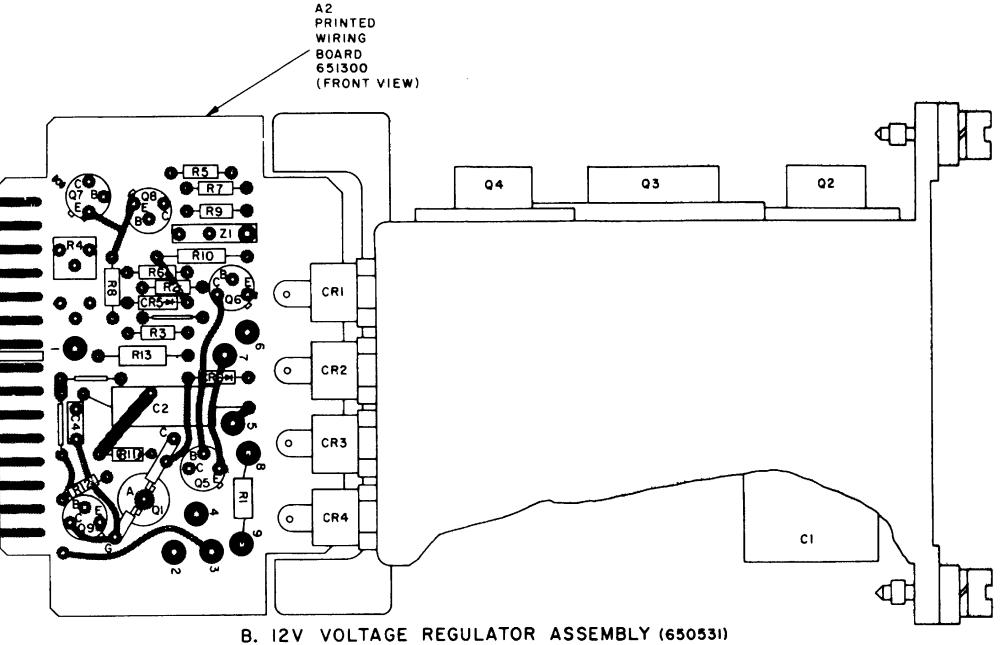

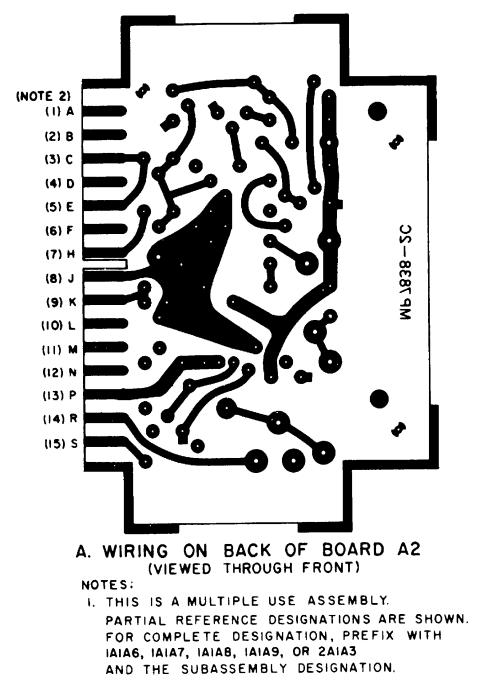

| 2-10                    | 12V voltage regulator 1A1A6 through 1A1A9 and 2A1A3, schematic diagram                                                                      | 2-58             |

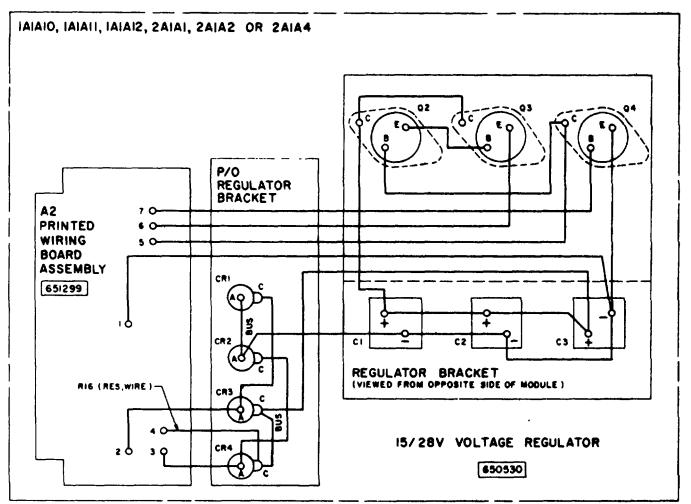

| 2-11                    | 15/28V voltage regulator 1AA10 through 1A1A12,<br>2A1A1, 2A1A2 and 2A1A4 schematic diagram                                                  | 2-50             |

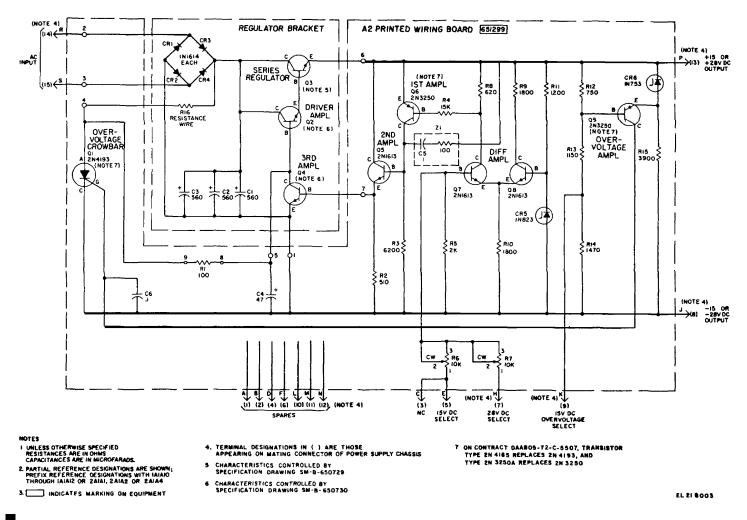

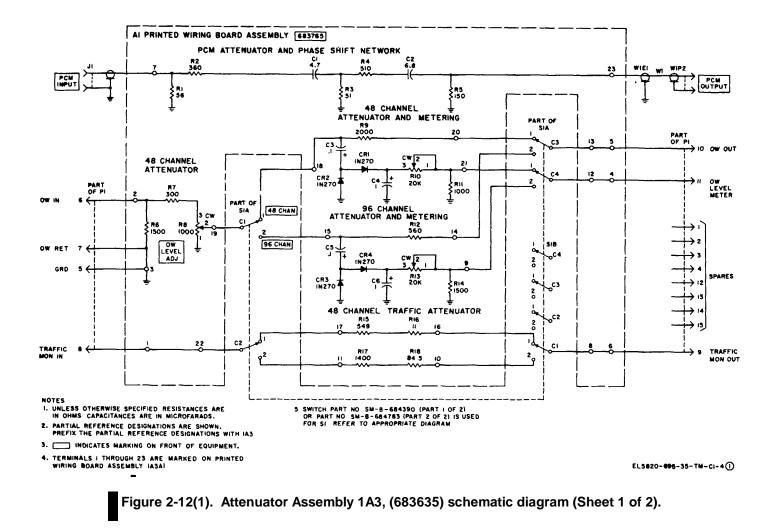

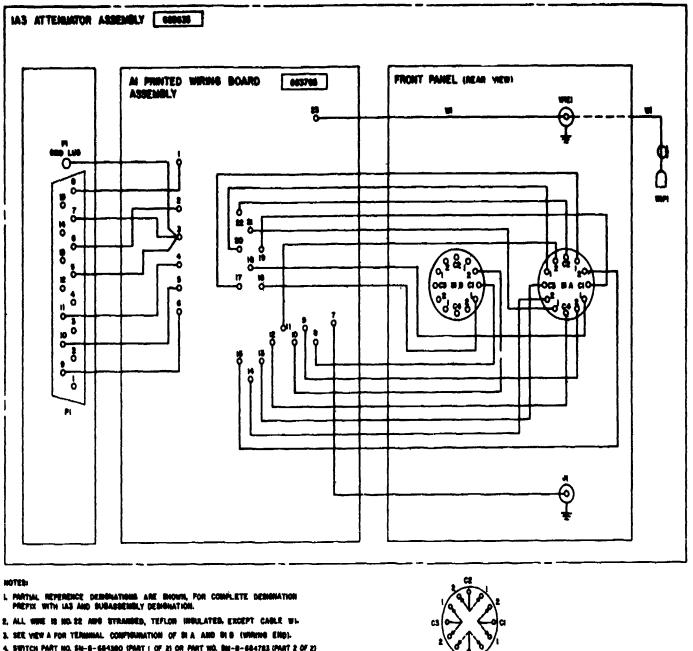

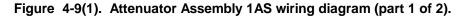

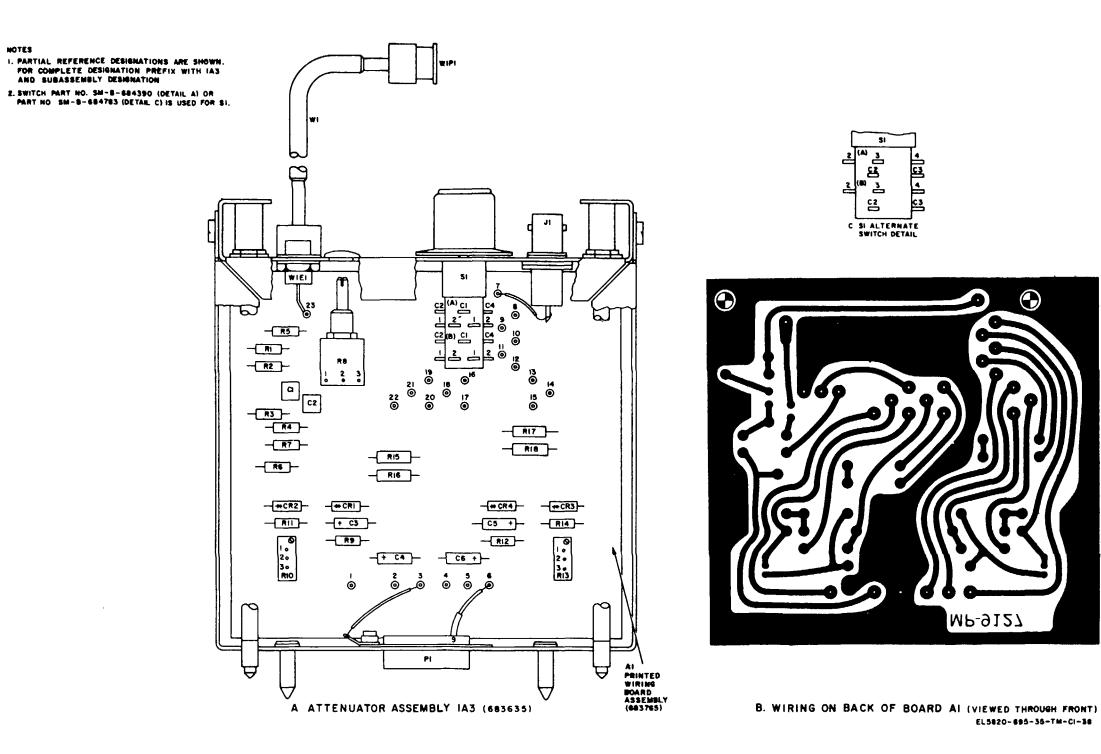

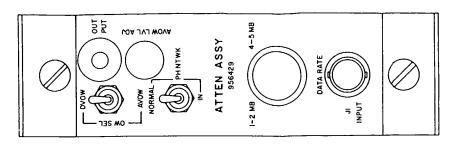

| 2-12(1)                 | Attenuator assembly 1A3 (683635), schematic diagram<br>(Sheet 1 of 2)                                                                       | 2-59             |

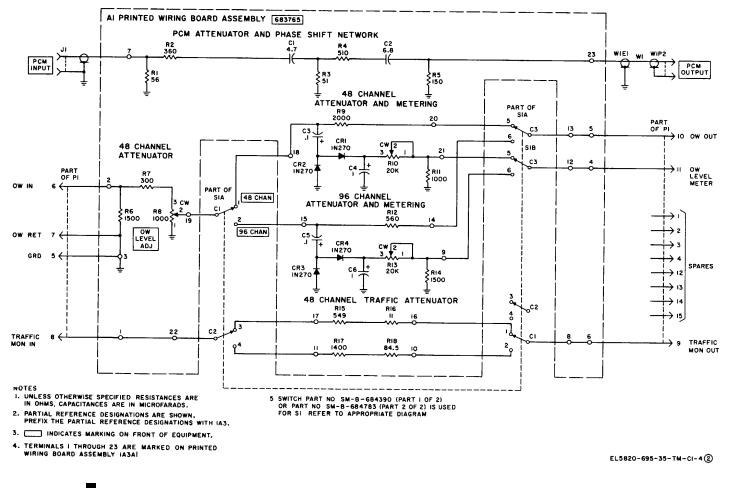

| 2-12(1)                 | Attenuator assembly 1A3 (683635), schematic diagram                                                                                         | 2-61             |

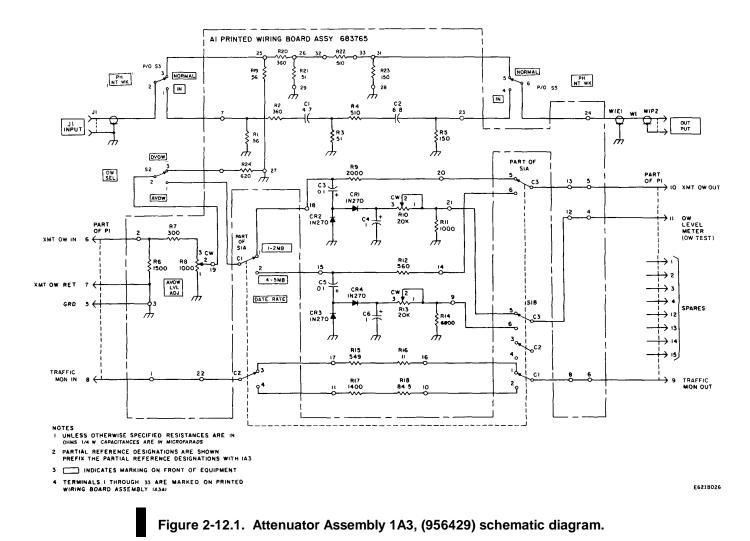

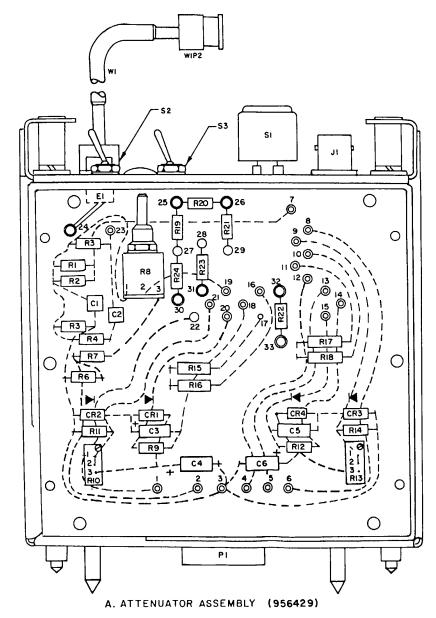

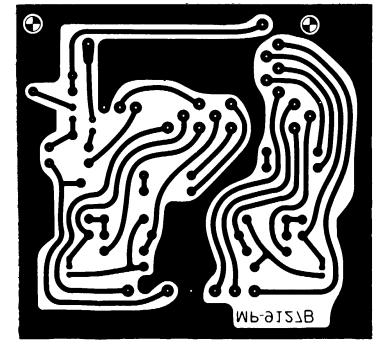

| 2-12.1                  | (Sheet 2 of 2)<br>Attenuator assembly 1A3 (956429), schematic diagram                                                                       | 2-02<br>2-62.1   |

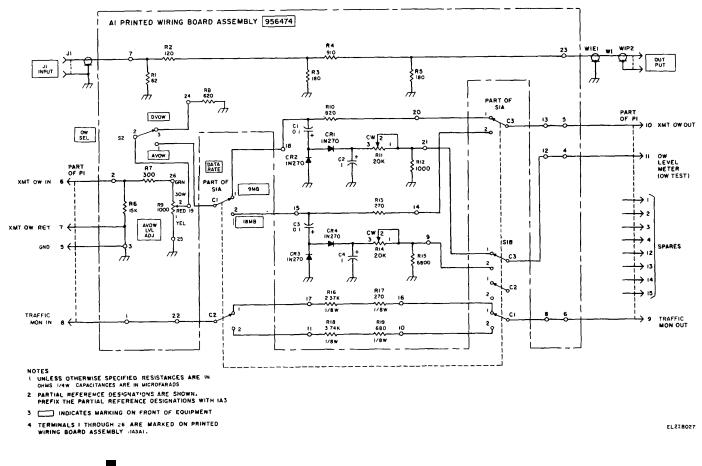

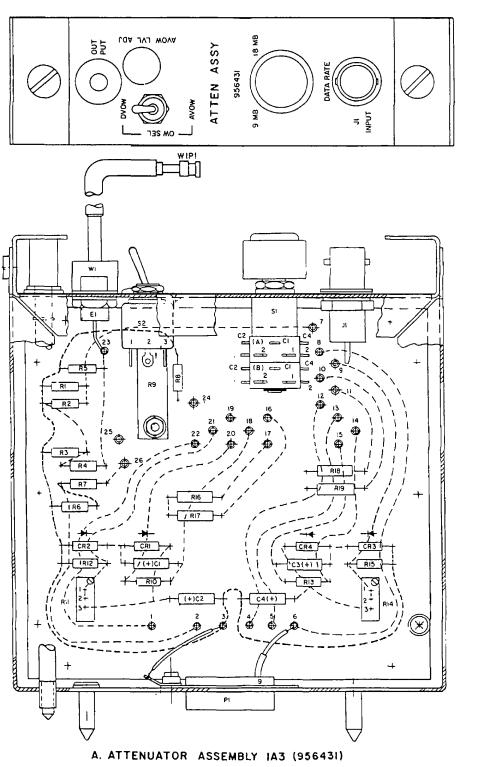

| 2-12.2                  | Attenuator assembly 1A3 (956431), schematic diagram                                                                                         | 2-62.2           |

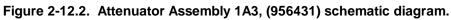

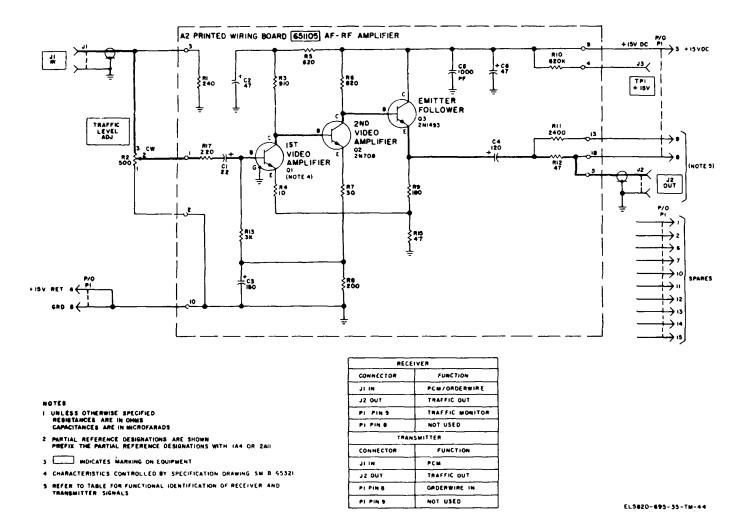

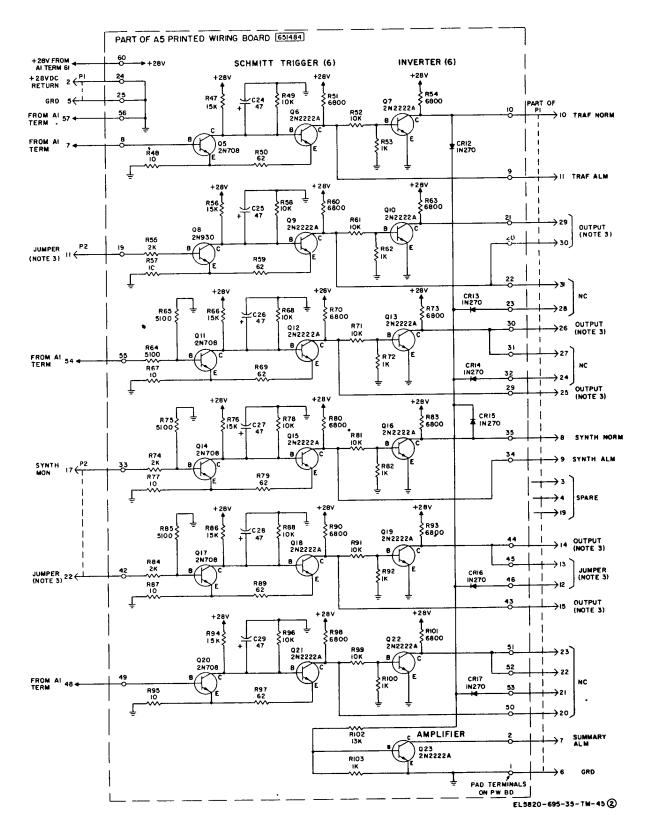

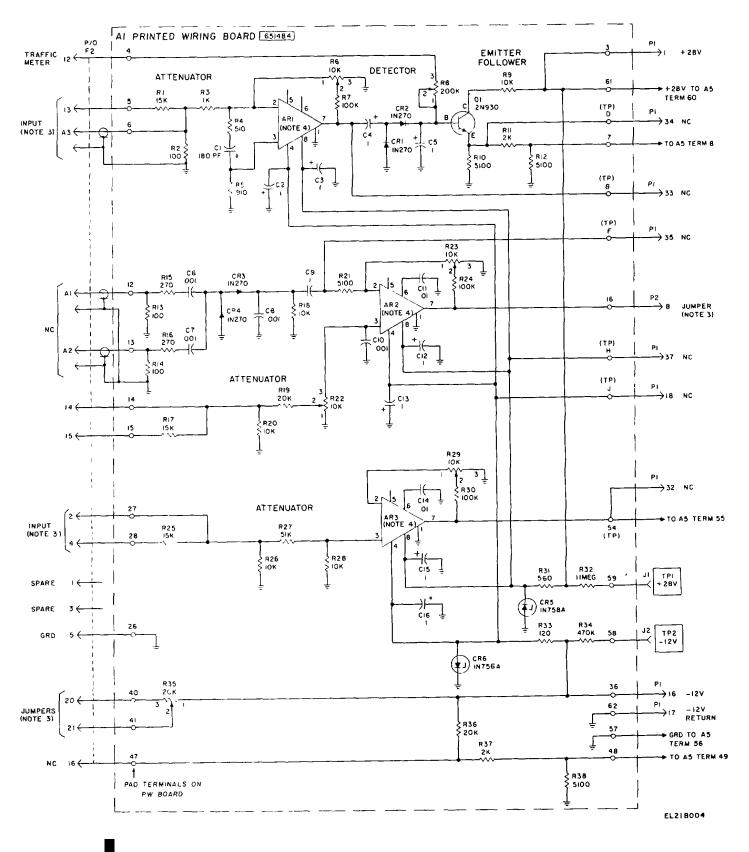

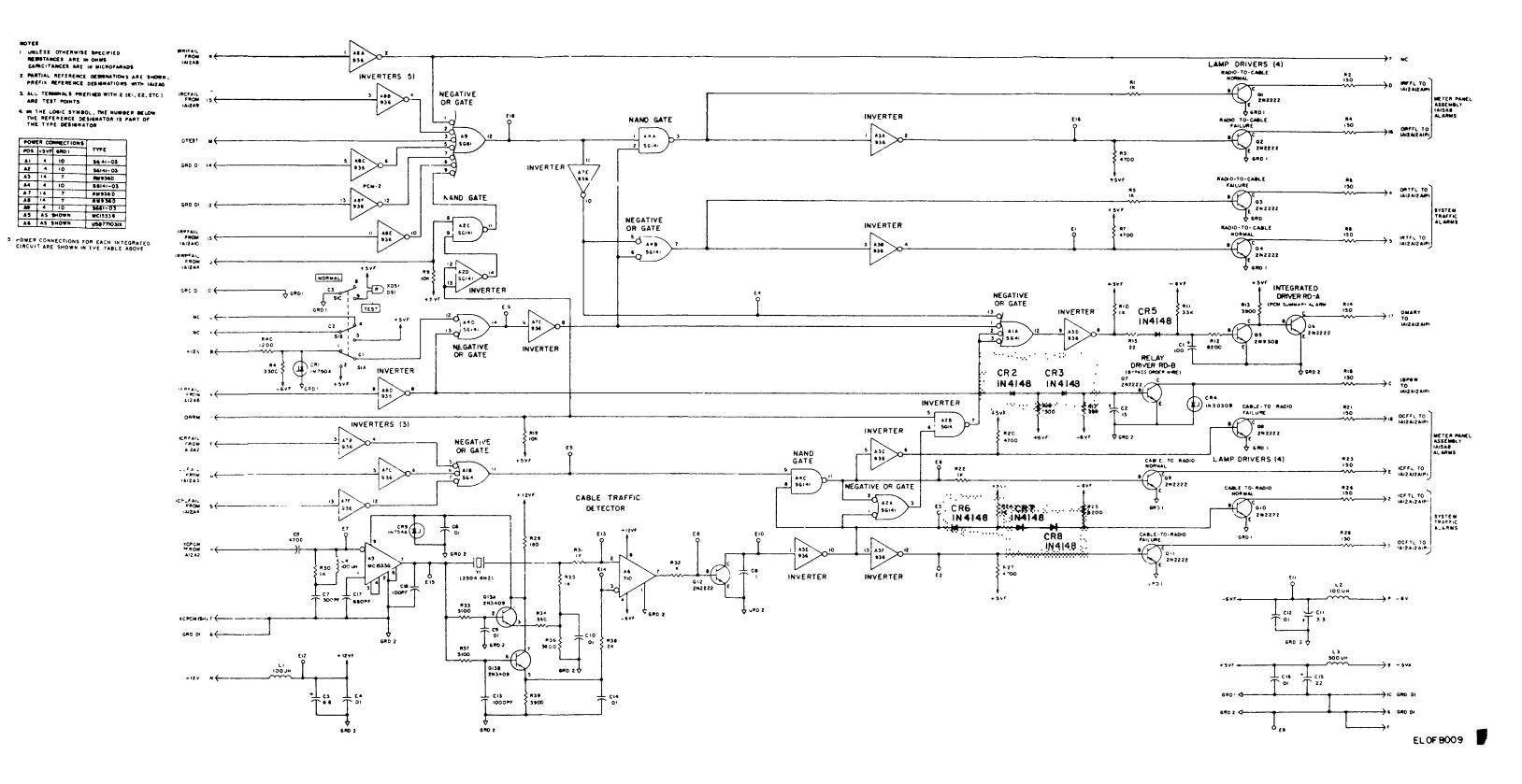

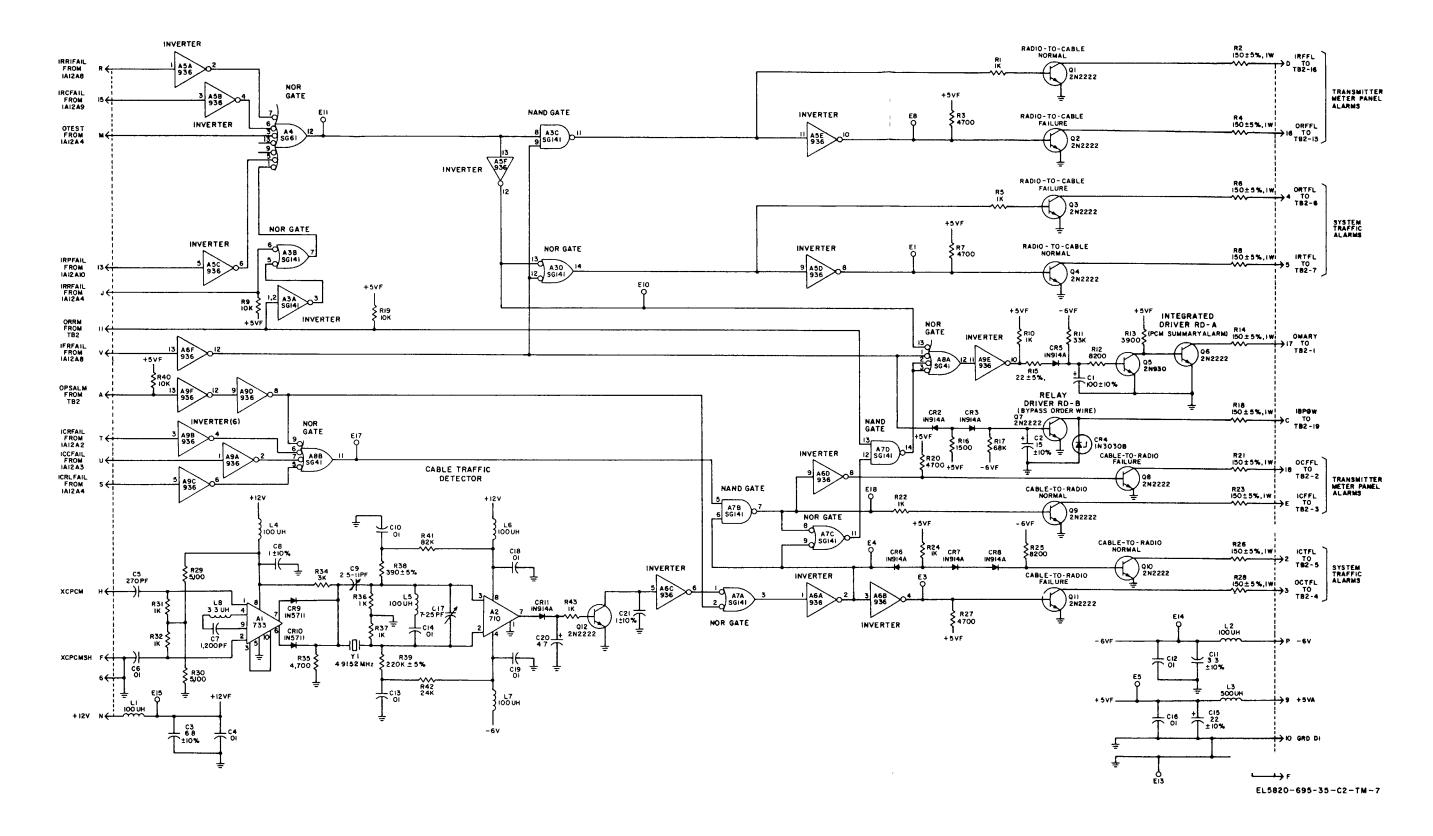

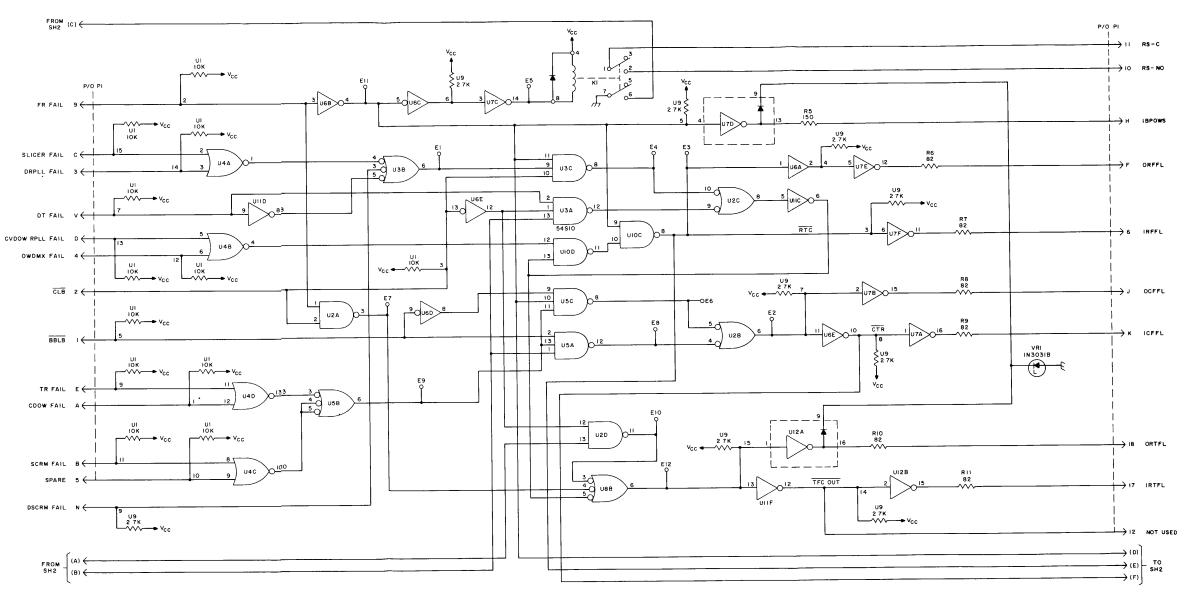

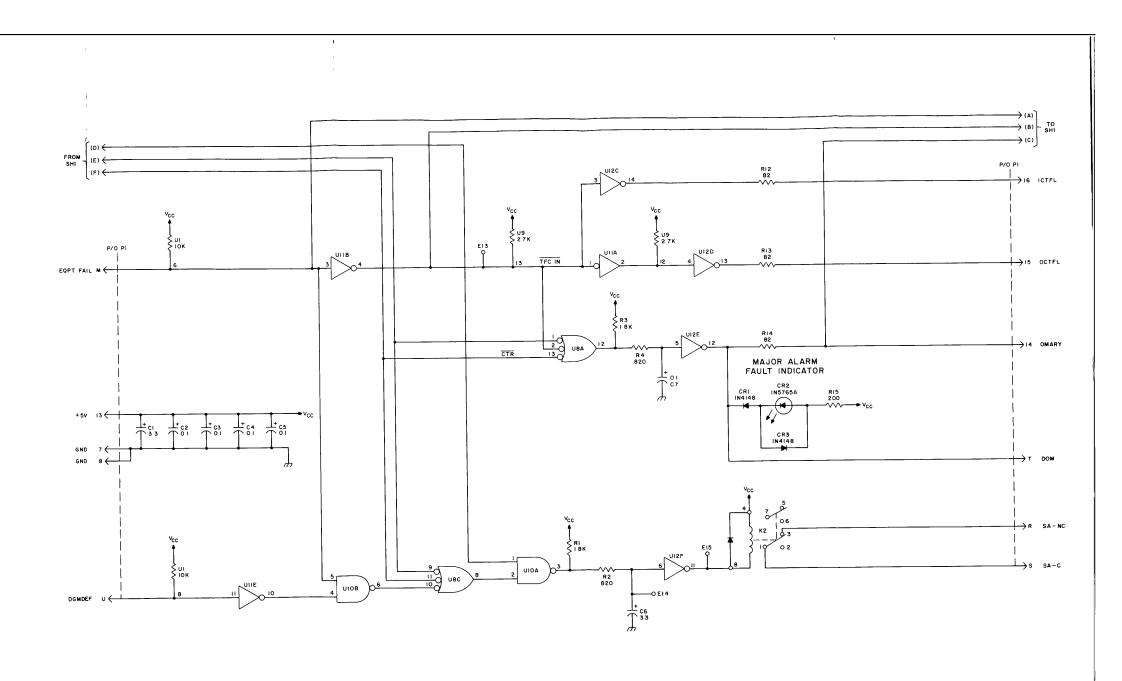

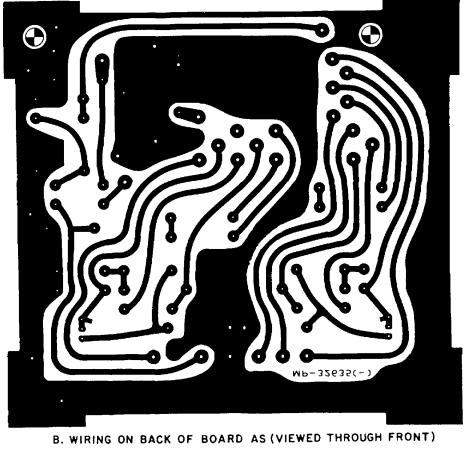

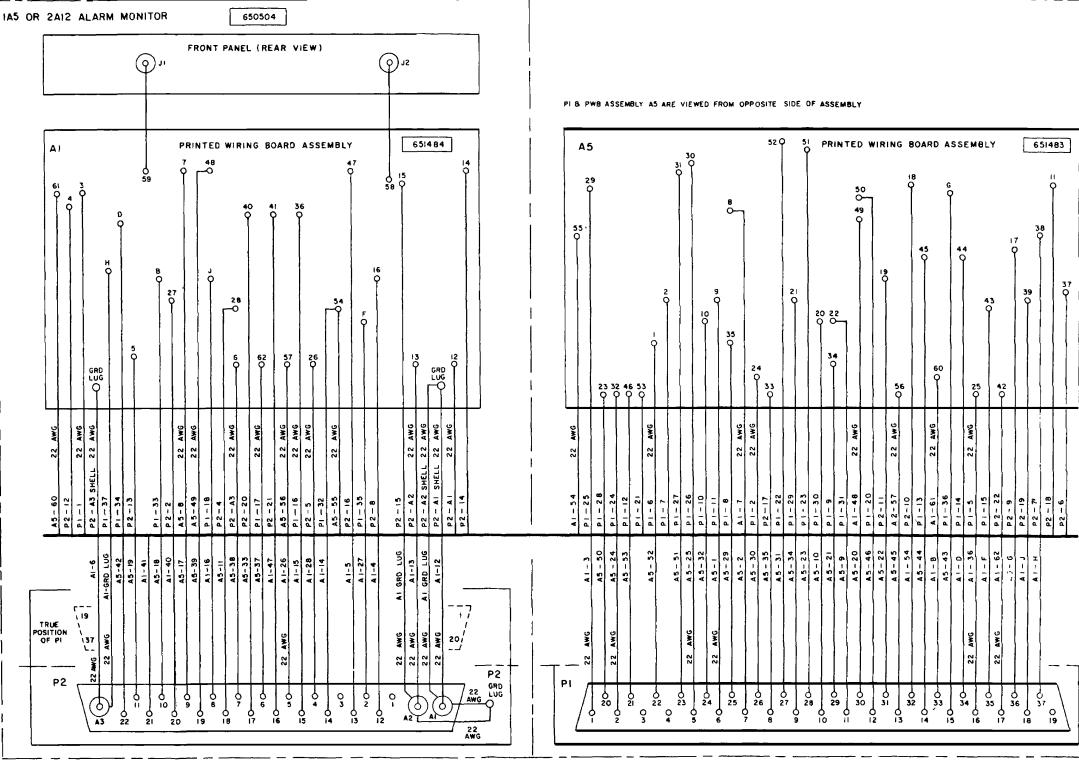

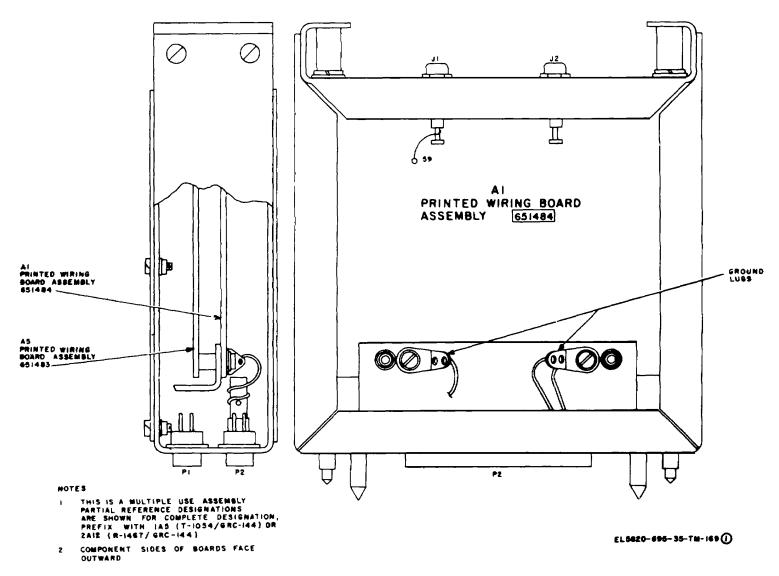

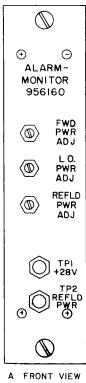

| 2-13<br>2-14(1)         | AF-RF Amplifier 1A4/2A11, schematic diagram<br>Alarm monitor 1A5/2A12, schematic diagram                                                    | 2-62.3           |

|                         | (Part 1 of 3)                                                                                                                               | 2-64             |

| 2-14(2)                 | Alarm monitor 1A5/2A12, schematic diagram<br>(Part 2 of 3)                                                                                  | 2-65             |

| 2-14(3)                 | Alarm monitor 1A5/2A12, schematic diagram                                                                                                   |                  |

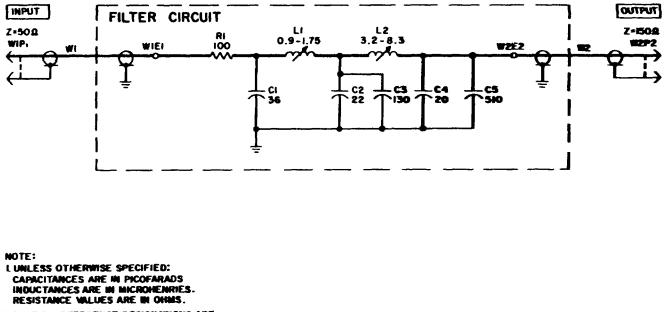

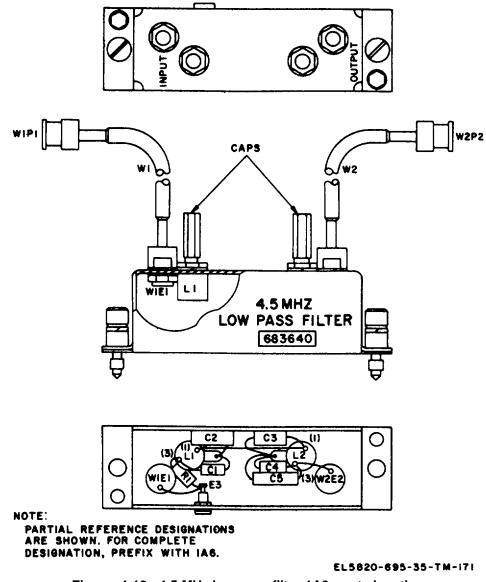

| 2-15                    | (Part 3 of 3)<br>4.5 MHz low pass filter 1A6, schematic diagram                                                                             | 2-67<br>2-69     |

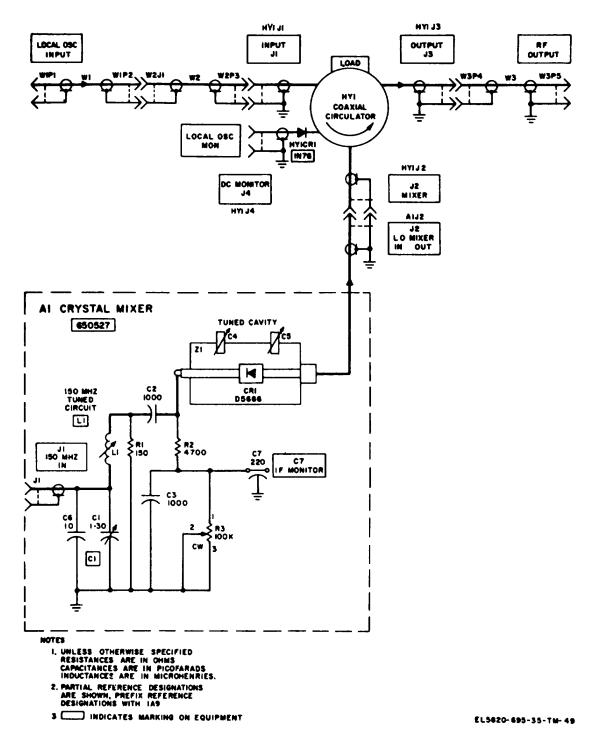

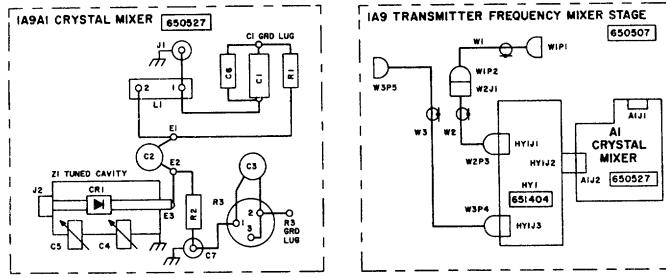

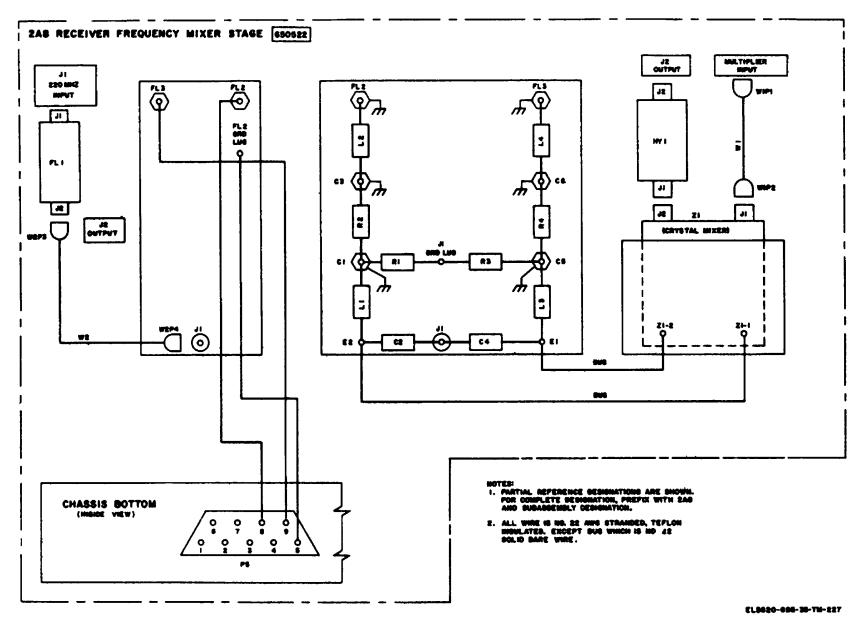

| 2-16                    | Transmitter frequency mixer stage 1A9, schematic                                                                                            |                  |

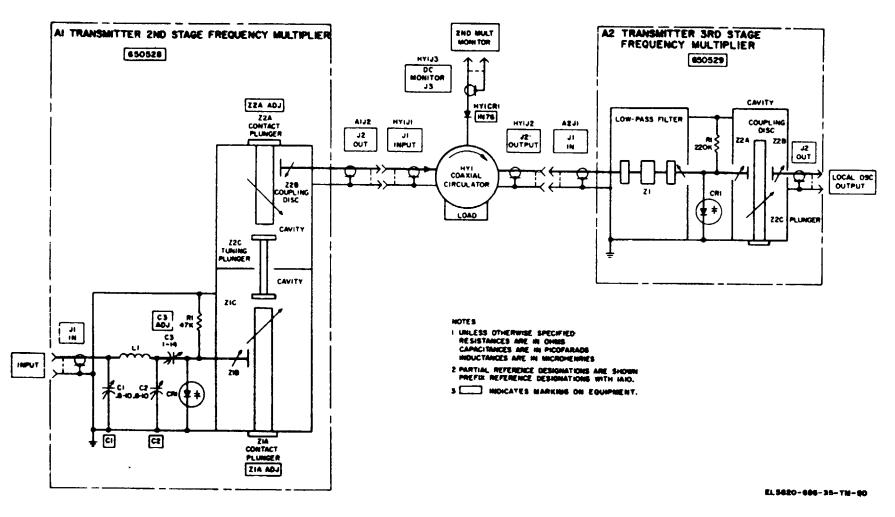

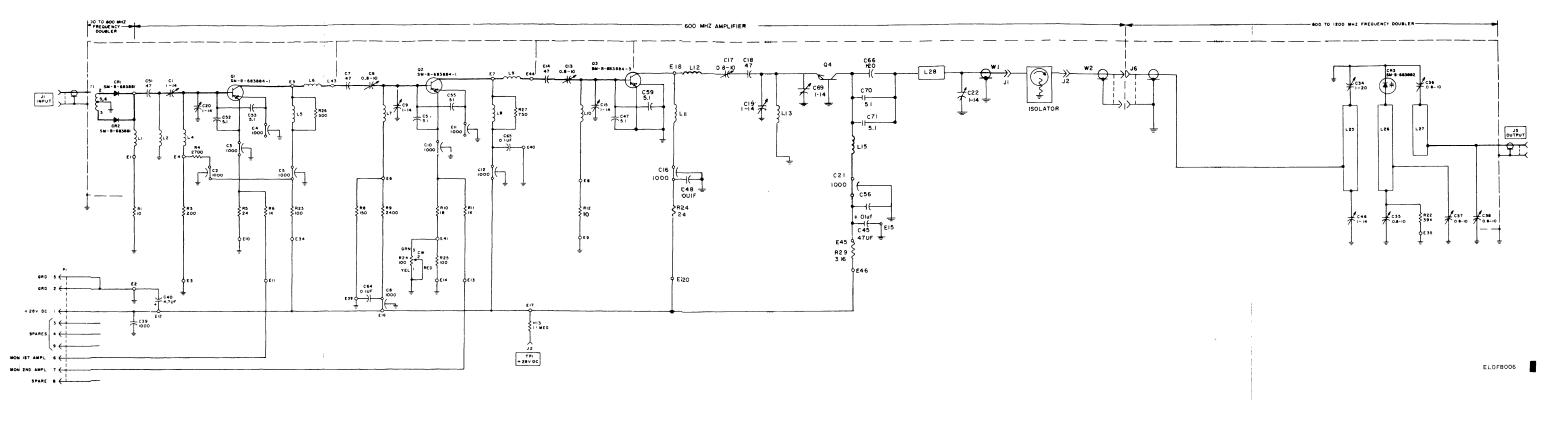

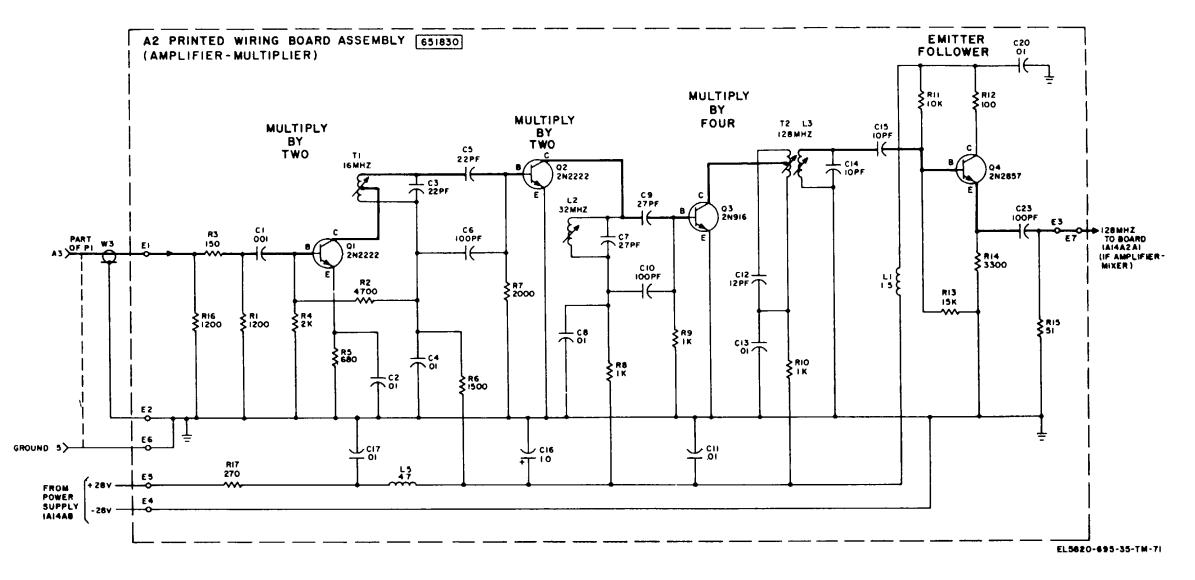

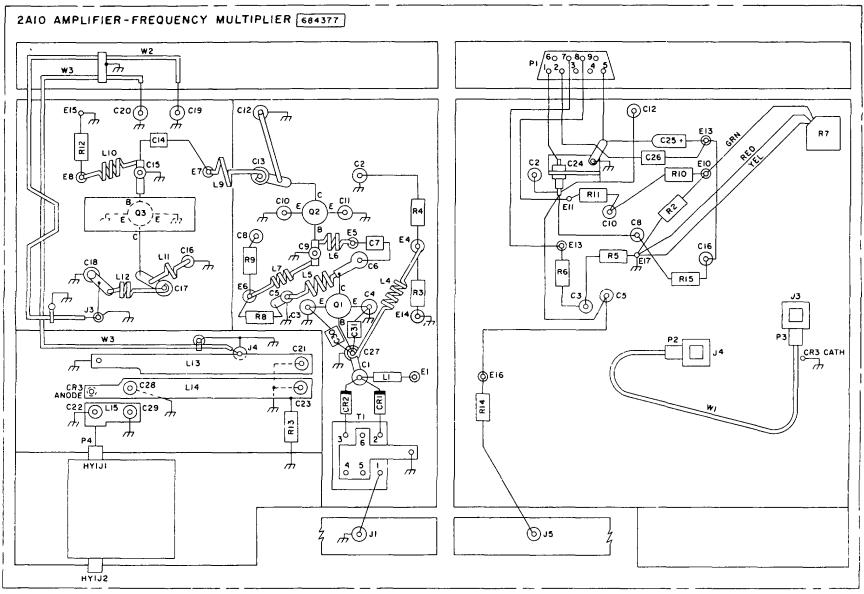

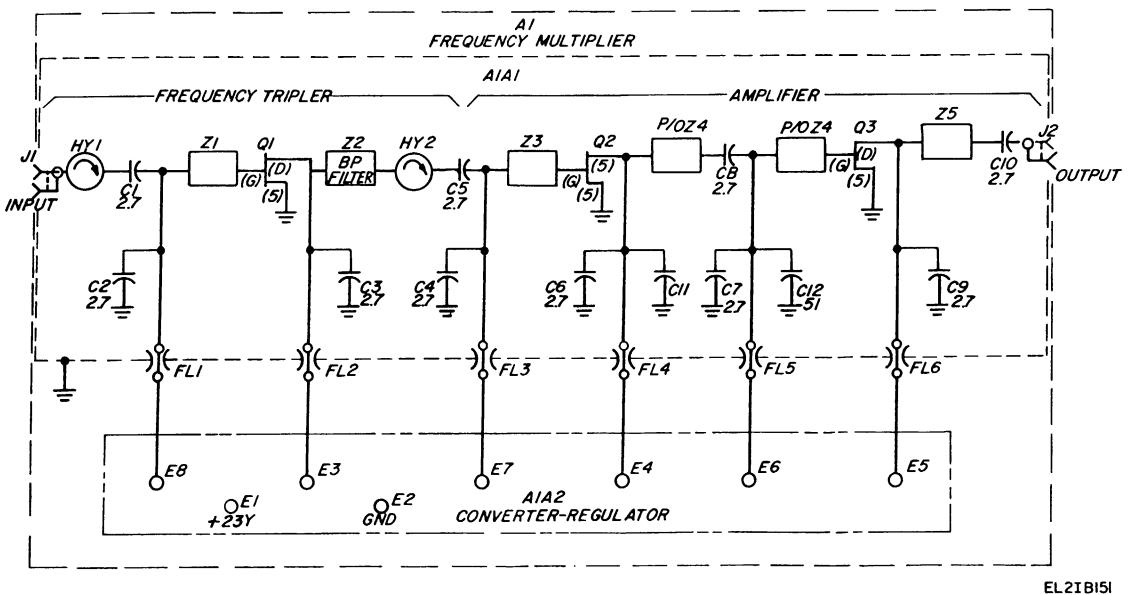

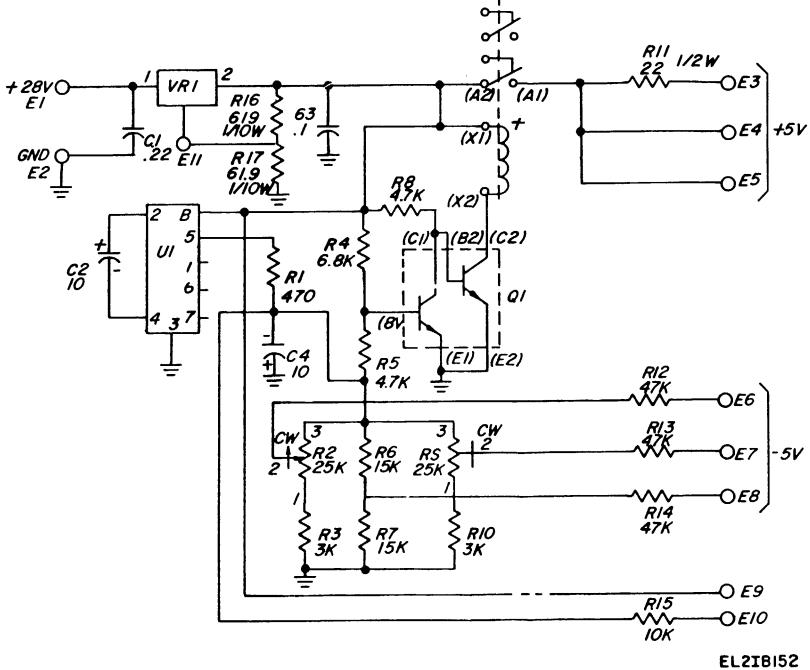

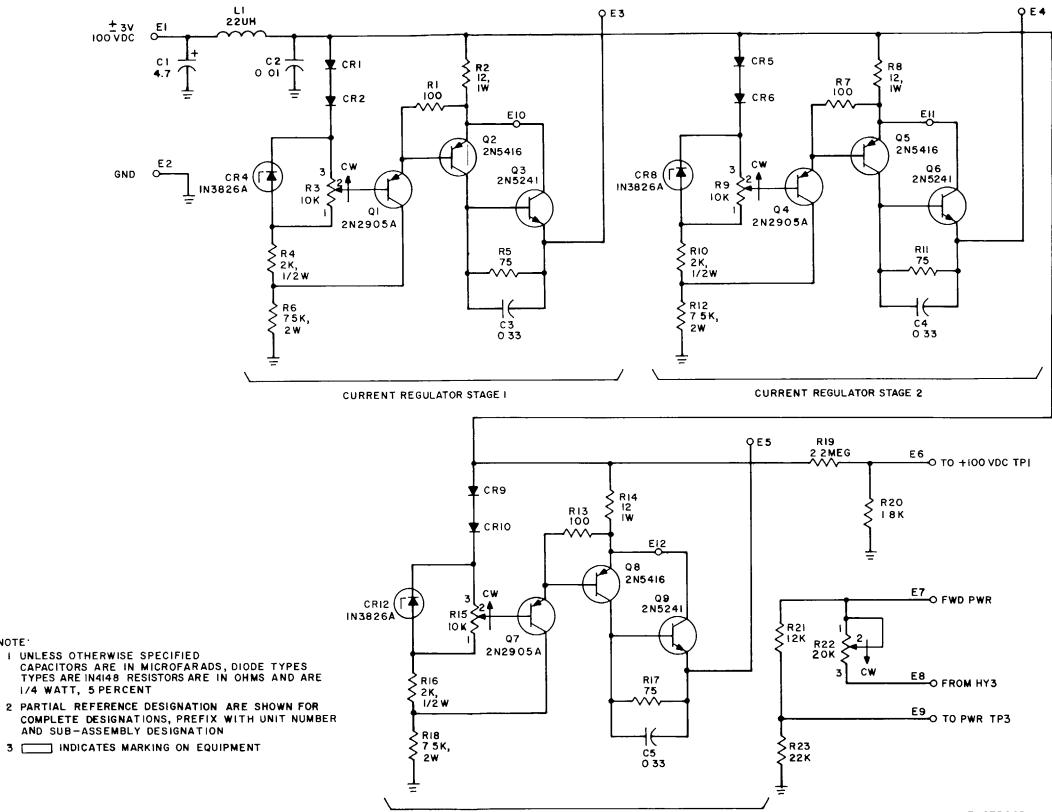

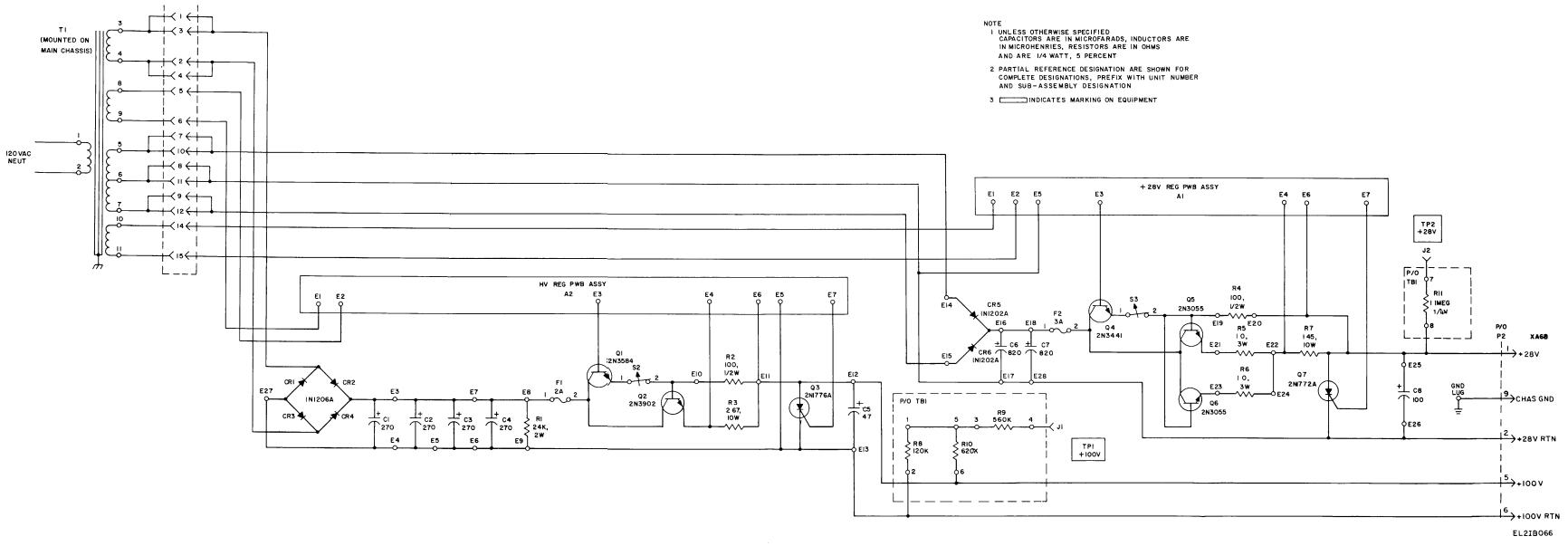

| 2-17                    | diagram<br>Transmitter frequency multiplier group 1A10,<br>schematic diagram                                                                | 2-75<br>2-77     |

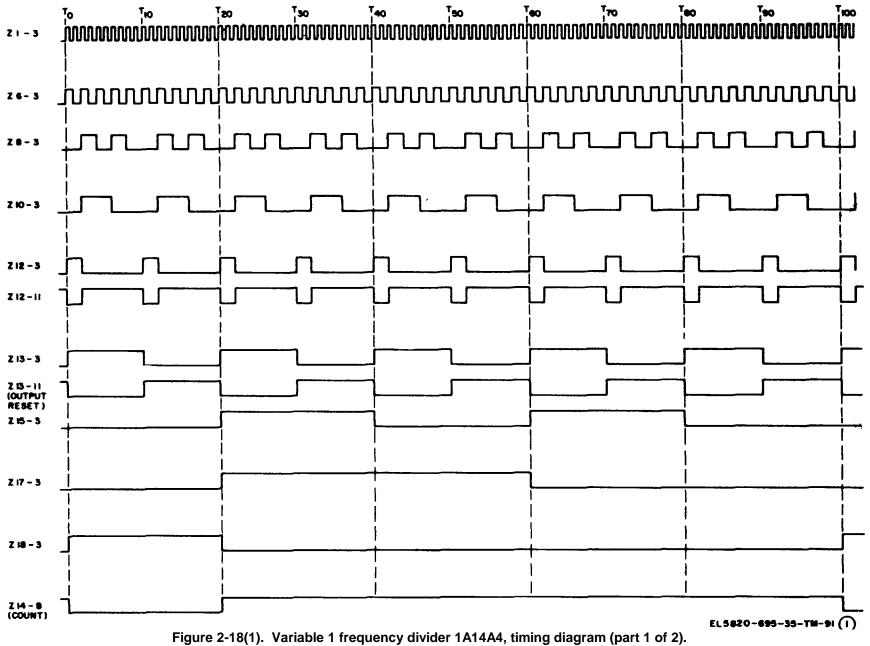

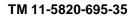

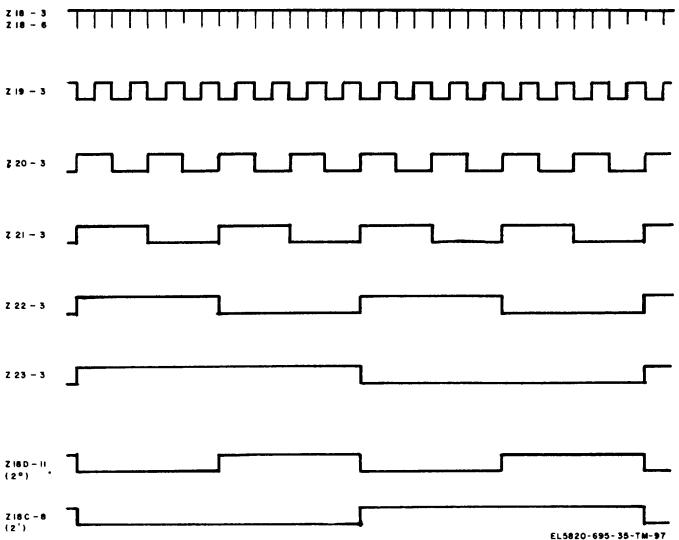

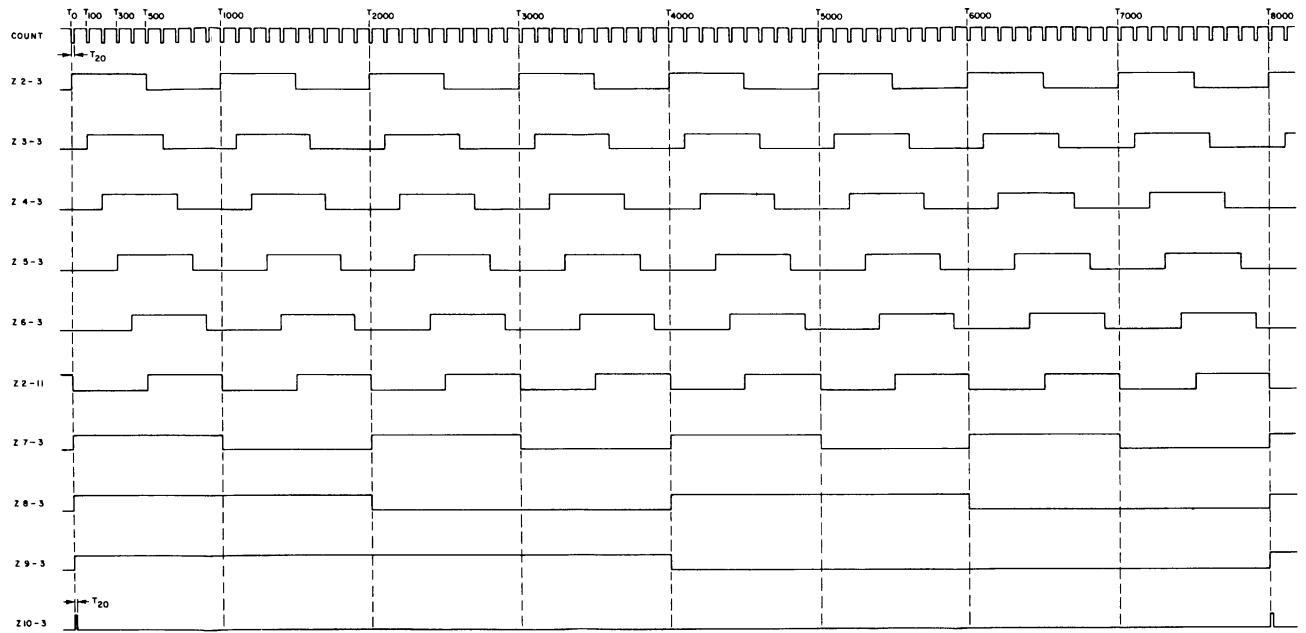

| 2-18(1)                 | Variable 1 frequency divider 1A14A4, timing diagram                                                                                         |                  |

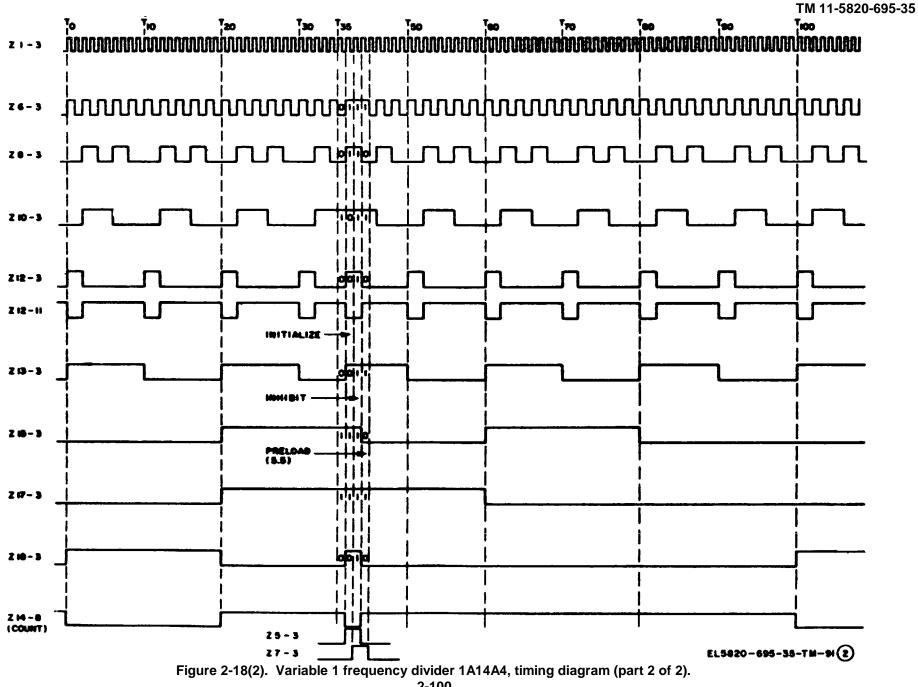

| 2-18(2)                 | (Part 1 of 2)<br>Variable 1 frequency divider 1A14A4, timing diagram                                                                        | 2-99             |

|                         | (Part 2 of 2)                                                                                                                               | 2-100            |

Change 6 ii

| Figure<br><u>Number</u> | Title                                                                                              | <u>Page</u> |

|-------------------------|----------------------------------------------------------------------------------------------------|-------------|

|                         |                                                                                                    |             |

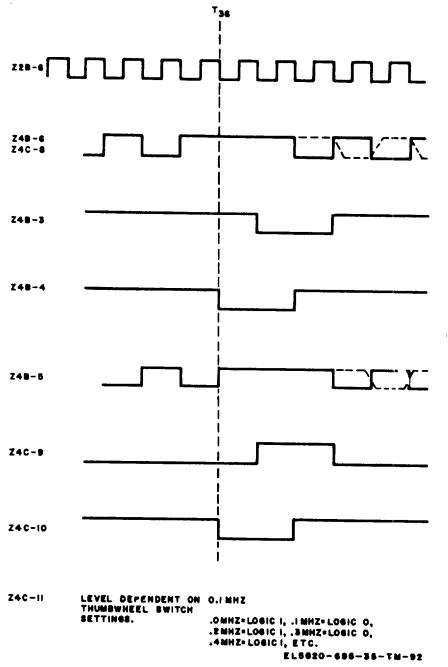

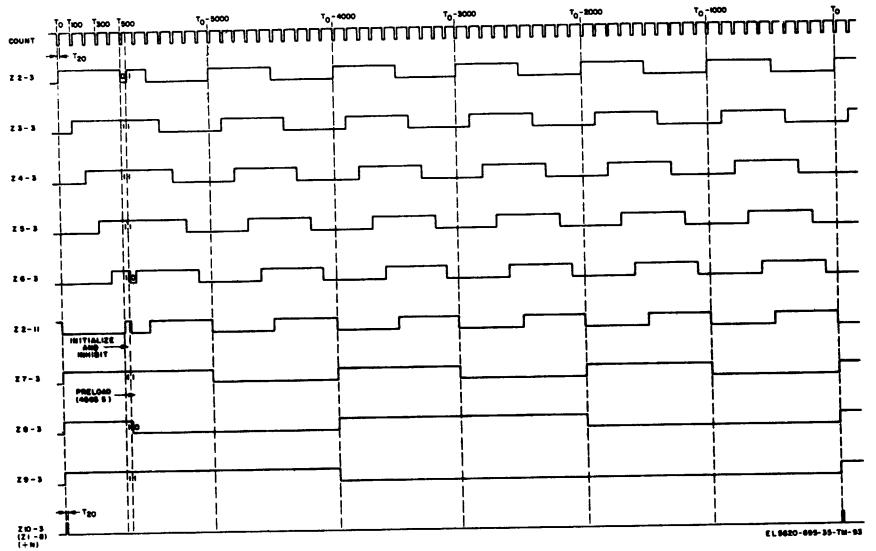

| 2-19<br>2-20            | 1A14 timing diagram, 0.1 MHz thumbwheel switch<br>Variable 2 frequency divider 1A14A5, timing with | 2-102       |

|                         | jump count                                                                                         | 2-105       |

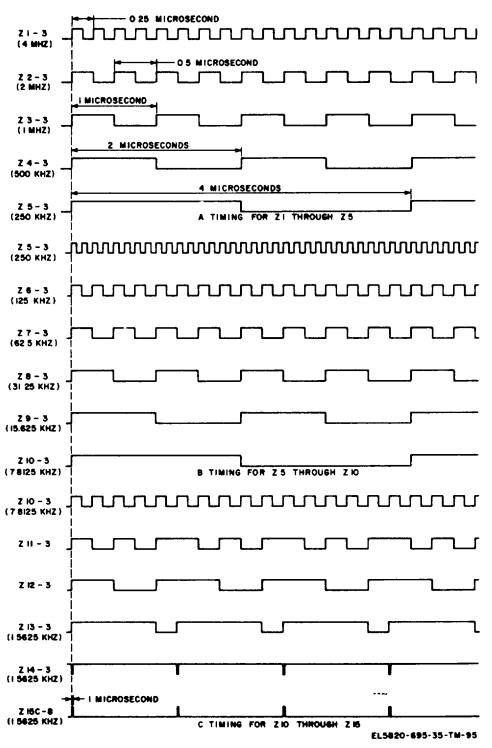

| 2-21<br>2-22            | Fixed frequency divider 1A14A6, timing diagram<br>Fixed frequency divider 1A14A6, phase detector,  | 2-107       |

| 2-23                    | timing diagram<br>Fixed frequency divider 1A14A6, phase detector,                                  | 2-108       |

|                         | timing diagram with phase loop unlocked                                                            | 2-109       |

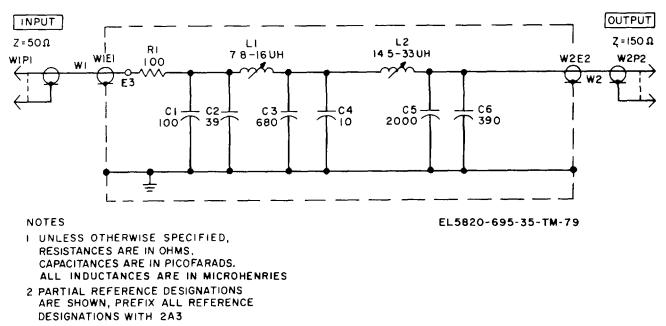

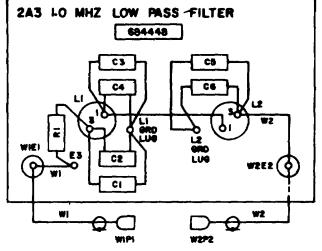

| 2-24                    | 1.0 MHz low pass filter 2A3, schematic diagram                                                     | 2-110.1     |

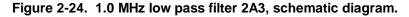

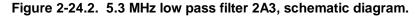

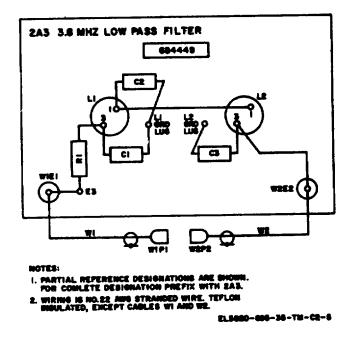

| 2-24.1                  | 3.8 MHz low pass filter 2A3, schematic diagram                                                     | 2-110.1     |

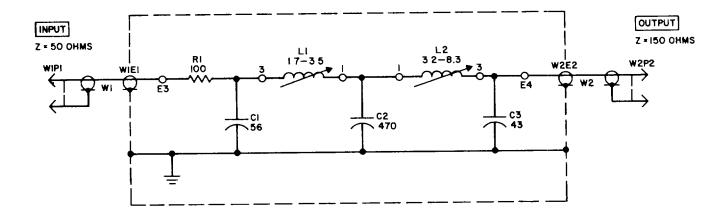

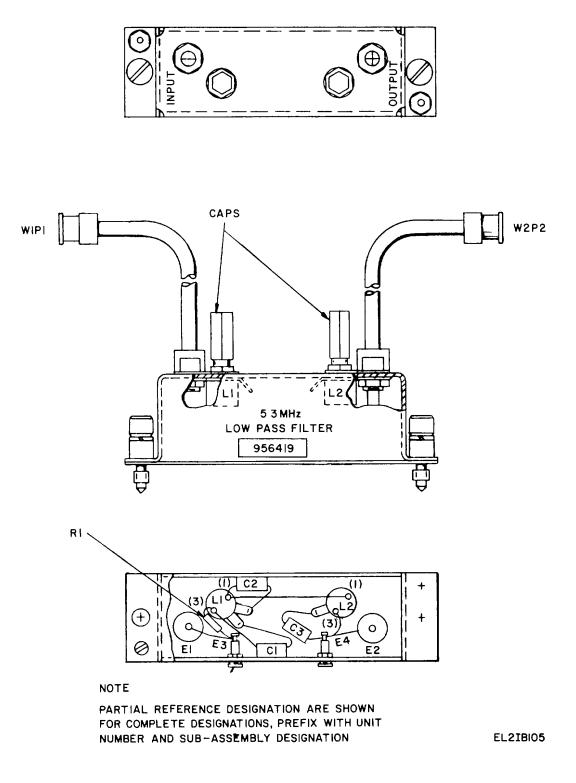

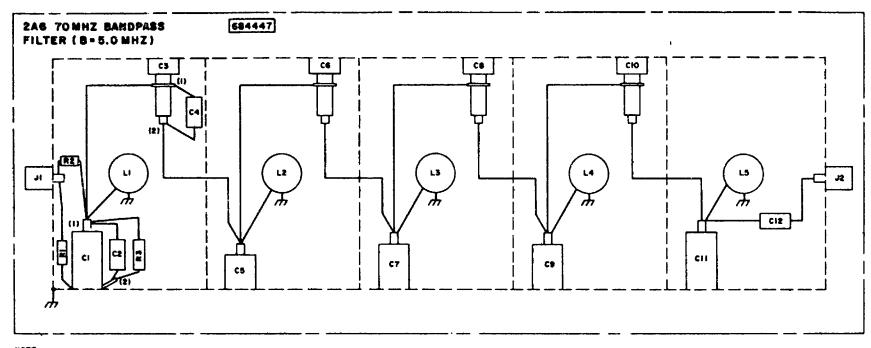

| 2-24.2                  | 5.3 MHz low pass filter 2A3, schematic diagram                                                     | 2-110.2     |

| 2-24.3                  | 13 MHz low pass filter 2A3, schematic diagram                                                      | 2-110.2     |

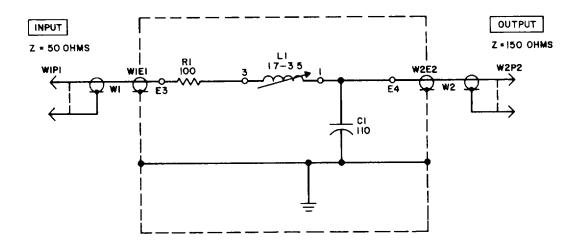

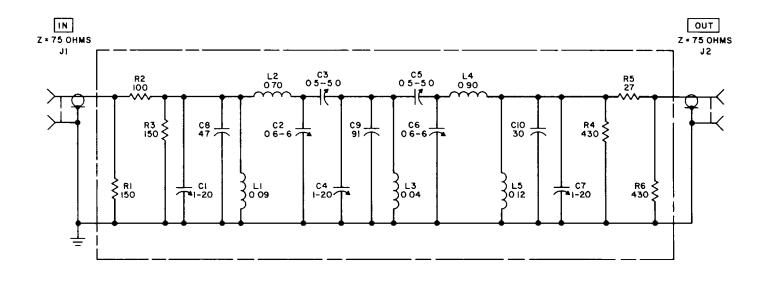

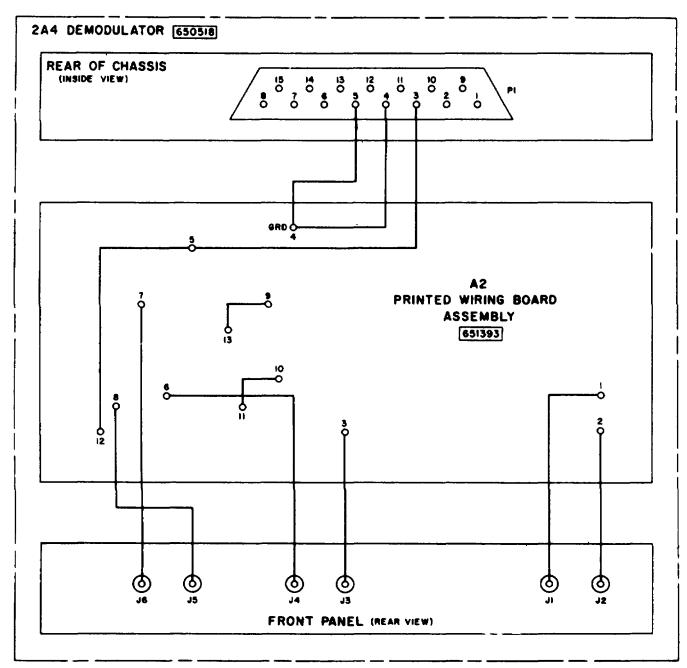

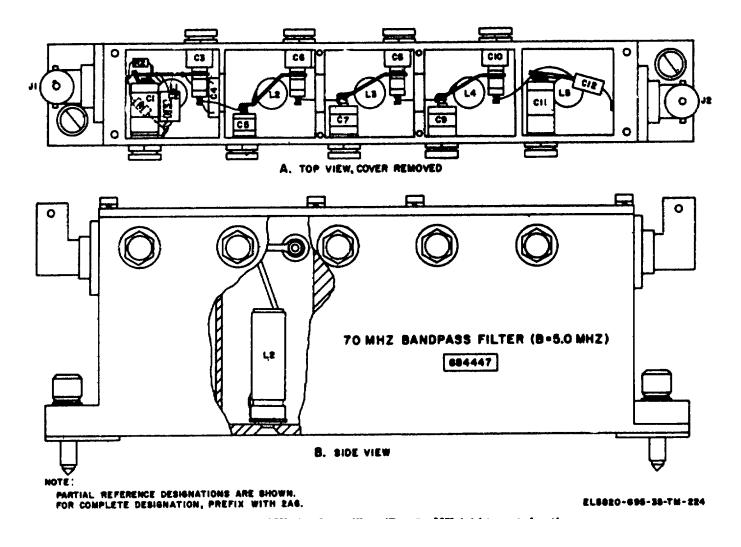

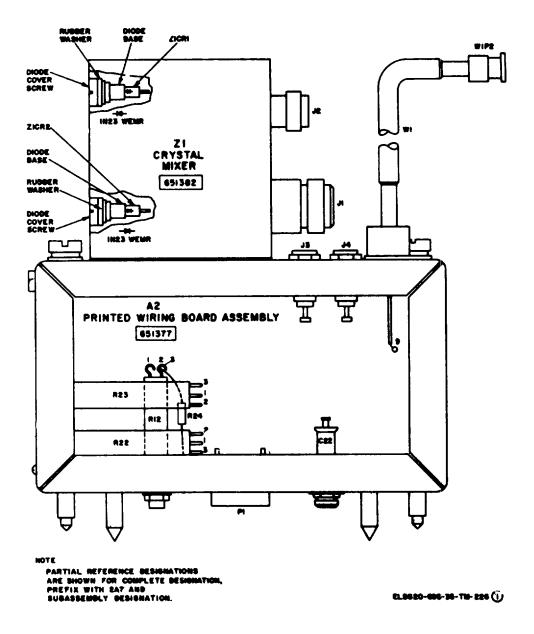

| 2-25                    | 70 MHz band pass filter (B=5.0) 2A6, (684447),<br>schematic diagram                                | 2-114       |

| 2-25.1                  | 70 MHz band pass filter (B=10.6) 2A6 (956417),                                                     | 2 114       |

| 2 20.1                  | schematic diagram                                                                                  | 2-114.1     |

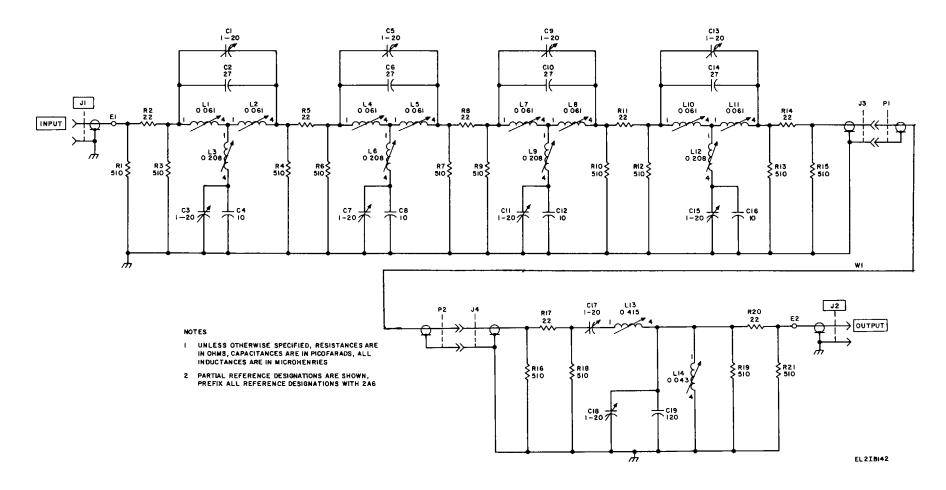

| 2-25.2                  | Equalizer filter 2A6 (956462), schematic diagram                                                   | 2-114.2     |

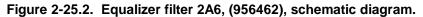

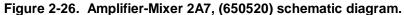

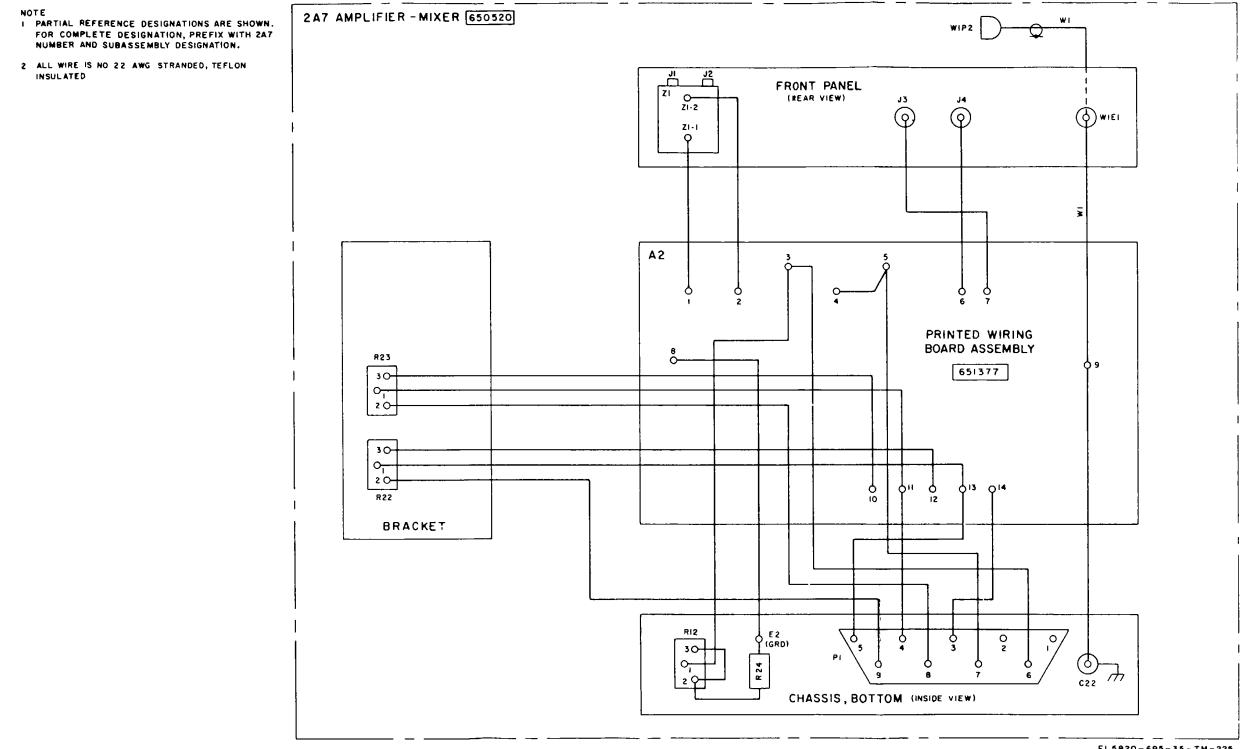

| 2-26                    | Amplifier-mixer 2A7 (650520), schematic diagram                                                    | 2-115       |

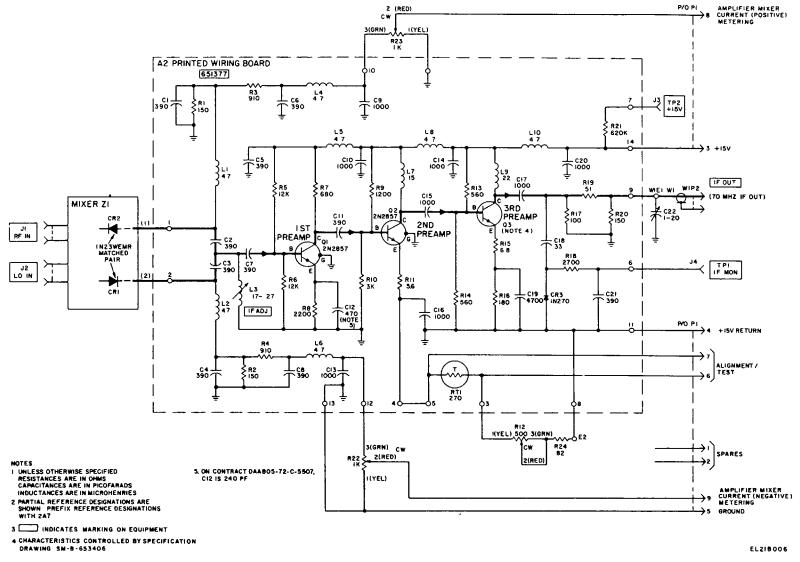

| 2-26.1                  | Amplifier-mixer 2A7 (956425), schematic diagram                                                    | 2-116.1     |

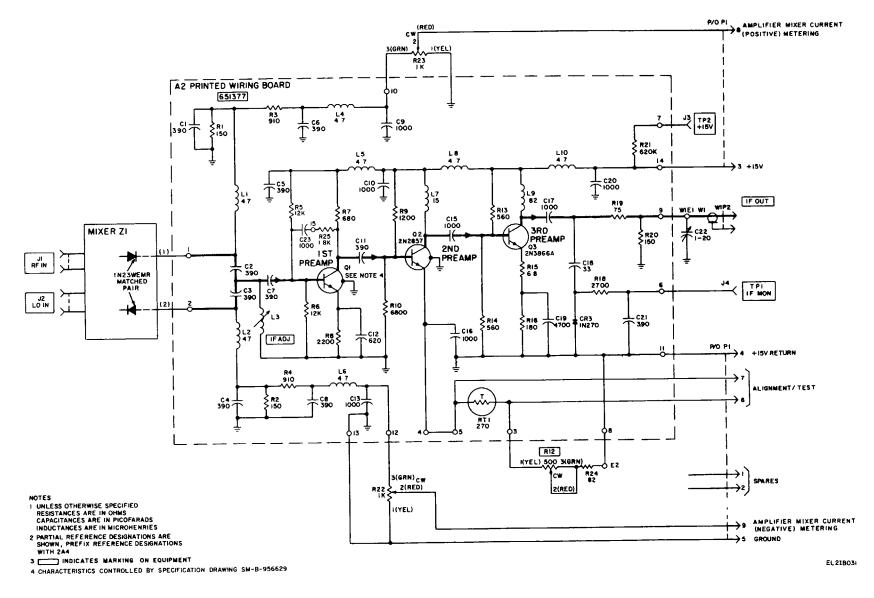

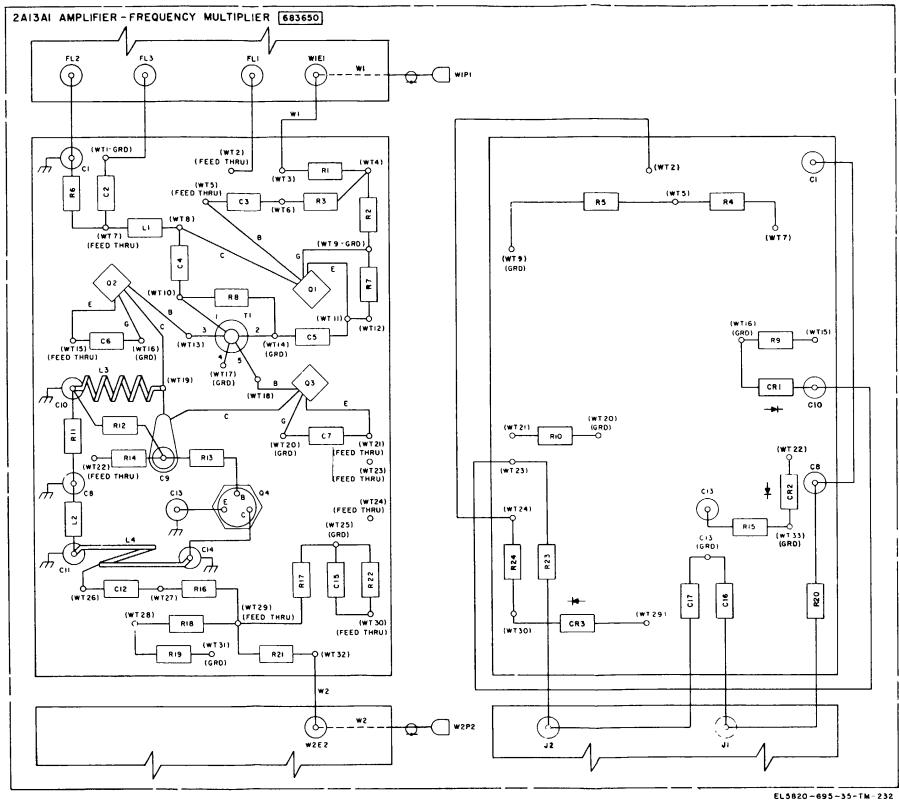

| 2-27                    | 110 MHz RF oscillator 2A13Y1, schematic diagram                                                    | 2-119       |

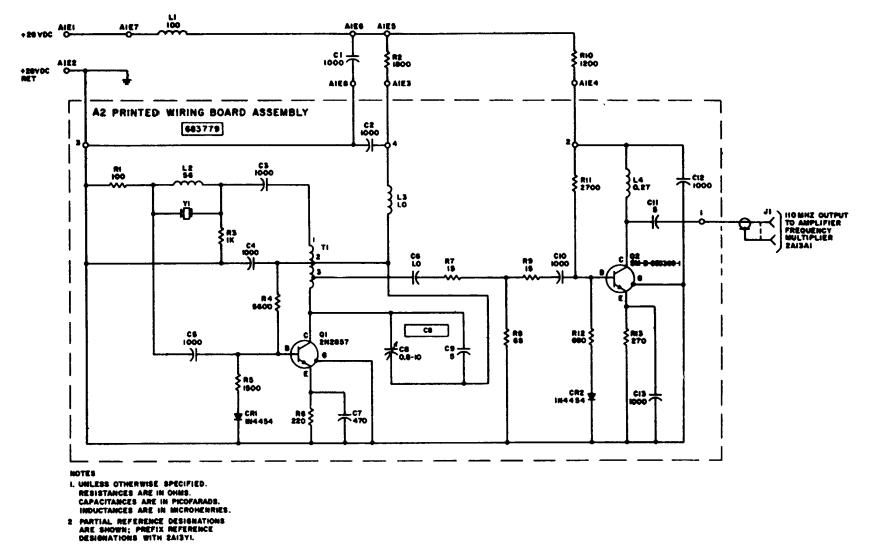

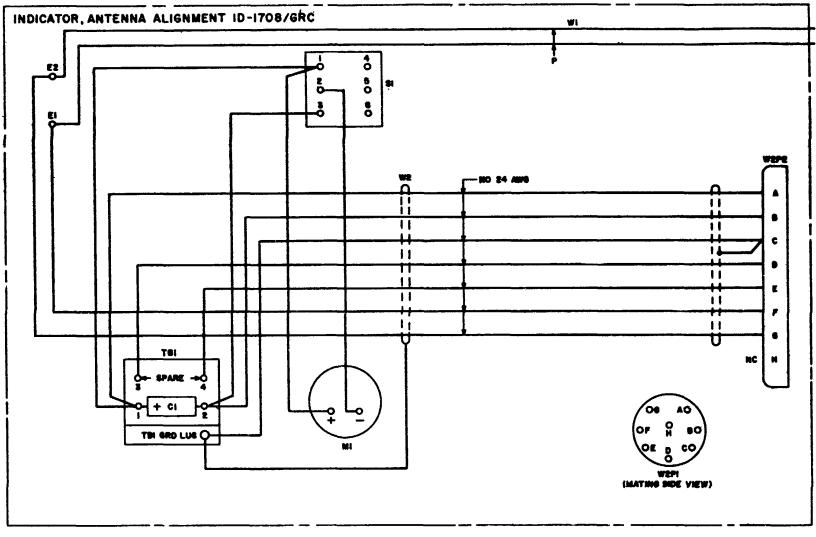

| 2-28                    | Indicator, Antenna Alignment ID-1708/GRC,                                                          |             |

| 0.00                    | schematic diagram                                                                                  | 2-120       |

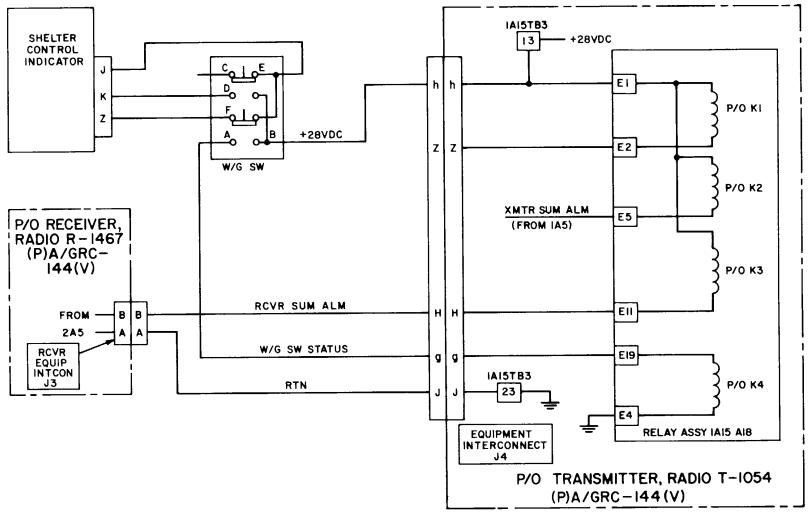

| 2-29                    | AN/GRC-144(V)3 waveguide switch position indicator                                                 | o 400 🌢     |

| 0.00                    | simplified schematic diagram                                                                       | 2-123       |

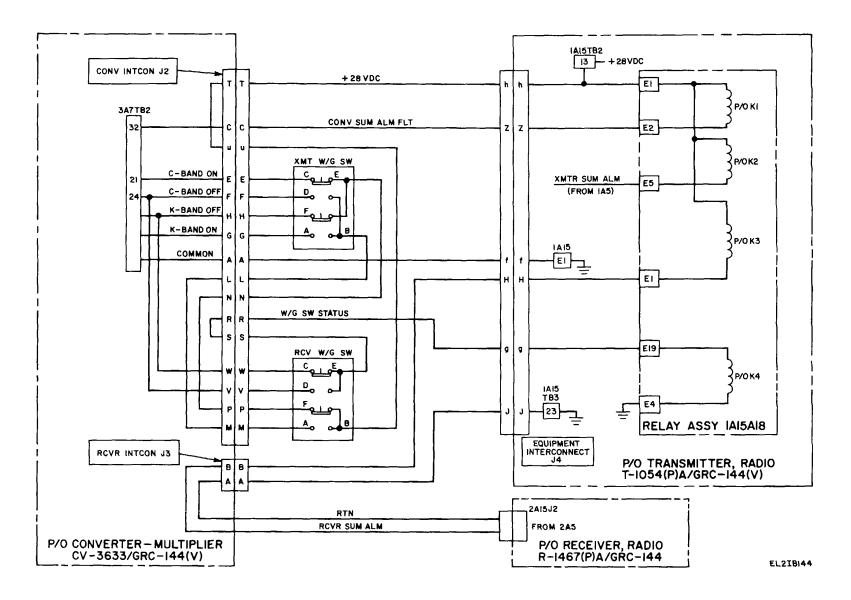

| 2-30                    | AN/GRC-144(V)4 waveguide switch position indicator                                                 | 2 1 2 4     |

| 2-31                    | simplified schematic diagram<br>AN/GRC-144(V)4 optional configuration waveguide                    | 2-124       |

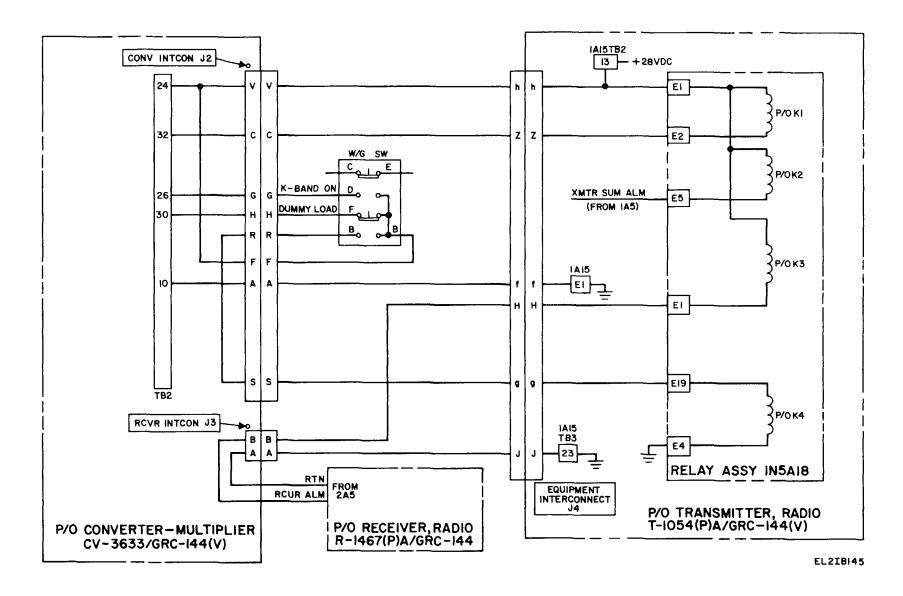

| 2-31                    | switch position indicator simplified schematic                                                     |             |

|                         | diagram                                                                                            | 2-125       |

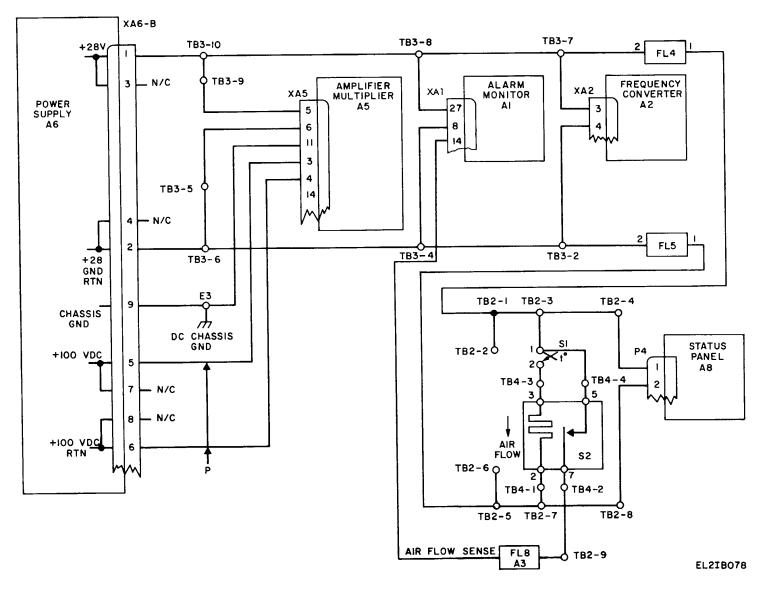

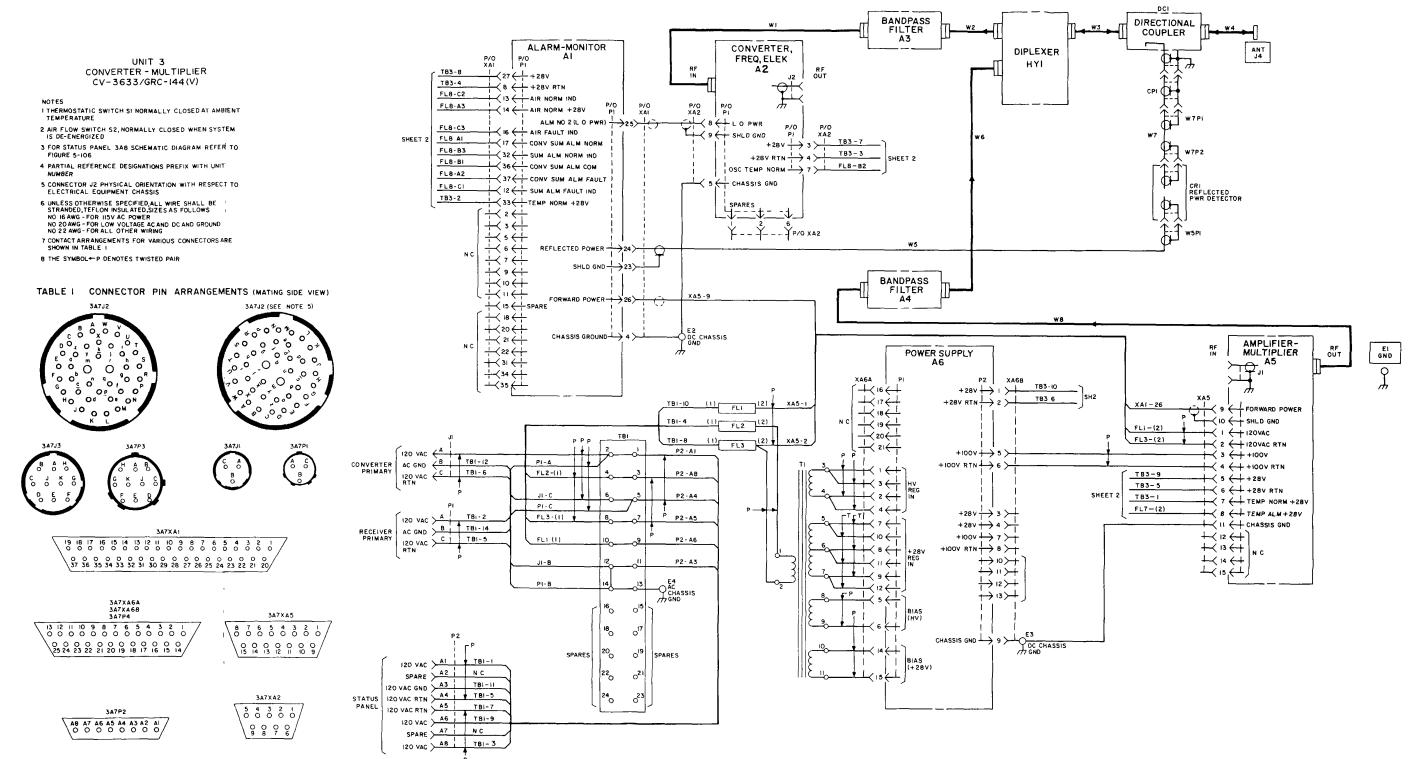

| 2-32                    | Converter-Multiplier CV-3633/GRC-144(V) primary                                                    | 2-125       |

| 2 02                    | power distribution                                                                                 | 2-128       |

| 2-33                    | Converter-Multiplier CV-3633/GRC-144(V) DC power                                                   | 2 120       |

| 2 00                    | distribution                                                                                       | 2-129       |

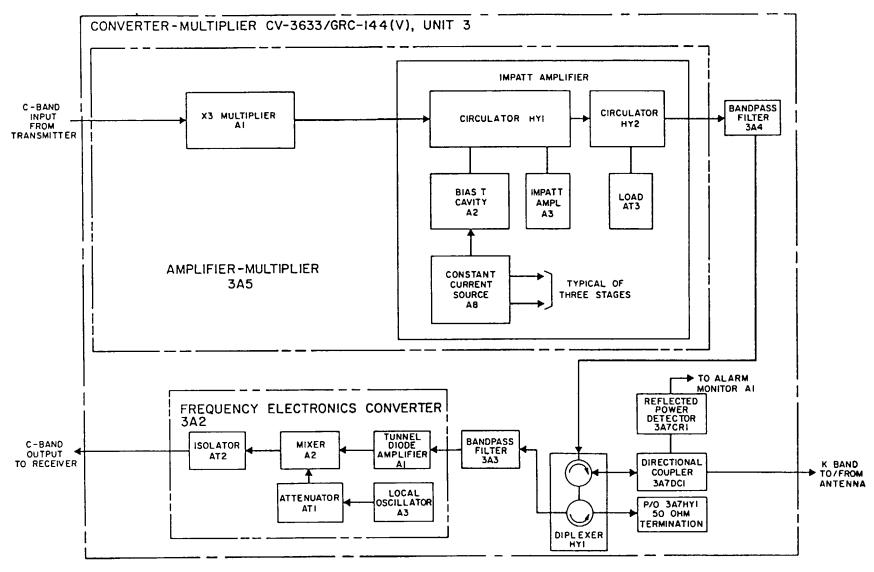

| 2-34                    | Converter-Multiplier CV-3633/GRC-144(V) functional                                                 |             |

|                         | block diagram                                                                                      | 2-131       |

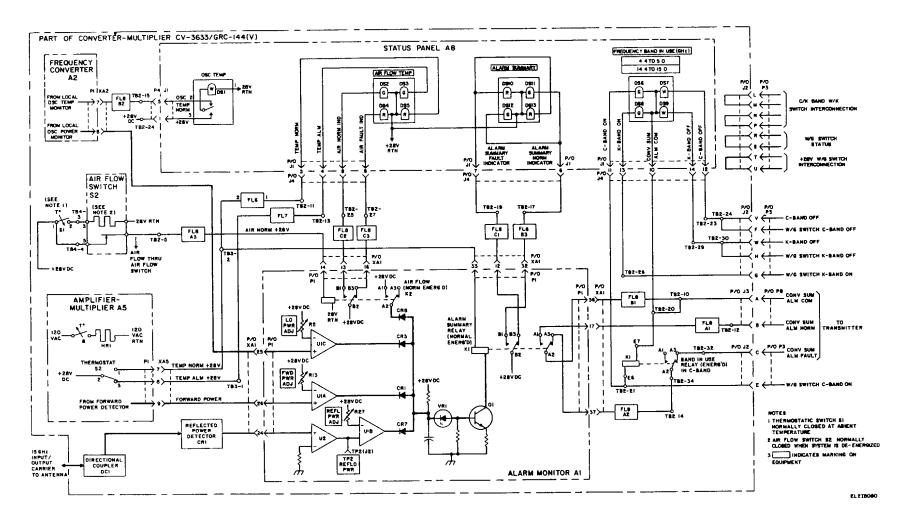

| 2-35                    | Converter-Multiplier CV-3633/GRC-144(V) alarm<br>circuit diagram                                   | 2-138       |

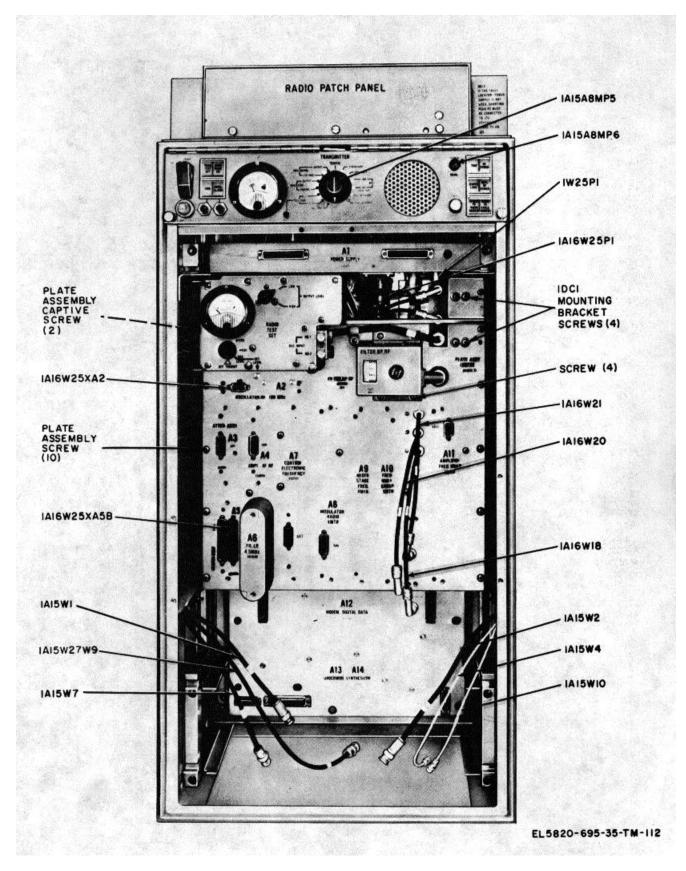

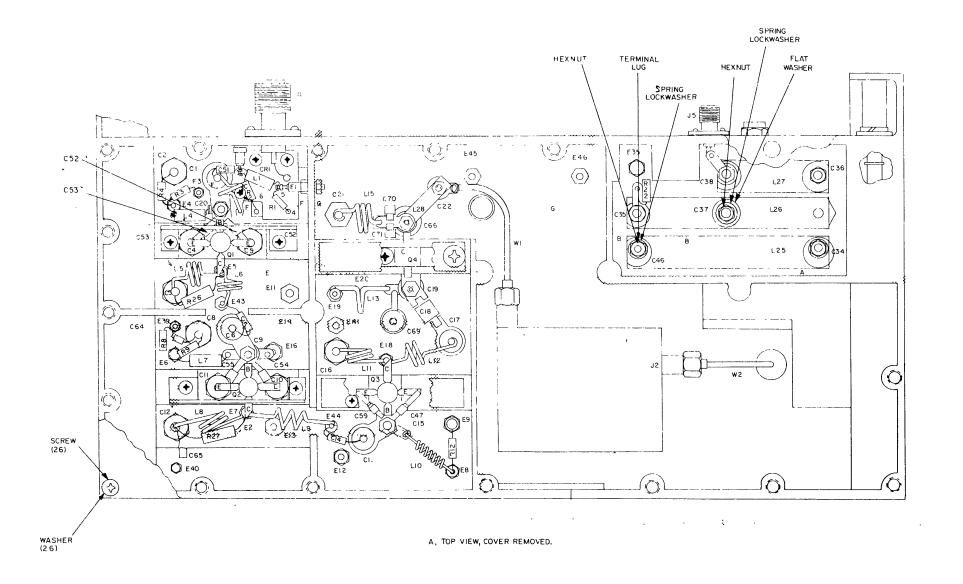

| 3-1                     | Transmitter, Radio T-1054(P)/GRC-144(V) and T-1054(P)A/                                            | 2 100       |

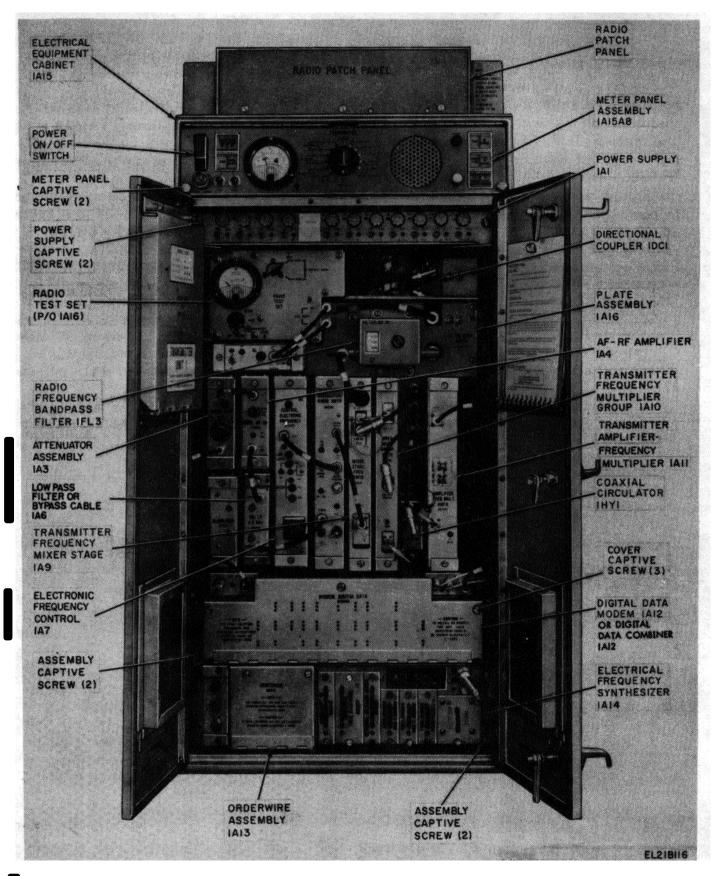

| 01                      | GRC-144(V), parts location                                                                         | 3-32        |

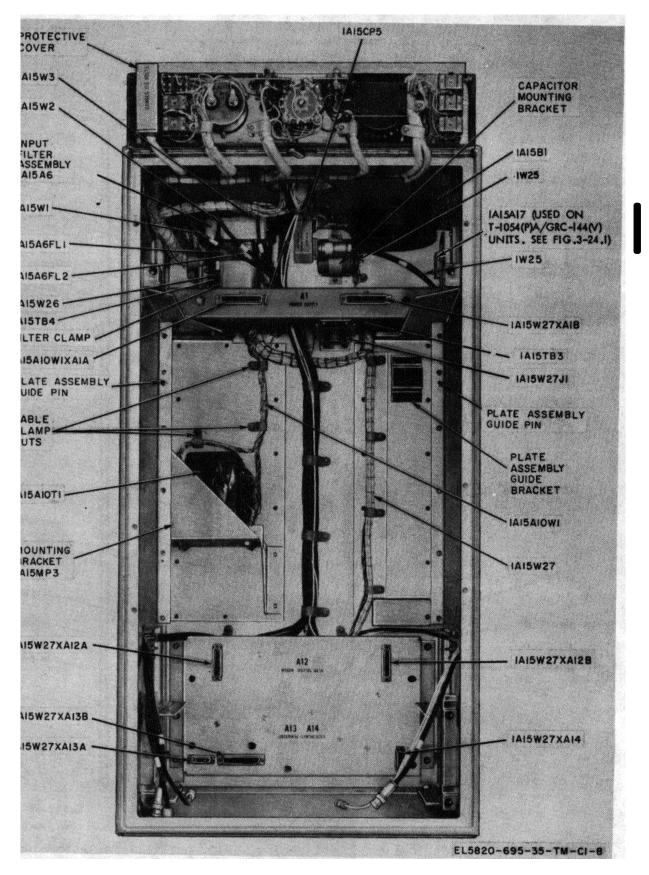

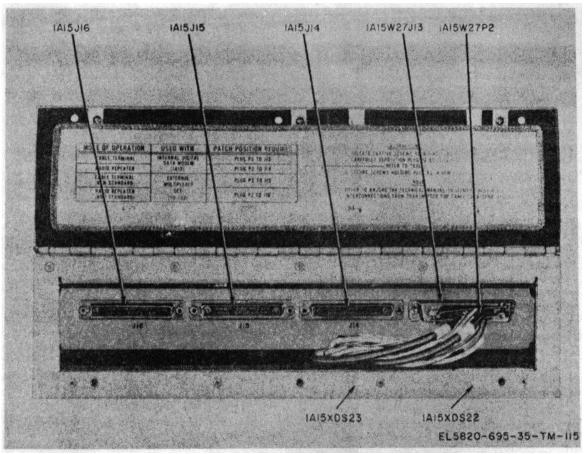

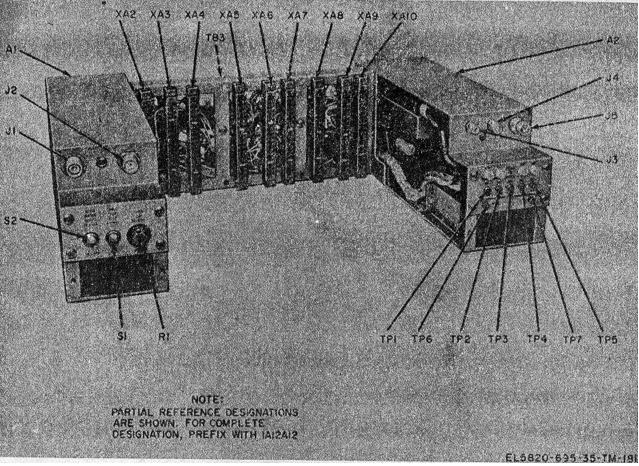

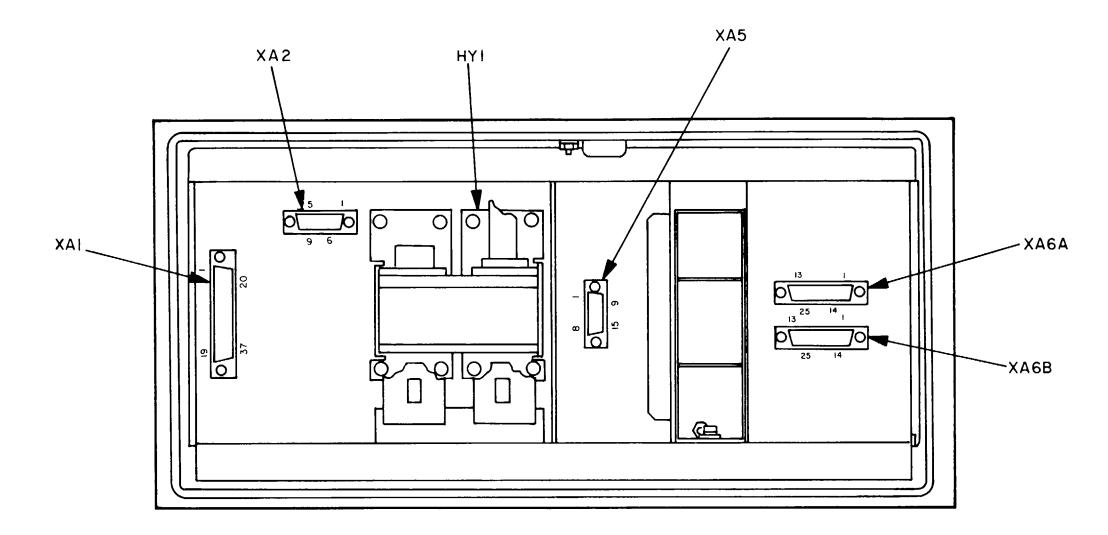

| 3-2                     | Electrical equipment cabinet 1A15, partially                                                       | • • • •     |

| -                       | disassembled, parts location                                                                       | 3-33        |

| 3-3                     | Electrical equipment cabinet 1A15, front view with                                                 |             |

|                         | plate assembly 1A16 removed, parts location                                                        | 3-34        |

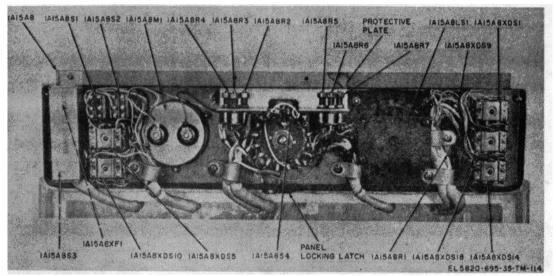

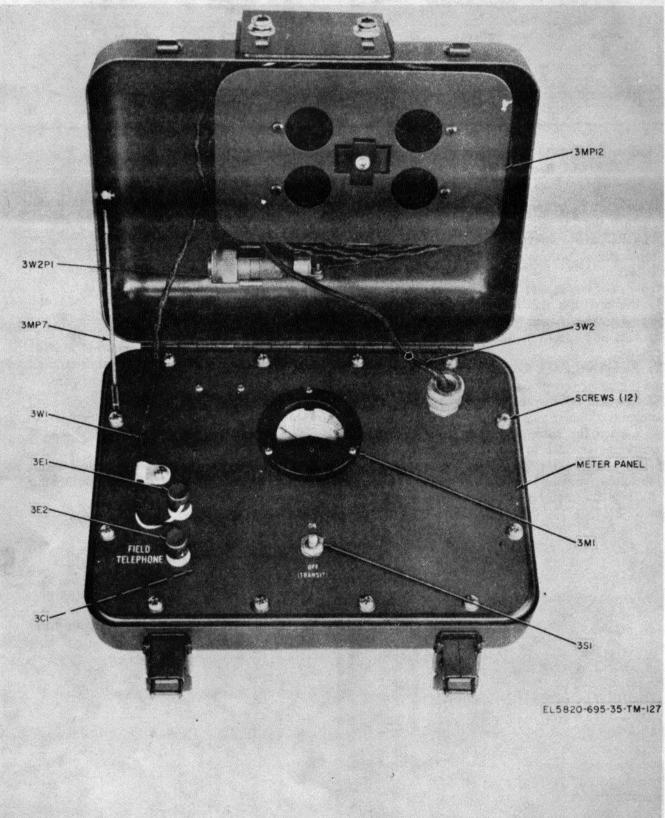

| 3-4                     | Meter panel assembly 1A15A8, rear view parts location                                              | 3-35        |

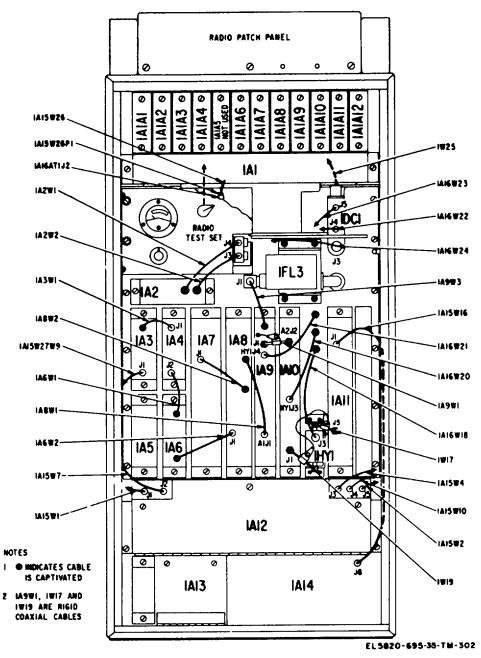

| 3-5                     | Radio patch panel (P/O 1A150) front interior view                                                  | 2.20        |

|                         | parts location                                                                                     | 3-36        |

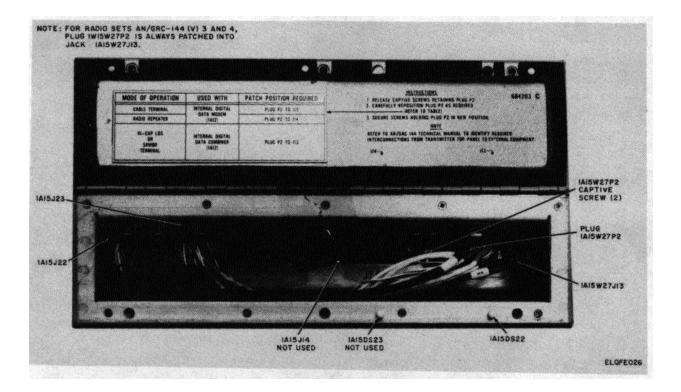

| 3-5.1                   | T-1054(P)A/GRC-144(V) radio patch panel (P/O 1A15),                                                | 2.20.4      |

| 3.6                     | front interior view, parts location                                                                | 3-36.1 ■    |

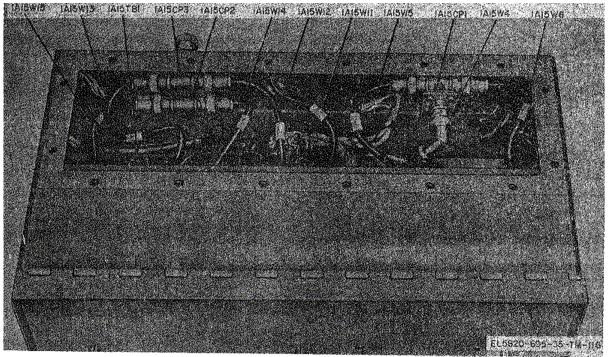

| 3-6                     | Radio patch panel (P/O 1A15) top interior view,<br>parts location                                  | 3-37        |

|                         |                                                                                                    | 5-57        |

| Figure<br><u>Number</u> | Title                                                                      | Page   |

|-------------------------|----------------------------------------------------------------------------|--------|

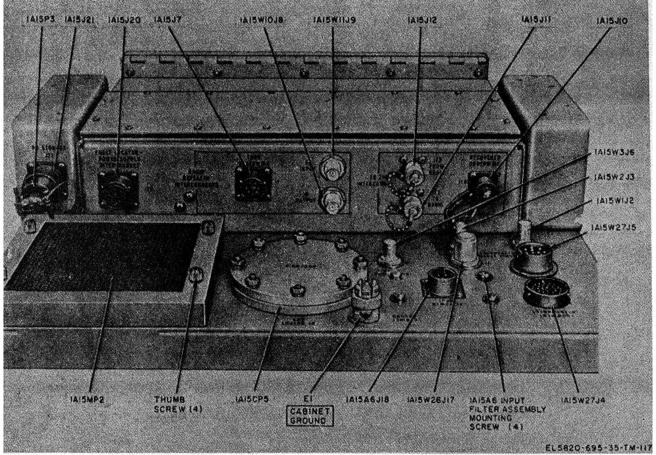

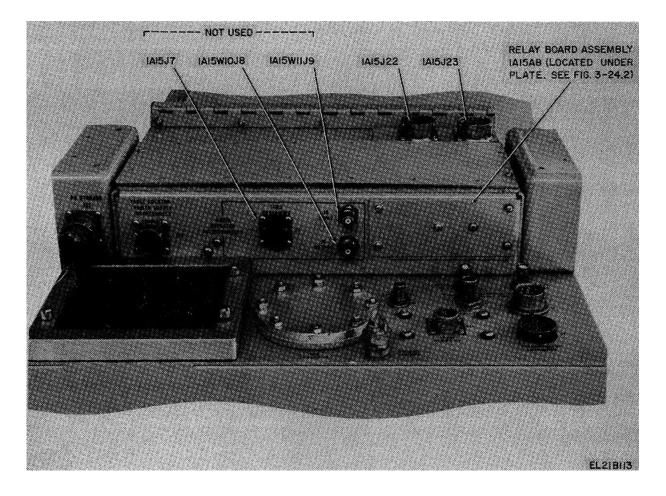

| 3-7                     | Transmitter, Radio T-1054(P)/GRC-144(V), rear top view.<br>parts location  | 3-38   |

| 3-7.1                   | T-1054(P)A/GRC-144 top rear view interface connectors                      | 3-38.1 |

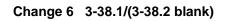

| 3-8                     | Assembly detail, indicator light assemblies, meter                         | 0 0011 |

| 00                      | panel, assembly 1A15A8 typical.                                            | 3-39   |

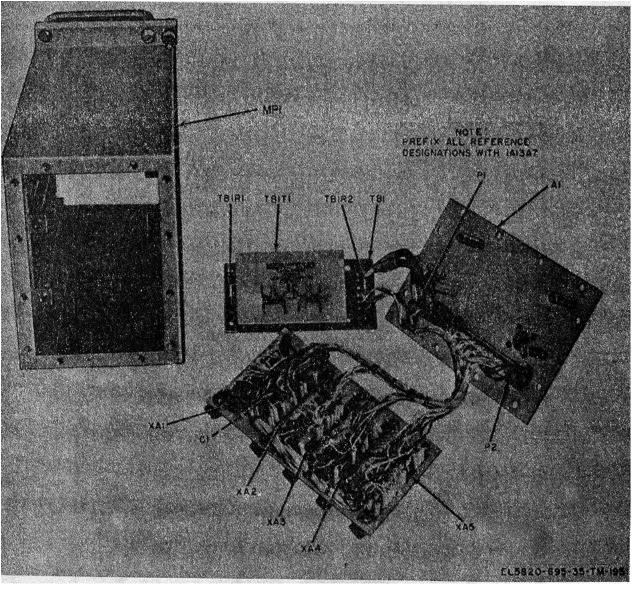

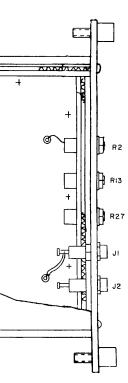

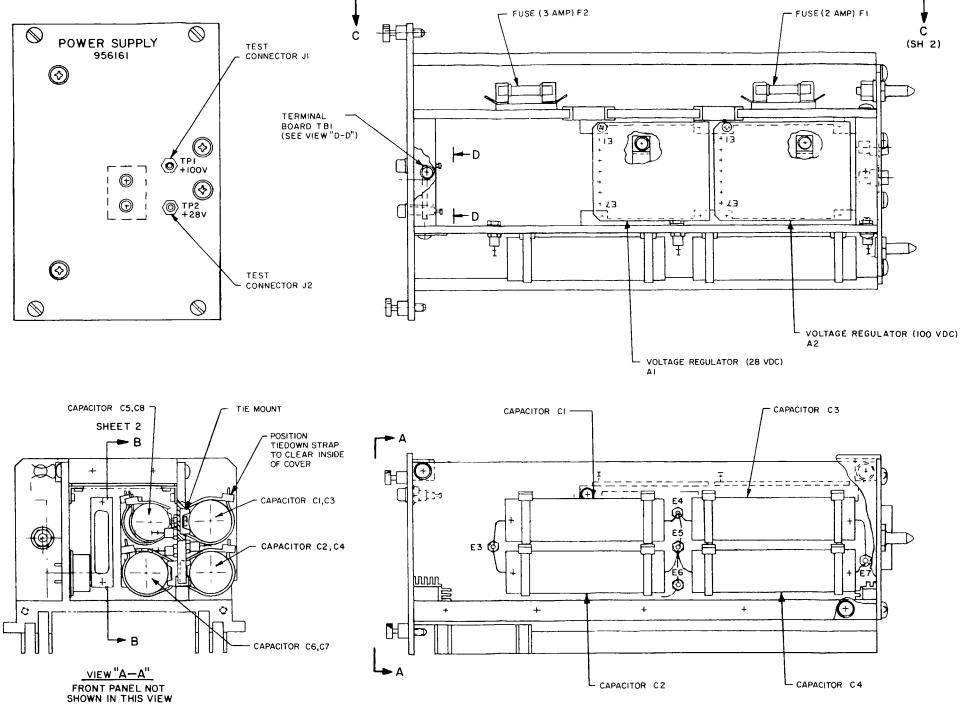

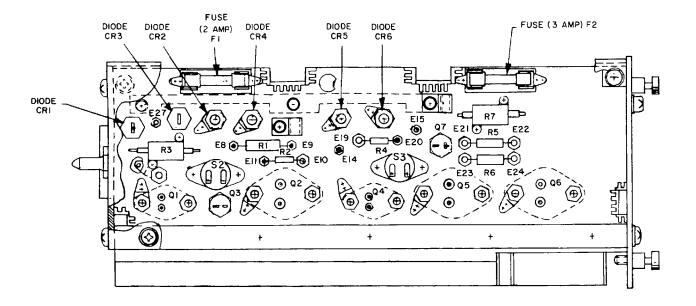

| 3-9                     | Power supply chassis assembly 1A1A13 parts location                        | 3-40   |

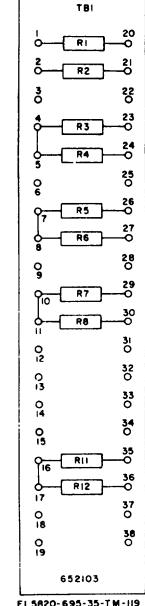

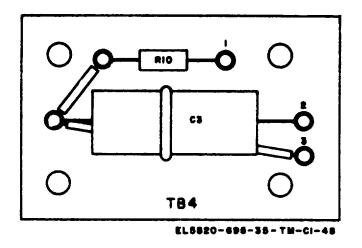

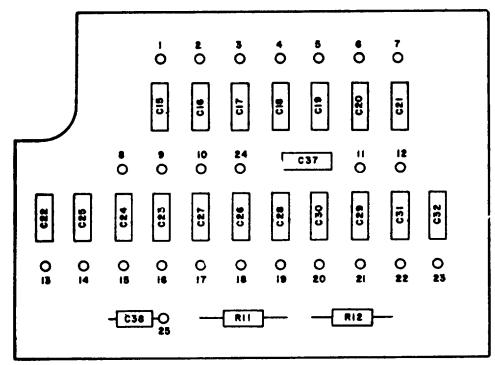

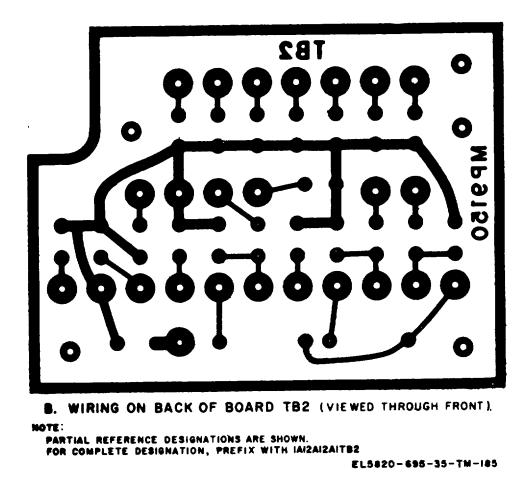

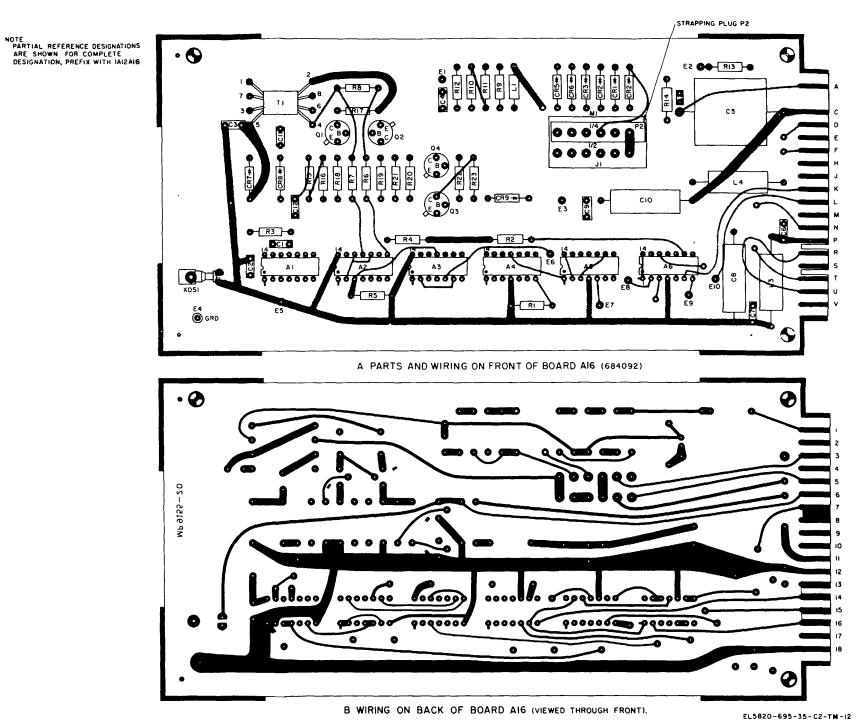

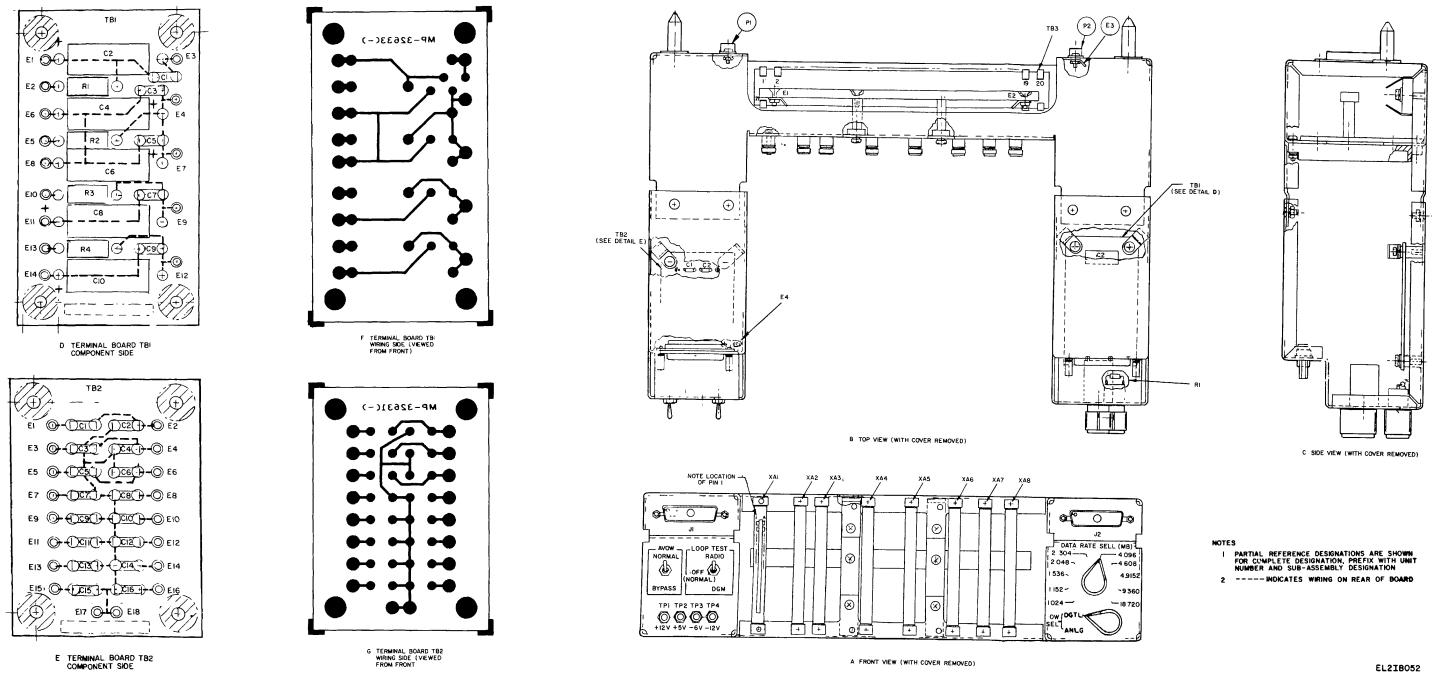

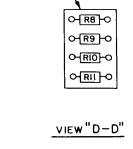

| 3-10                    | Terminal board 1A1A13TB1, top view parts location                          | 3-41   |

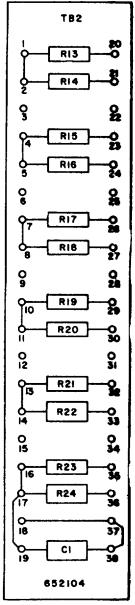

| 3-11                    | Terminal board 1A1A13TB2, top view parts location                          | 3-41   |

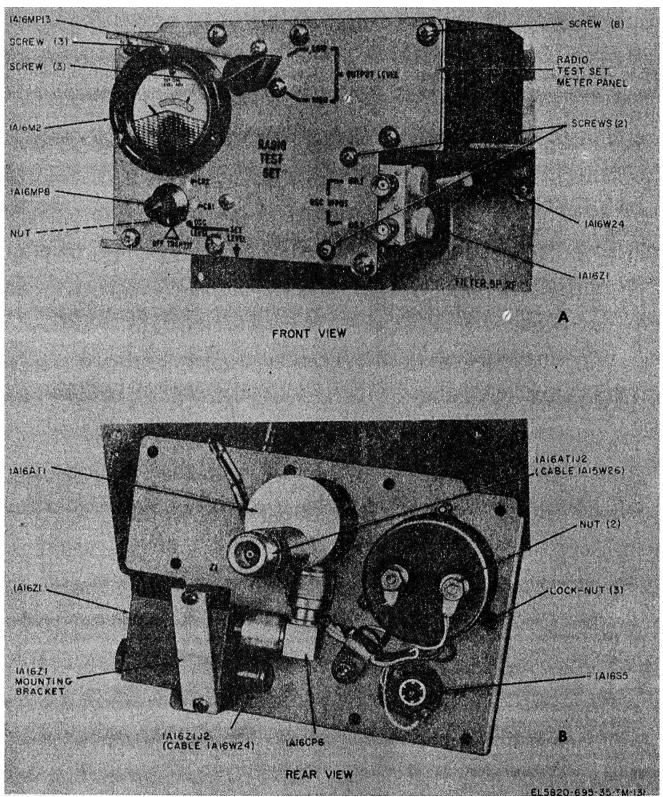

| 3-12                    | Radio test set (P/O 1A16) parts location                                   | 3-42   |

| 3-13                    | Transmitter, Radio T-1054(P)/GRC-144(V) cable locations.                   | 3-43   |

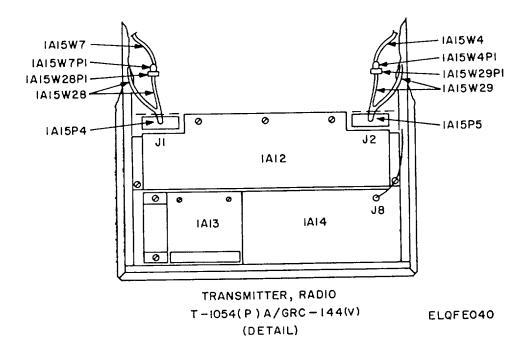

| 3-13.1                  | Transmitter, Radio T-1054(P)A/GRC-144(V)                                   |        |

|                         | interconnecting cables                                                     | 3-44.1 |

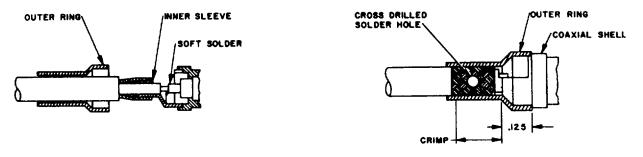

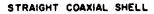

| 3-14                    | Repair detail, rectangular connectors with solder                          | ~      |

| 0.45                    | type removable coaxial contacts                                            | 3-44   |

| 3-15                    | Plate assembly 1A16 rear view parts location                               | 3-45   |

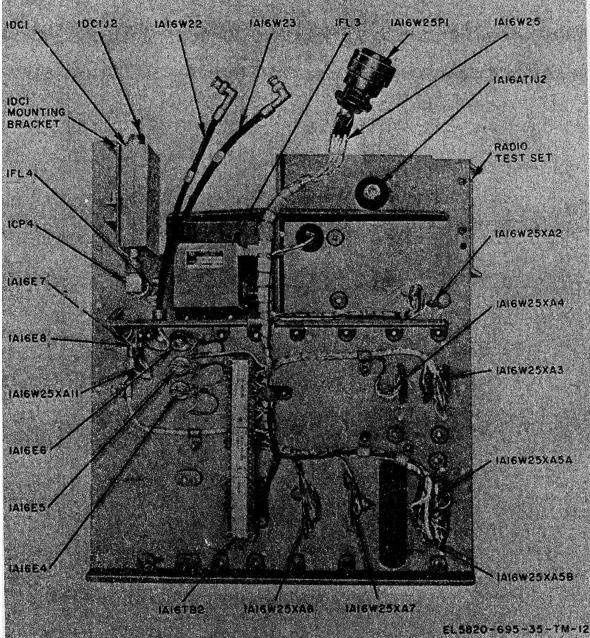

| 3-16                    | Disassembly detail, orderwire assembly electrical                          | 0.40   |

| 0.47                    | frequency synthesizer 1A1311A14                                            | 3-46   |

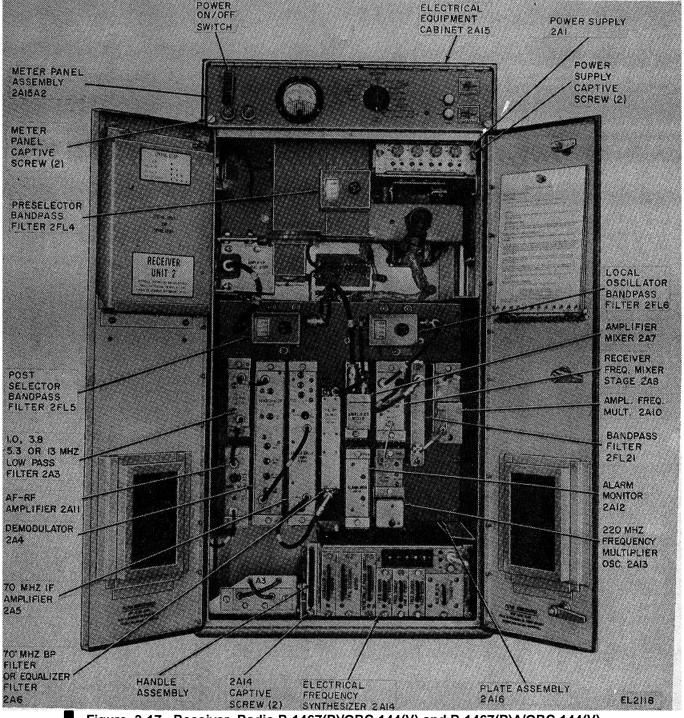

| 3-17                    | Receiver, Radio R-1467(P)/GRC-144(V) and R-1467(P)A/                       | 3-59   |

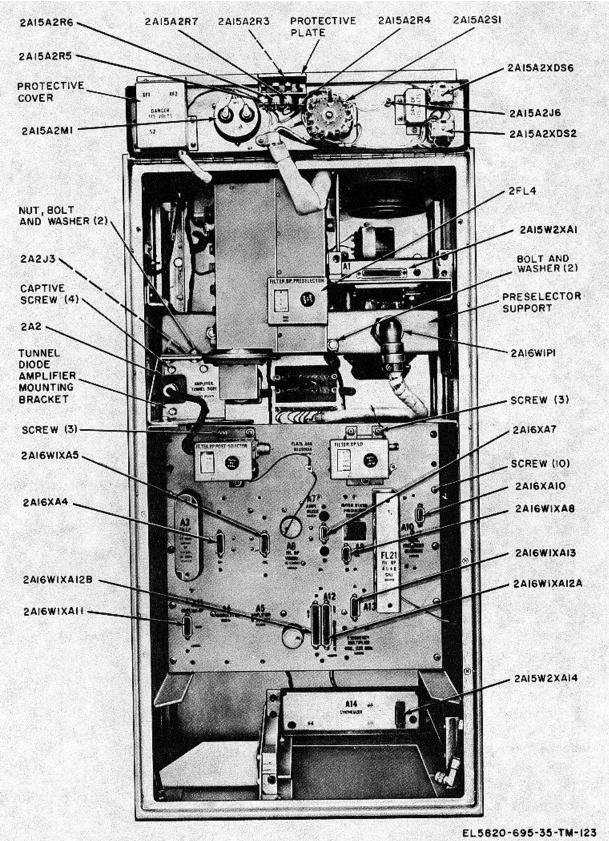

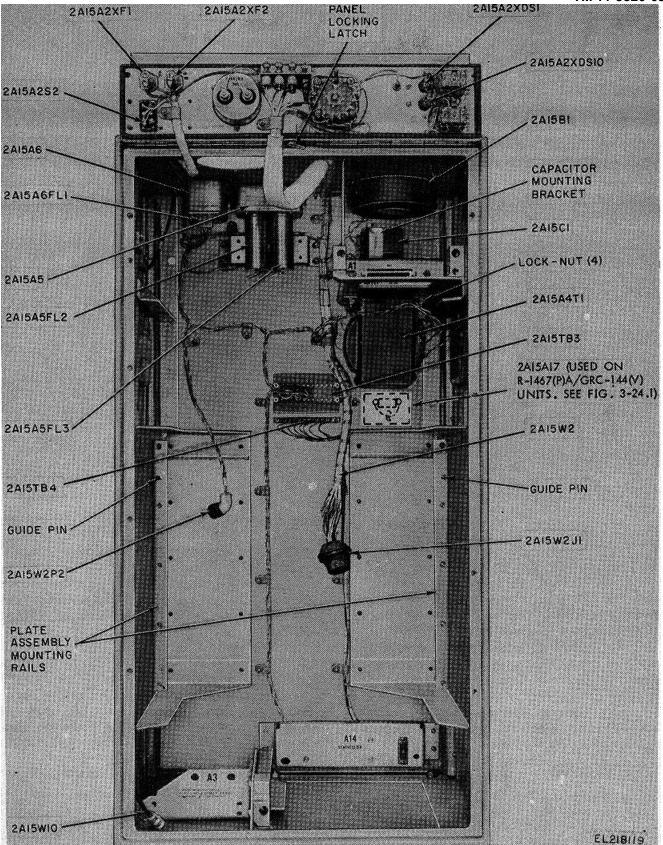

| 3-18                    | GRC-144(V), parts location<br>Electrical equipment cabinet 2A15, partially | 3-39   |

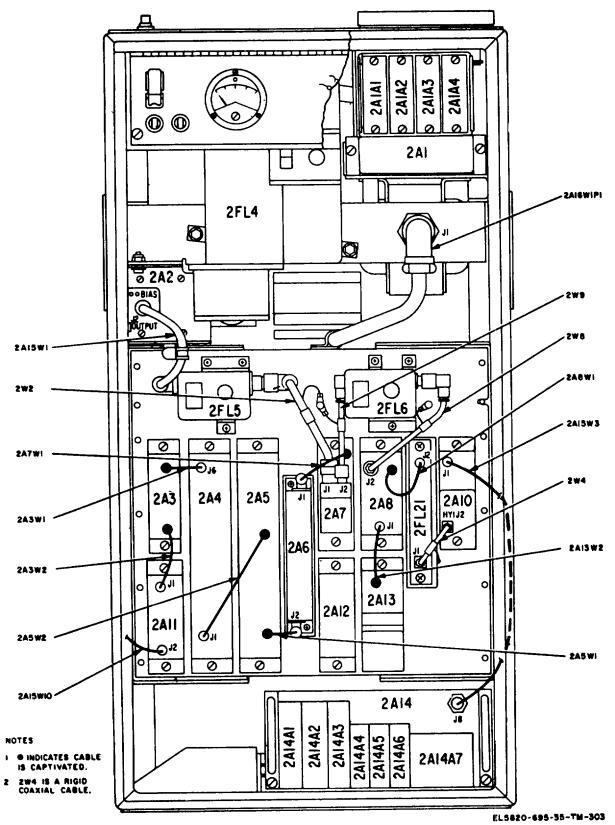

| 5-10                    | disassembled parts location                                                | 3-60   |

| 3-19                    | Electrical equipment cabinet 2A15 with plate assembly                      | 3-00   |

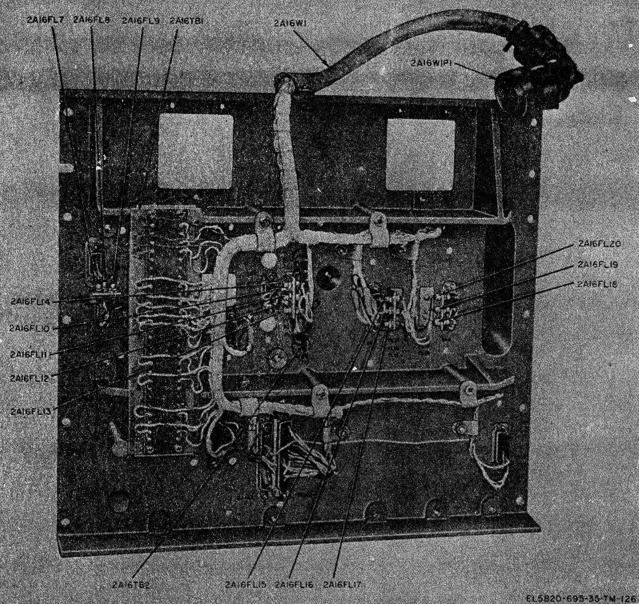

| 5-19                    | 2A16 removed, parts location                                               | 3-61   |

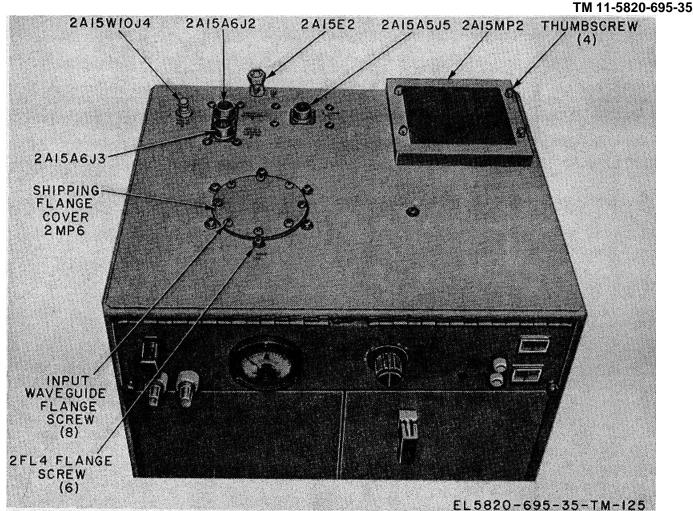

| 3-20                    | Receiver, Radio R-1467/GRC-144 top view parts location                     | 3-62   |

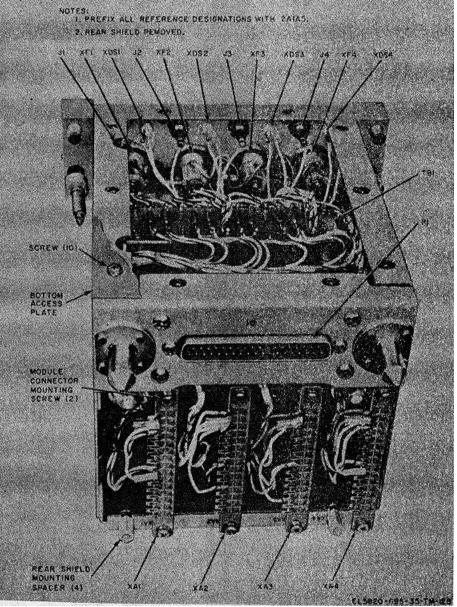

| 3-21                    | Plate assembly 2A16, rear view, parts location                             | 3-63   |

| 3-22                    | Power supply chassis assembly 2A1A5 parts location                         | 3-64   |

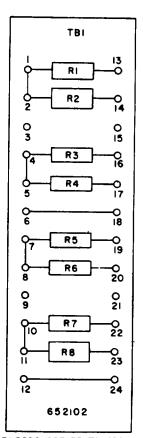

| 3-23                    | Terminal board 2A1A5TB1, top view parts location                           | 3-65   |

| 3-24                    | Receiver Radio R-1467(P)/GRC-144(V), cable locations                       | 3-66   |

| 3-24.1                  | Thermostatic switch assembly 1A15A17/2A15A17, parts                        | 0.00   |

| •                       | location                                                                   | 3-66.1 |

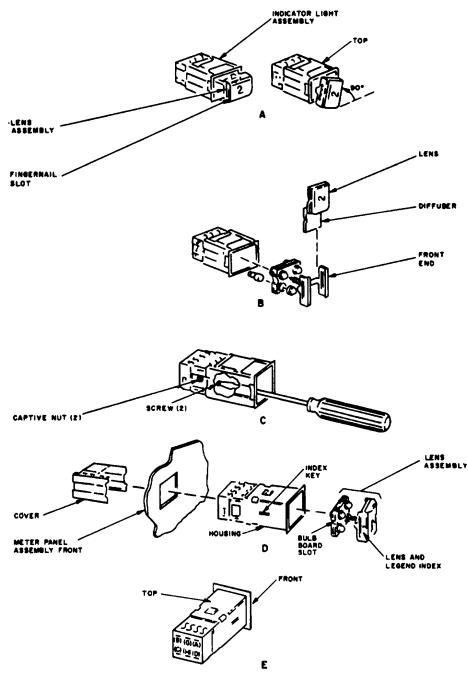

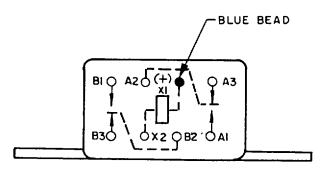

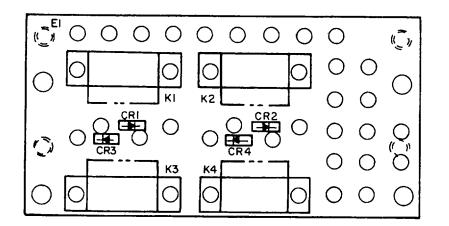

| 3-24.2                  | Relay board assembly 1A15A18, parts location                               | 3-66.2 |

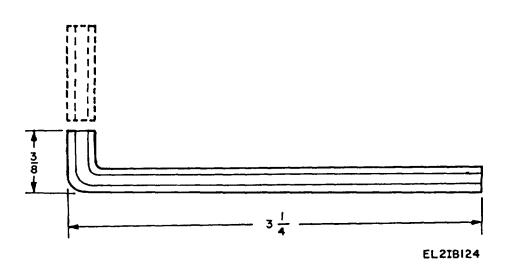

| 3-24.3                  | Fabricated allen wrench dimensions                                         | 3-74.1 |

| 3-25                    | Indicator, Alignment ID-1708/GRC parts location                            | 3-74   |

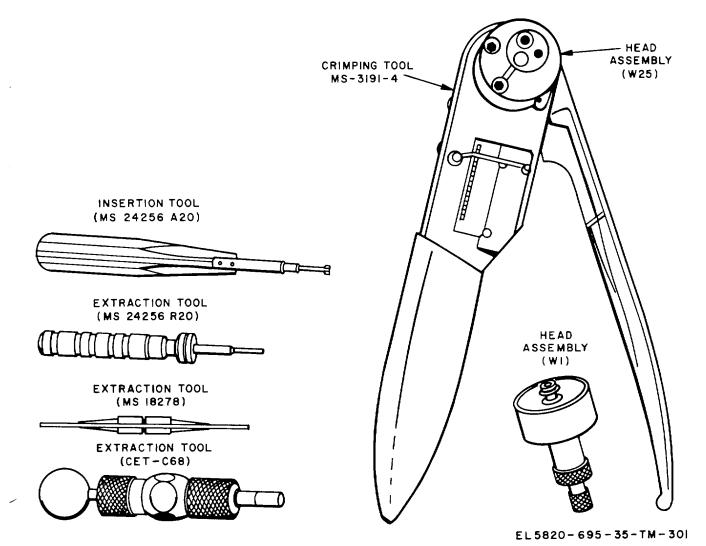

| 3-26                    | AN/GRC-144 connector repair tools                                          | 3-75   |

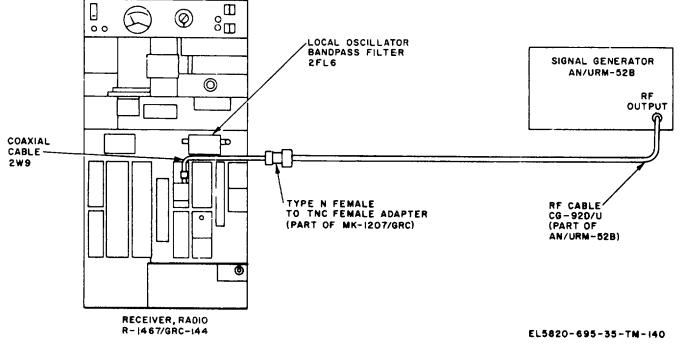

| 3-27                    | Calibration of R-1467/GRC-144 local oscillator                             |        |

|                         | metering circuits, equipment connections                                   | 3-82   |

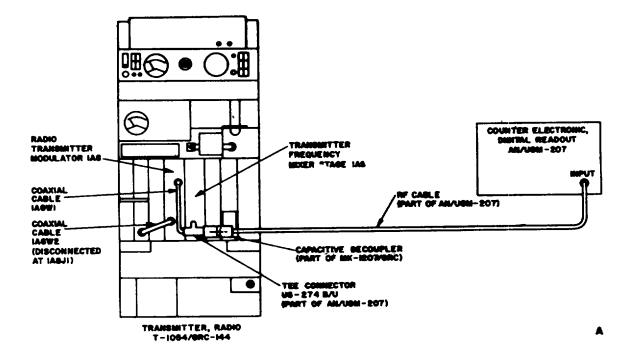

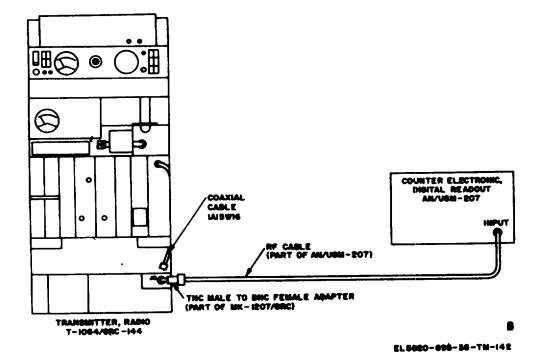

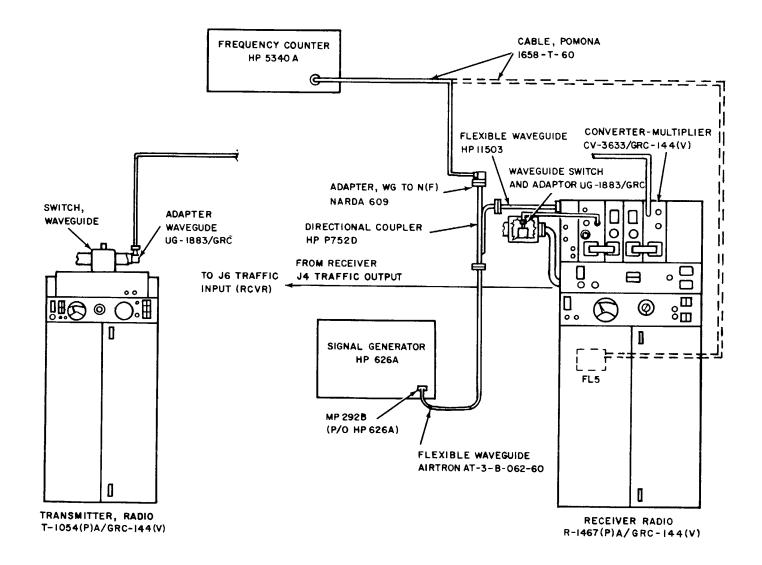

| 3-28                    | T-1054(P)/GRC-144(V) frequency accuracy test setup                         | 3-86   |

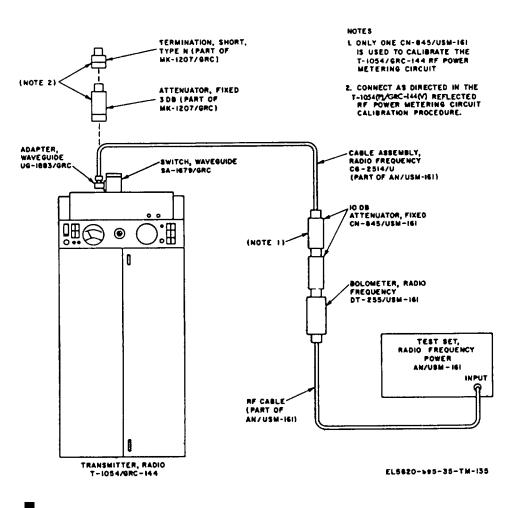

| 3-29                    | T-1054(P)/GRC-144(V) output power test setup                               | 3-90   |

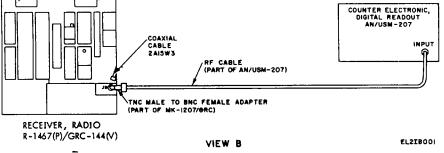

| 3-30                    | R-1467(P)/GRC-144(V) frequency accuracy test setup                         | 3-92   |

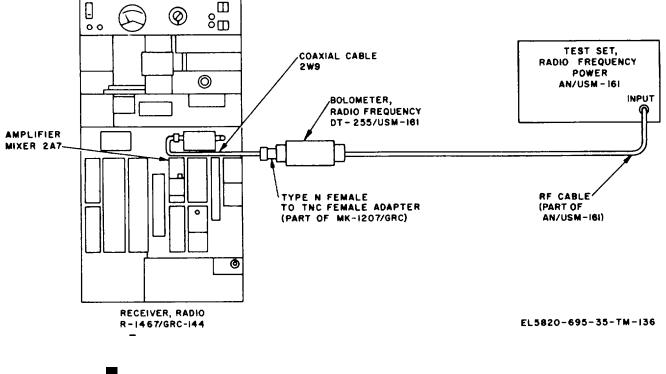

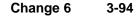

| 3-31                    | R-1467(P)/GRC-144(V) local oscillator power test setup,                    | 3-94   |

| 3-32                    | Calibration of signal generator AN/URM-52B, equipment<br>connections       | 3-96   |

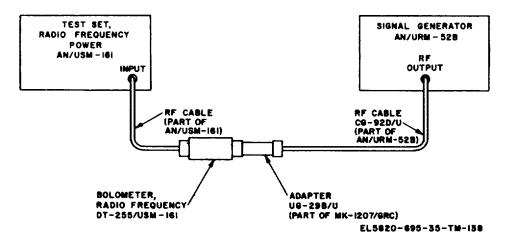

| 3-33                    | IF gain and carrier alarm test setup                                       | 3-97   |

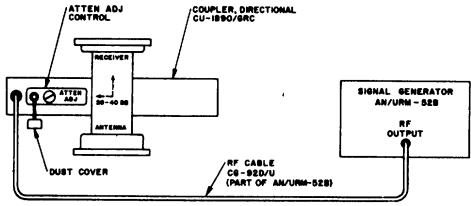

| 3-34                    | Mounting detail, van axial fans 1A15B1 and 2A1581                          | 3-97   |

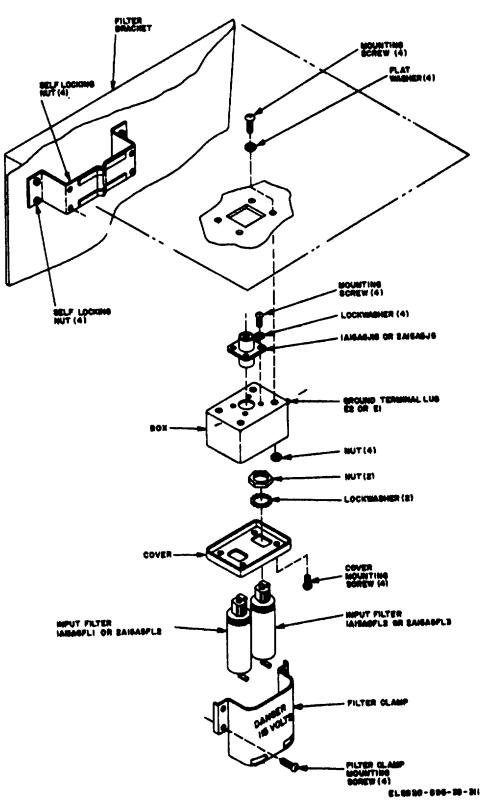

| 3-35                    | Exploded view, input assembly 1A15A6 and 2A15A5                            | 3-98   |

| 3-36                    | Transmitter cabinet, terminal board 1A15TB4 parts                          |        |

|                         | location                                                                   | 3-100  |

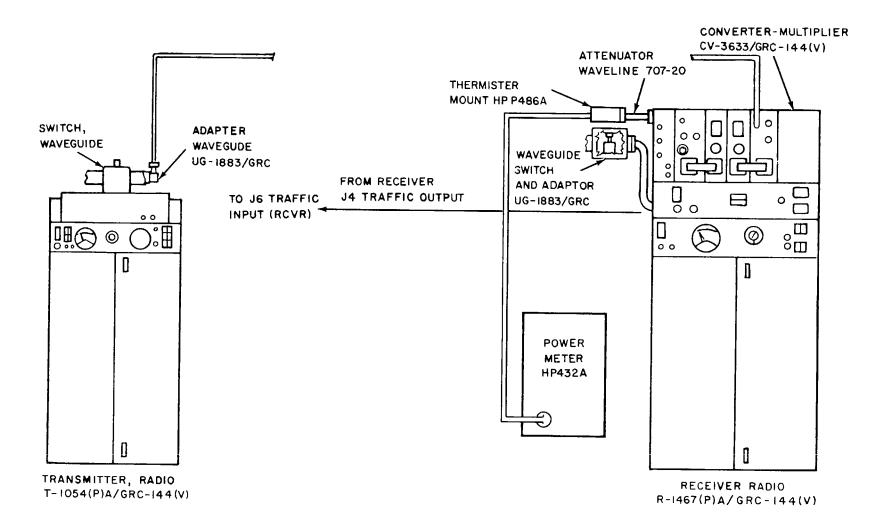

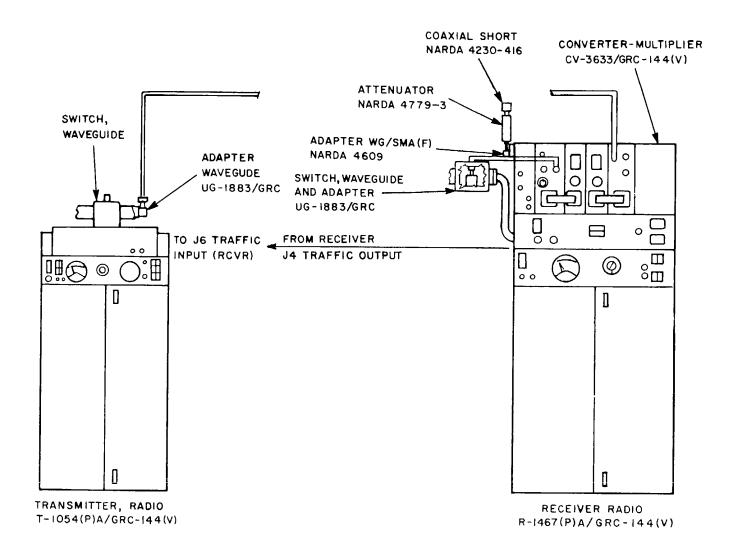

| 3-37                    | AN/GRC-144(V)4 output power test at 14.4 to 15.0 GHz                       | 3-102  |

| 3-38                    | CV-3633/GRC-144(V) reflected power alarm threshold                         | -      |

|                         | test and calibration                                                       | 3-106  |

| Figure<br><u>Number</u> | Title                                                                                                    | Page           |

|-------------------------|----------------------------------------------------------------------------------------------------------|----------------|

| 3-39                    | CV-3633/GRC-144(V) local oscillator frequency<br>accuracy test setup                                     | 3-110          |

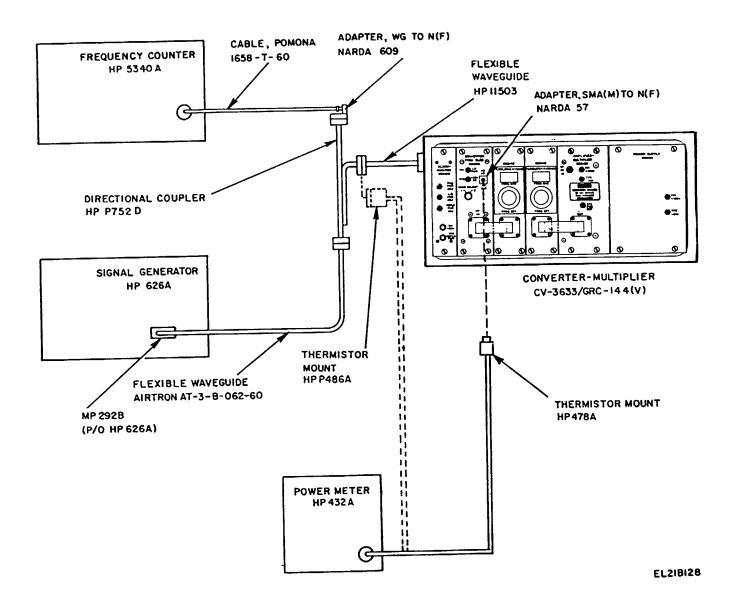

| 3-40                    | CV-3633/GRC-144(V) receive section conversion<br>gain test                                               | 3-113          |

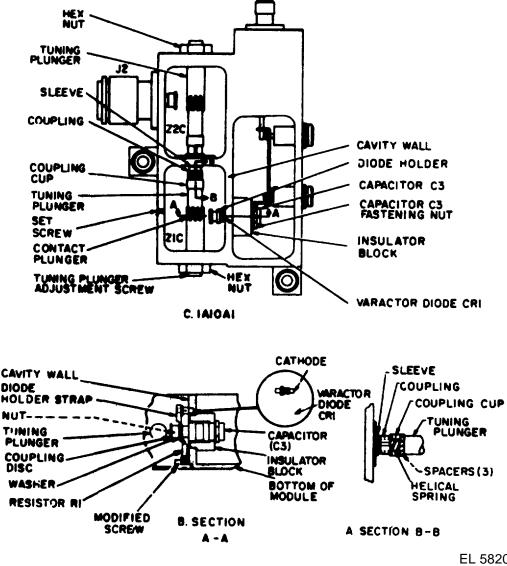

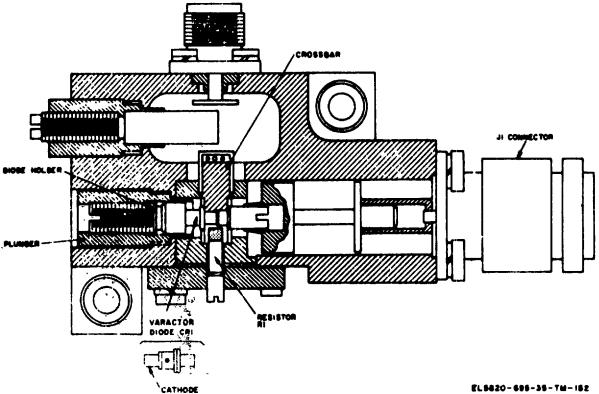

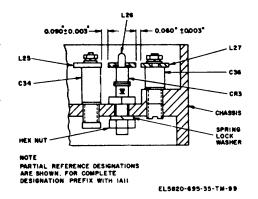

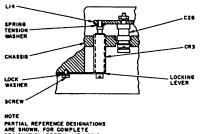

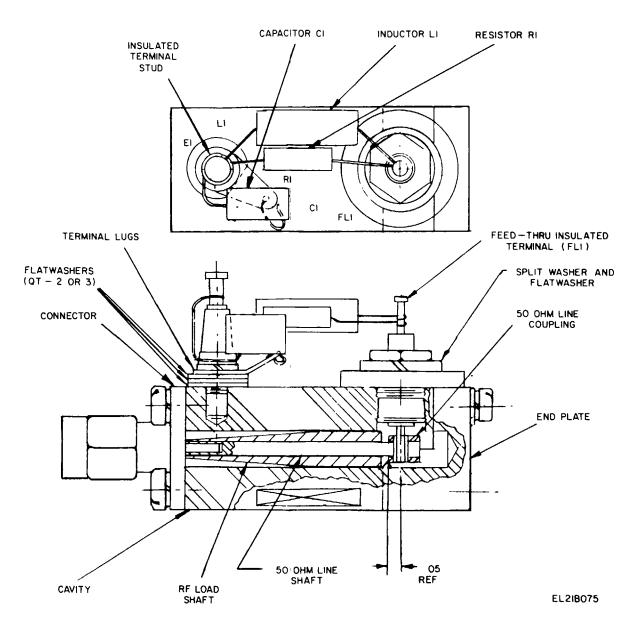

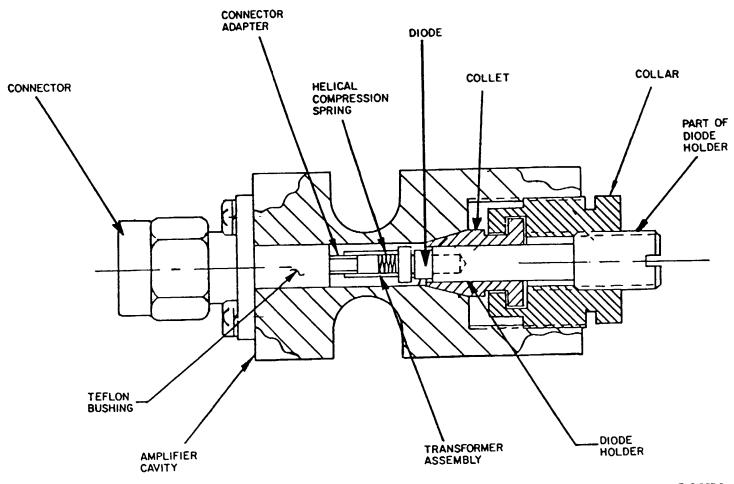

| 4-1                     | Transmitter 2nd stage frequency multiplier 1A10A1<br>varactor diode replacement                          | 4-3            |

| 4-2                     | Transmitter 3rd stage frequency multiplier 1A10A2<br>varactor diode replacement                          | 4-4            |

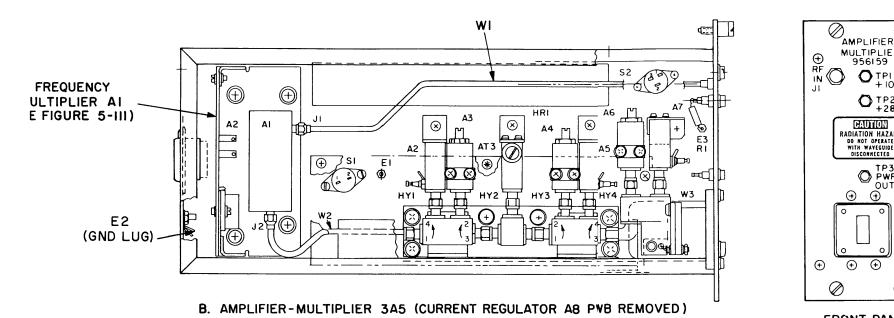

| 4-3                     | Transmitter amplifier-frequency multiplier 1A11,<br>varactor diode replacement                           | 4-5            |

| 4-4                     | Amplifier-frequency multiplier 2A10 varactor diode<br>replacement                                        | 4-6            |

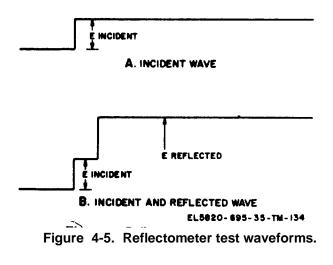

| 4-5                     | Reflected meter test waveforms                                                                           | 4-9            |

| 4-6                     | 5/6V voltage regulator 1A1A1 through 1A1A4 bracket<br>wiring diagram                                     | 4-11           |

| 4-7                     | 12V voltage regulator 1A1A6 through 1A1A9 and 2A1A3<br>bracket wiring diagram                            | 4-12           |

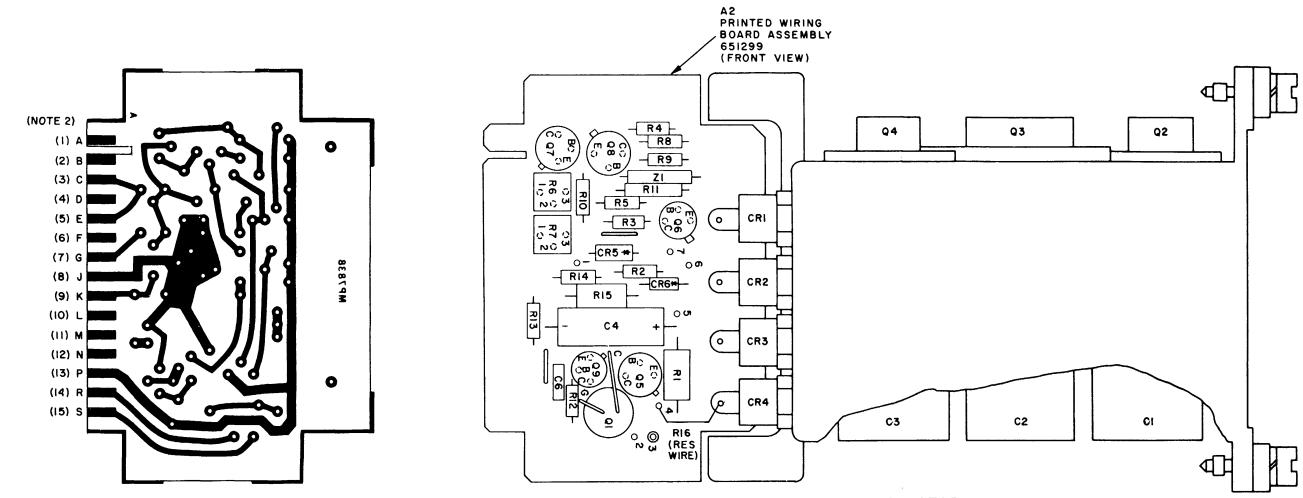

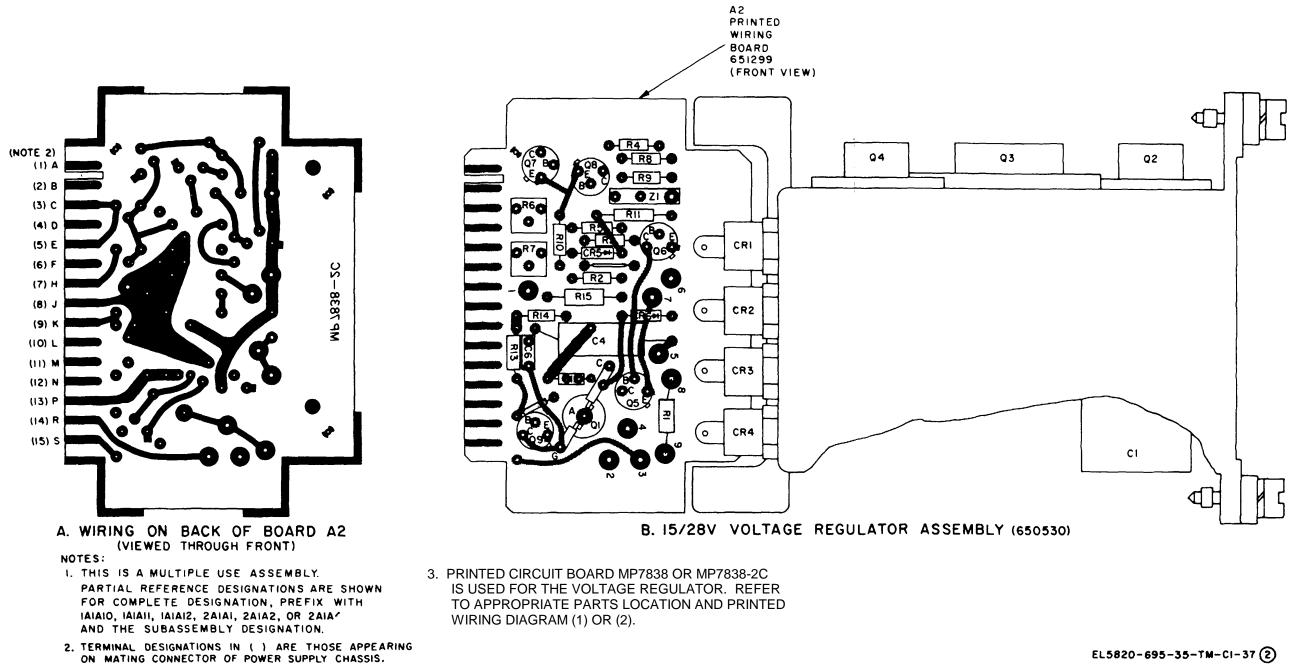

| 4-8                     | 15/28V voltage regulator 1A1A0 through 1A1A12, 2A1A1,                                                    |                |

| 4-9(1)                  | 2A1A2 and 2A1A4, bracket wiring diagram<br>Attenuator assembly 1A3 wiring diagram (Part 1 of 2)          | 4-13<br>4-14   |

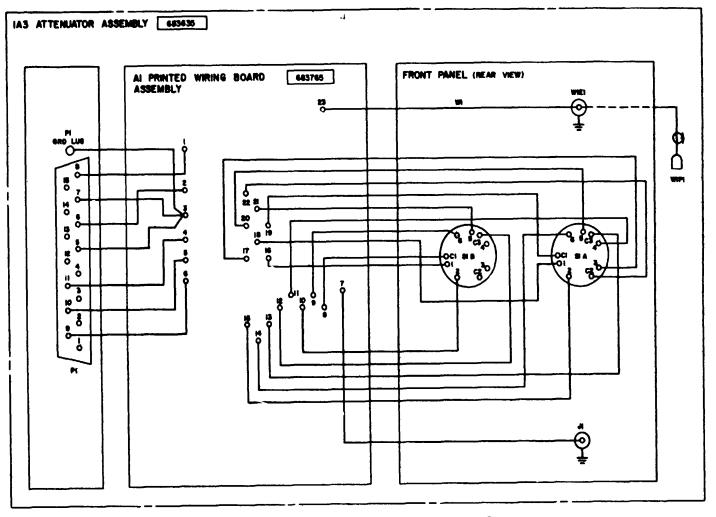

| 4-9(2)                  | Attenuator assembly 1A3 wiring diagram (Part 1 of 2)                                                     | 4-14           |

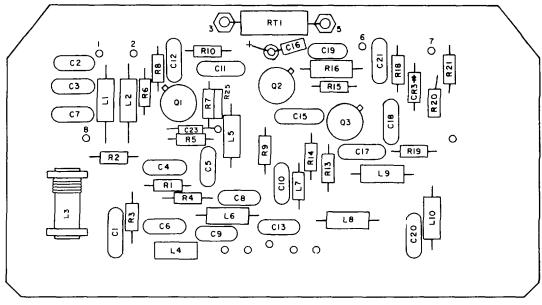

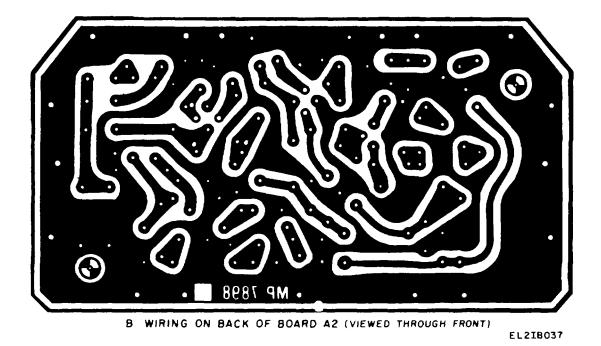

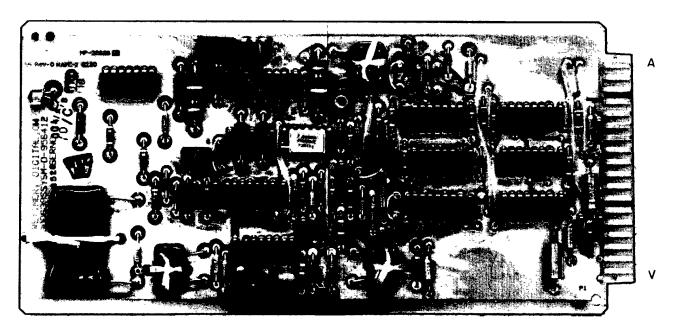

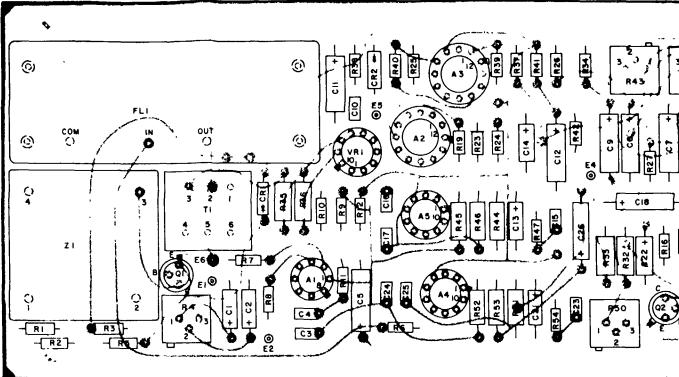

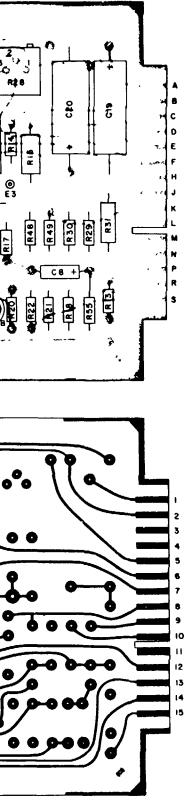

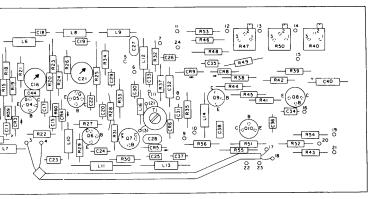

| 4-3(2)                  | AF-RF amplifier 1A4/2A11 wiring Diagram                                                                  | 4-14.1         |

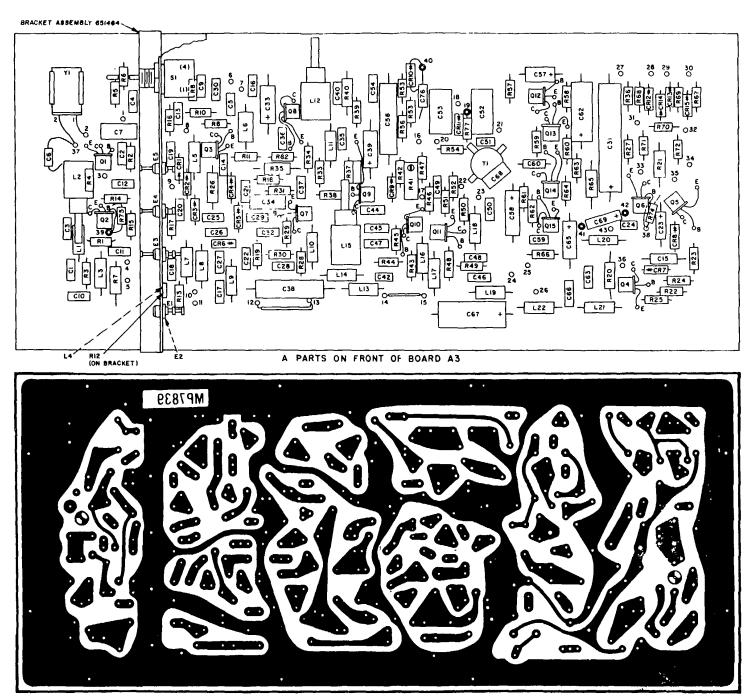

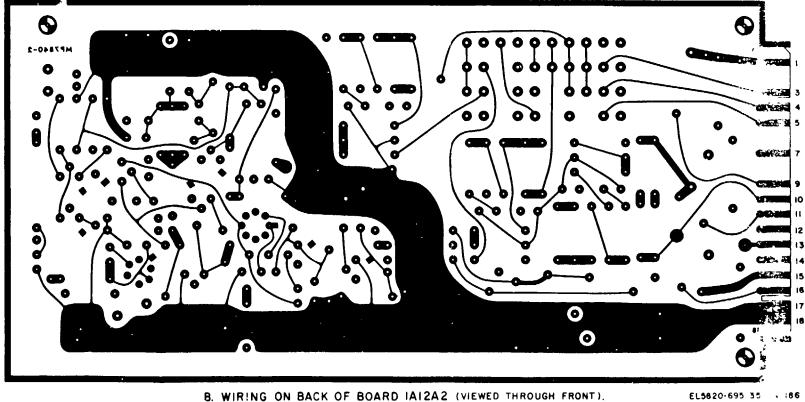

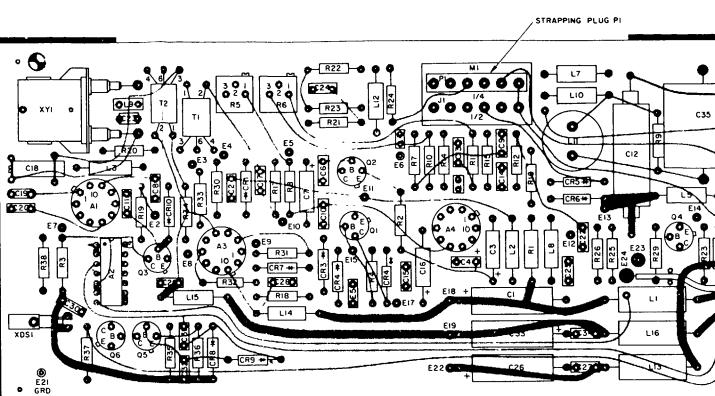

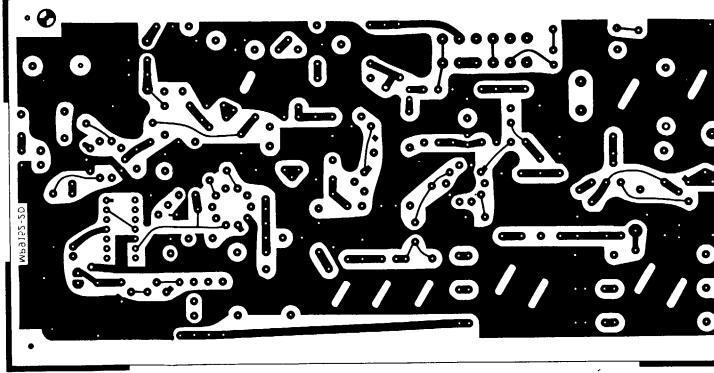

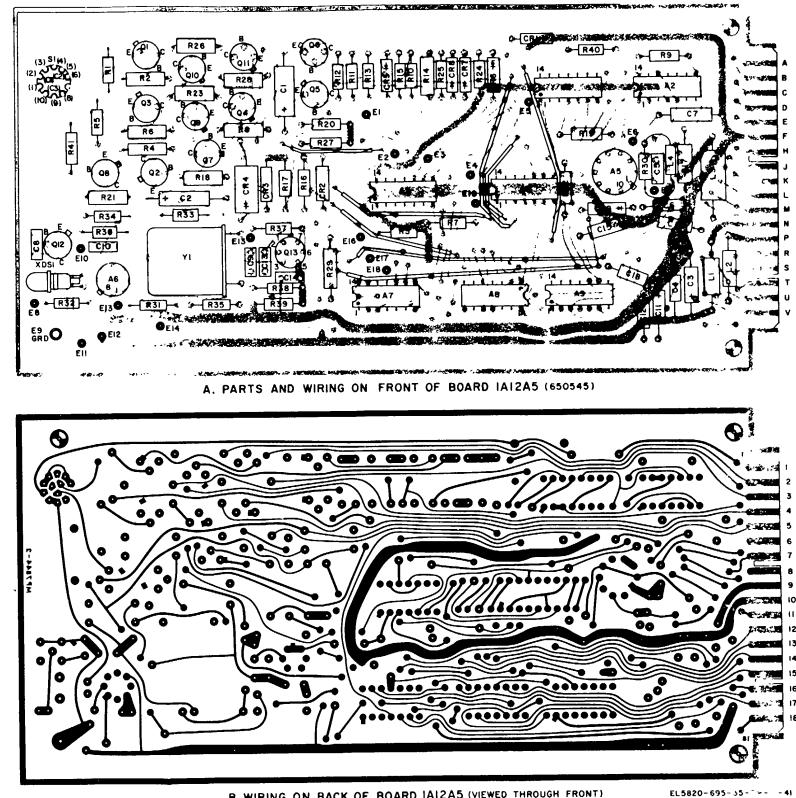

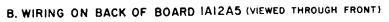

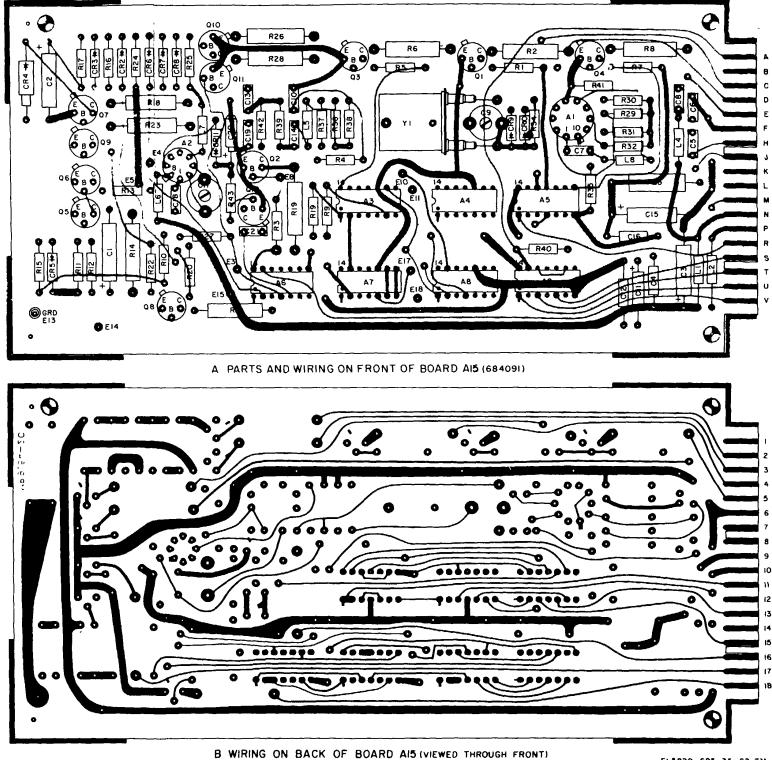

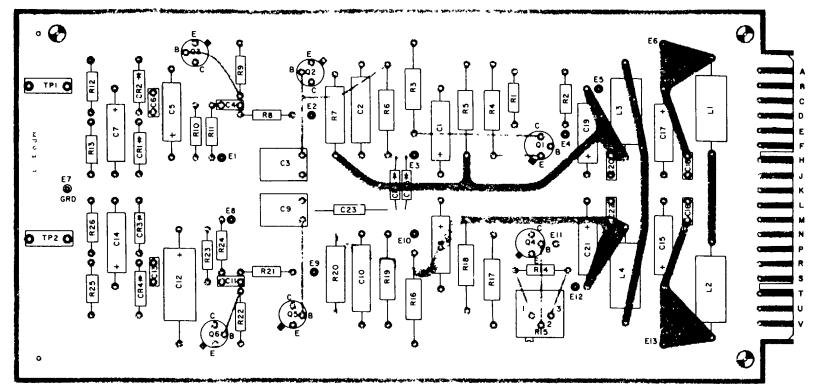

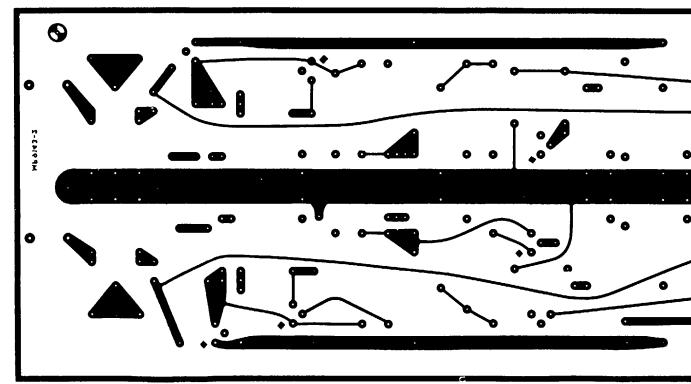

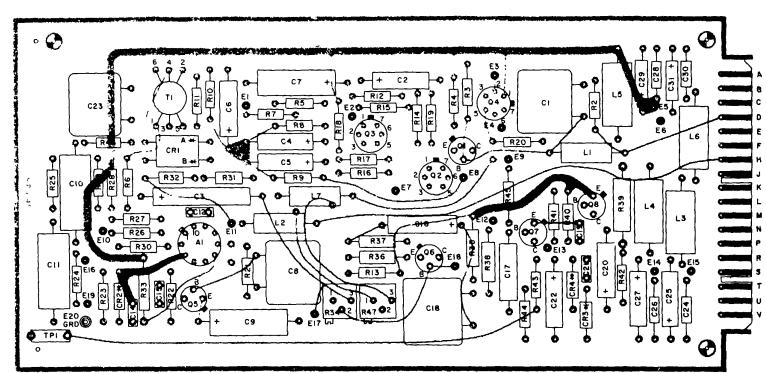

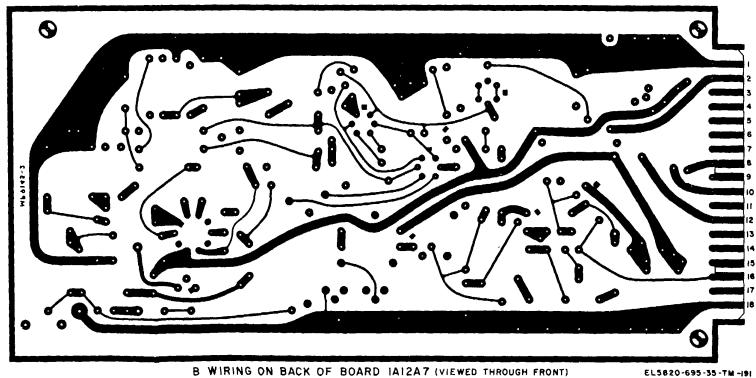

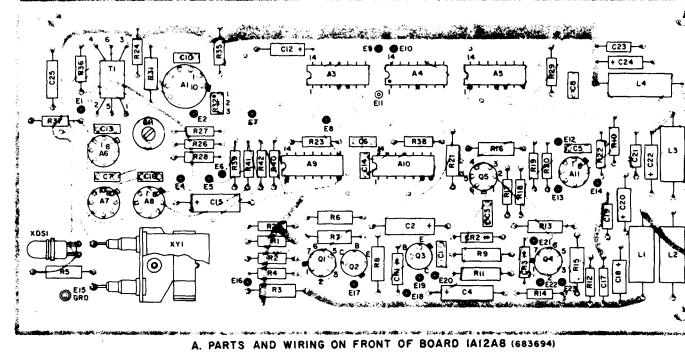

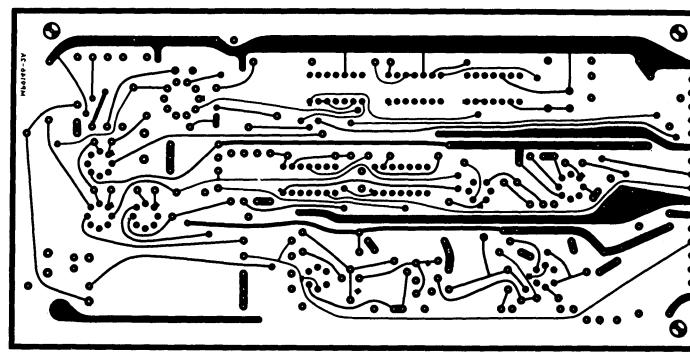

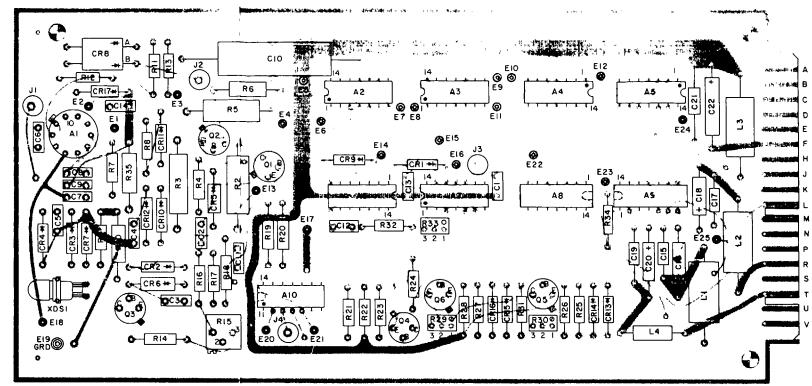

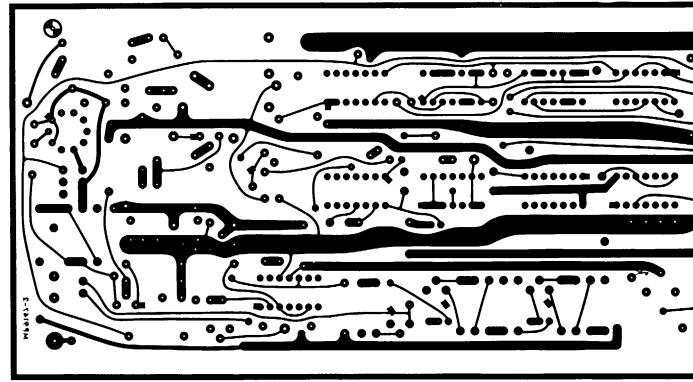

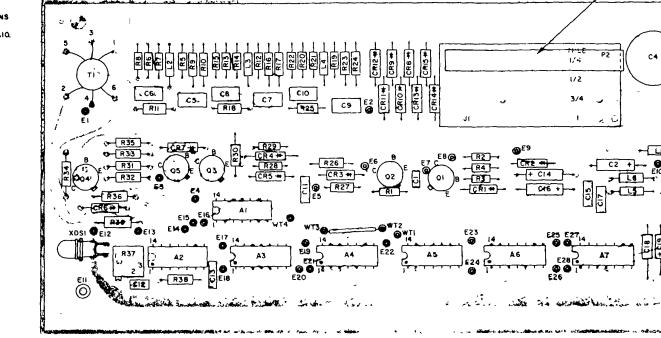

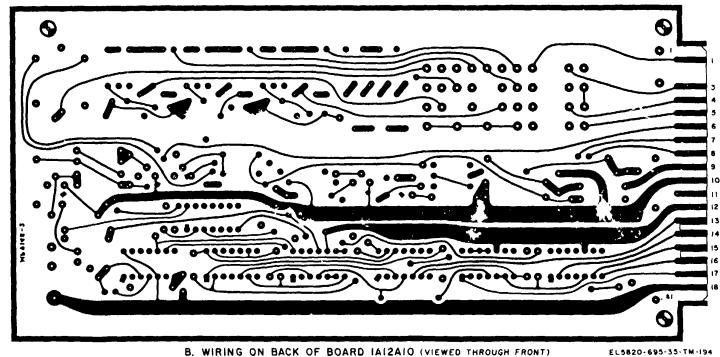

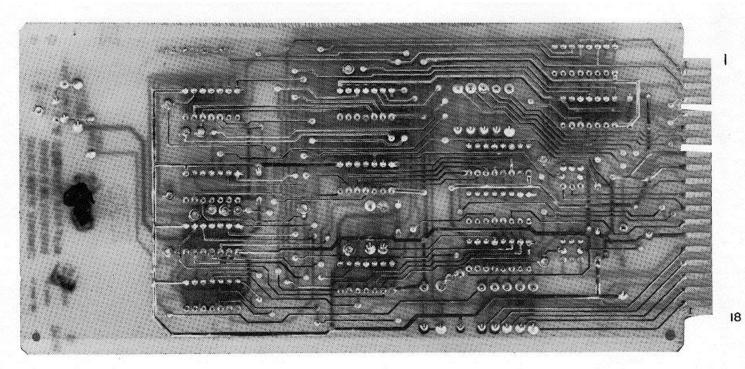

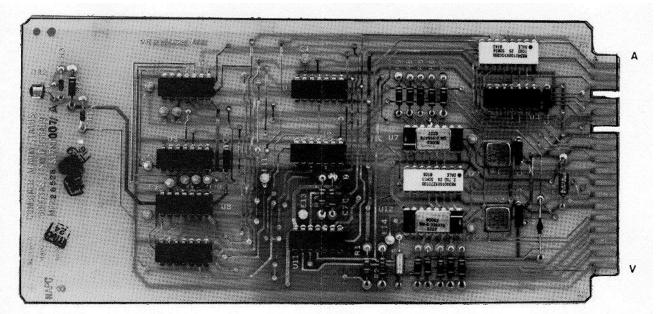

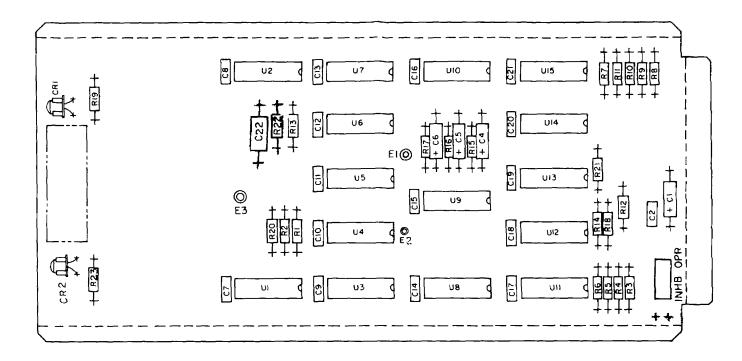

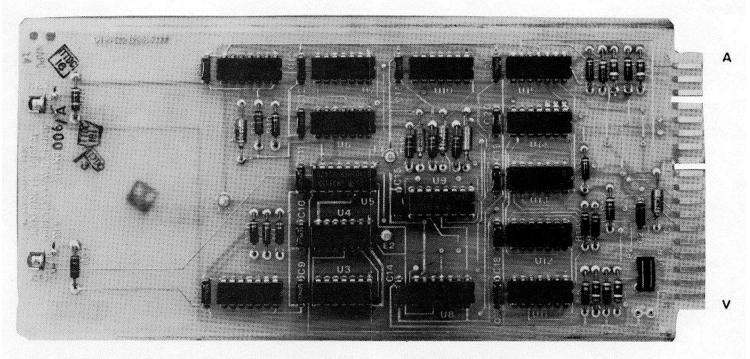

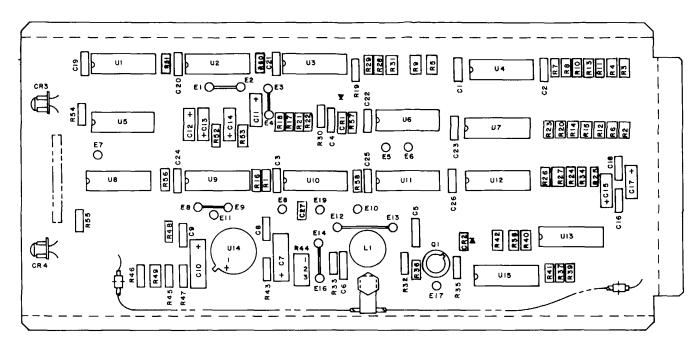

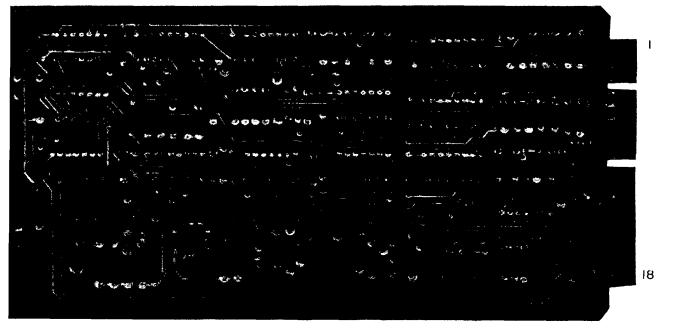

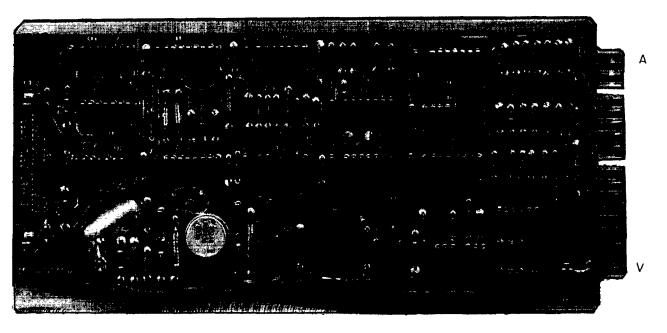

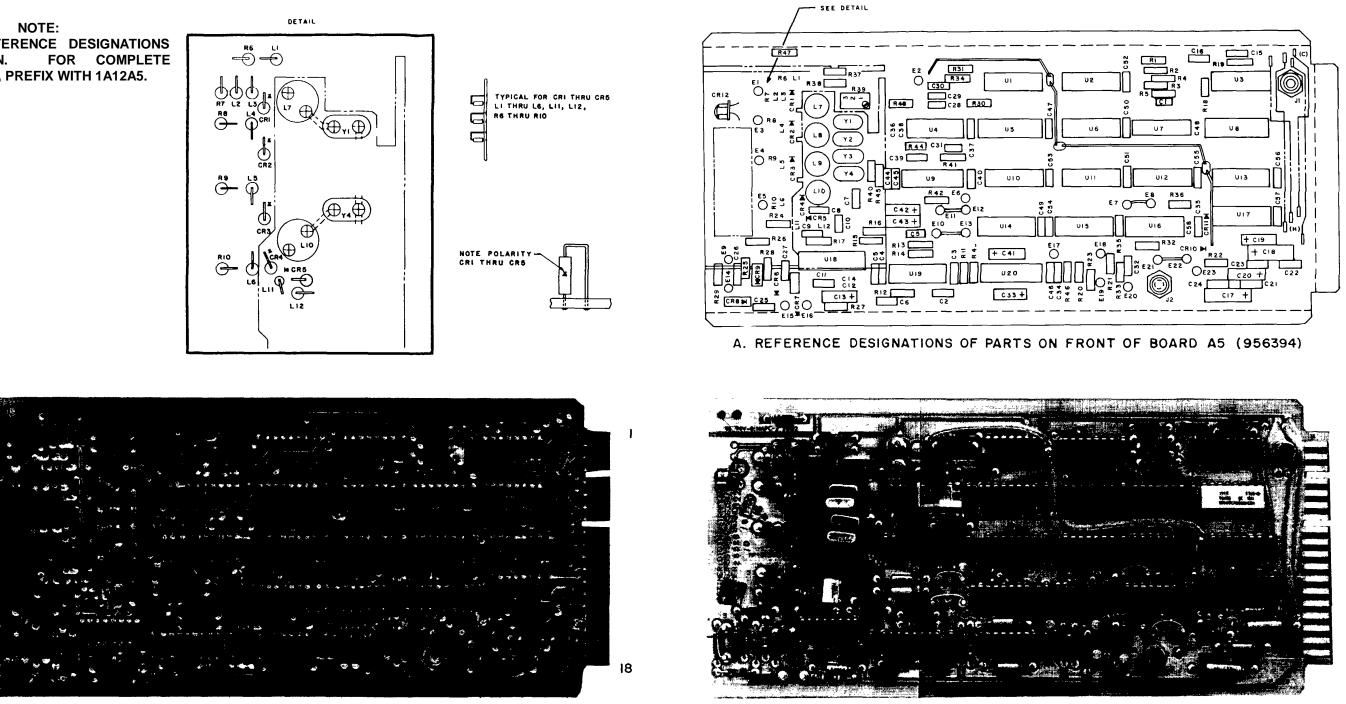

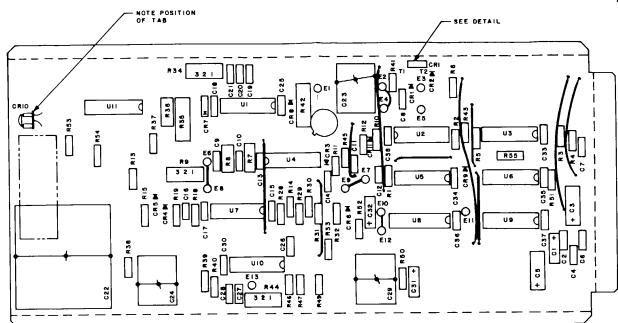

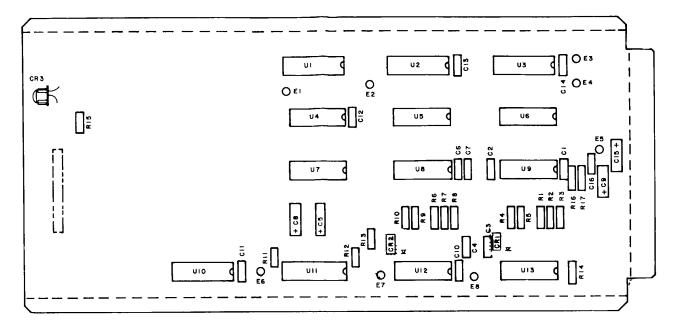

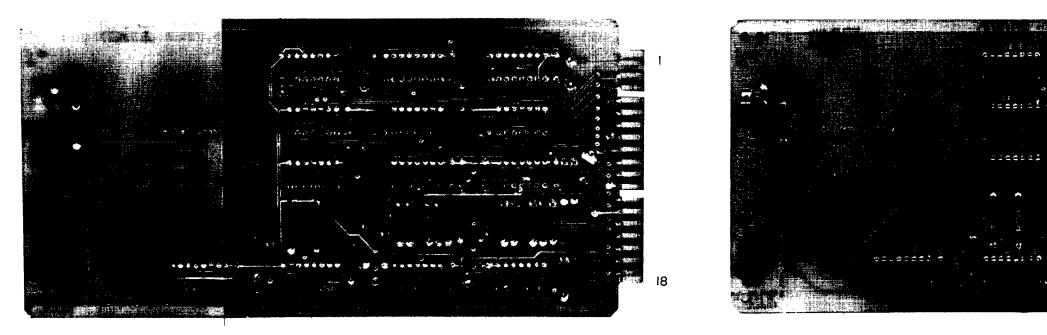

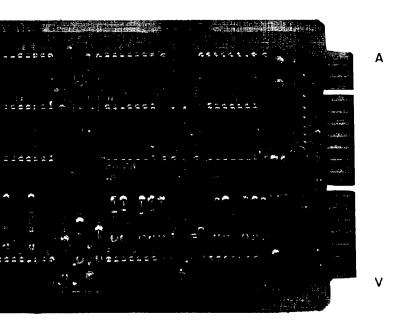

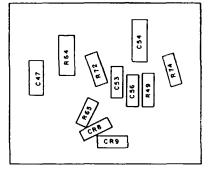

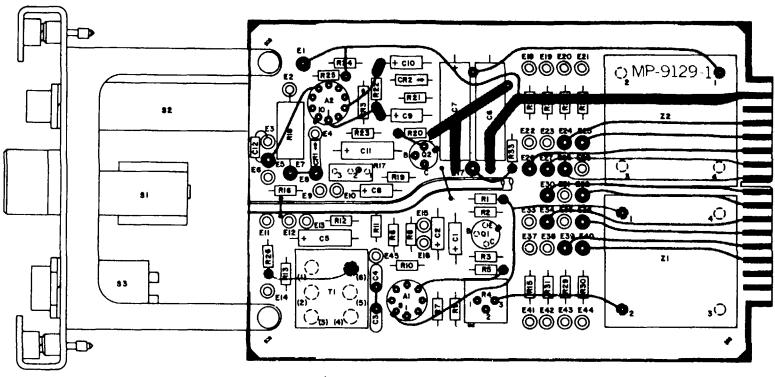

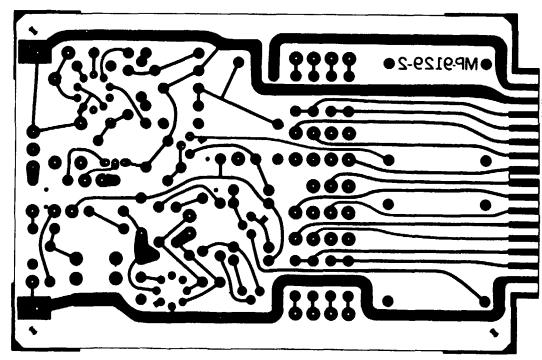

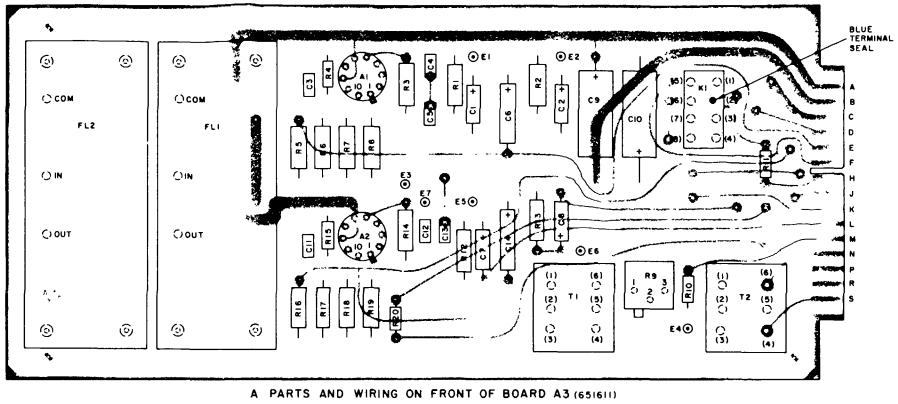

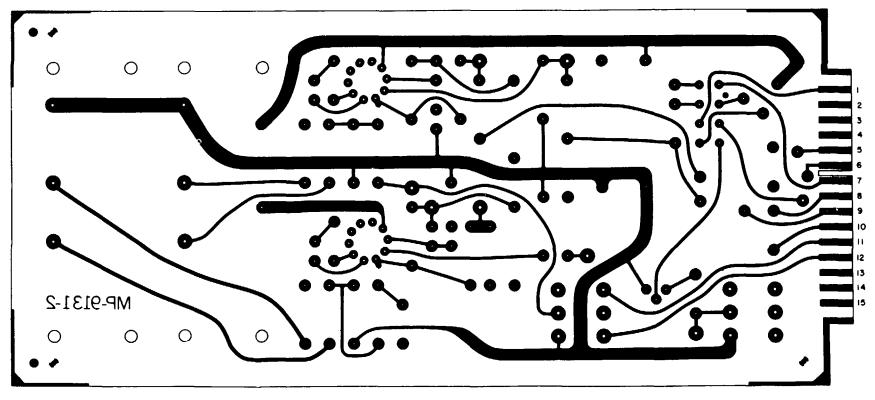

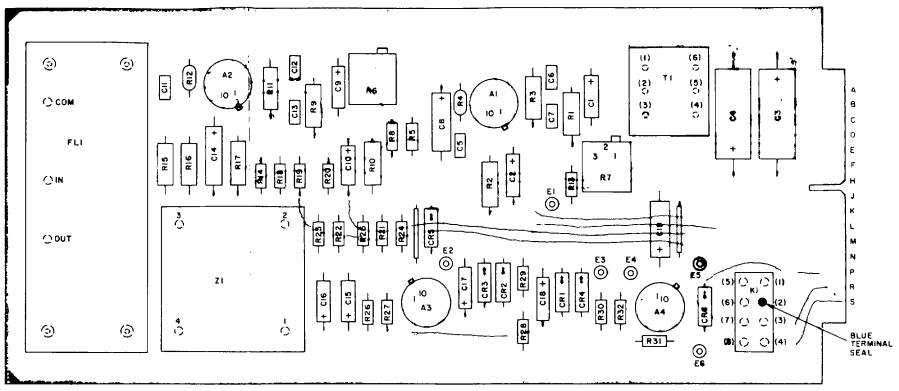

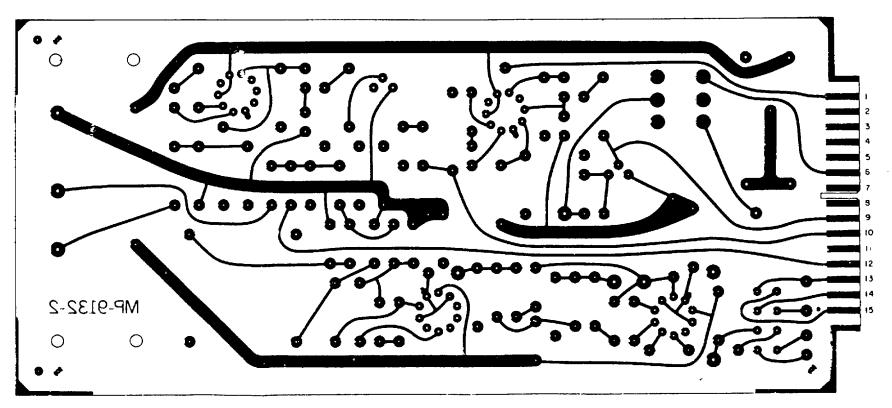

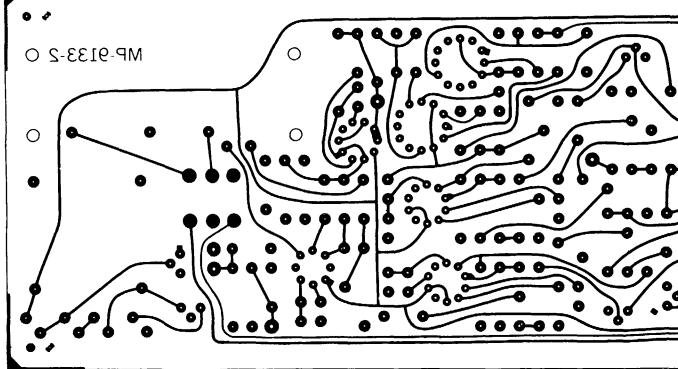

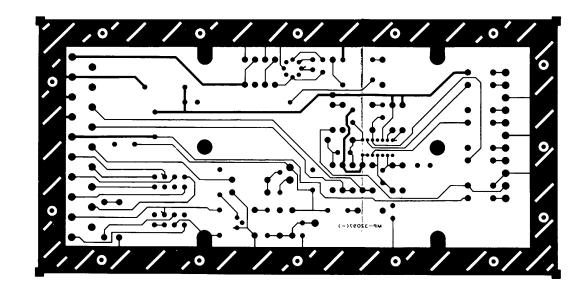

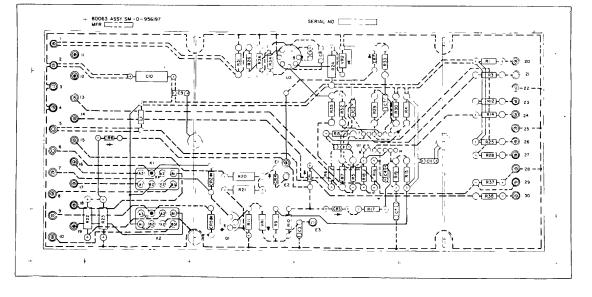

| 4-11(1)                 | AF-RF amplifier 1A4/2A11 parts location and printed                                                      | 4-15           |

|                         | wiring diagram (Part 1 of 2)                                                                             | 4-16           |

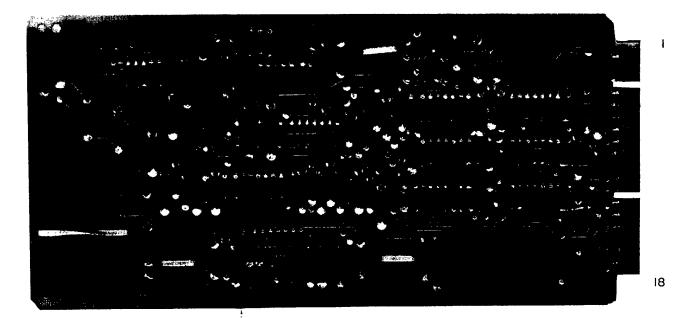

| 4-11(2)                 | AF-RF amplifier 1A4/2A11 parts location and printed                                                      | 4 47           |

| 4.40                    | wiring diagram (Part 2 of 2)                                                                             | 4-17           |

| 4-12<br>4-12.1          | 4.5 MHz low pass filter 1A6, wiring diagram                                                              | 4-18           |

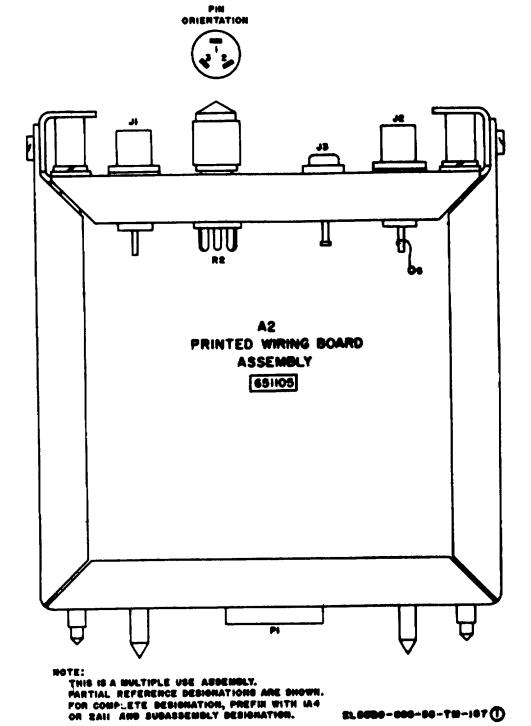

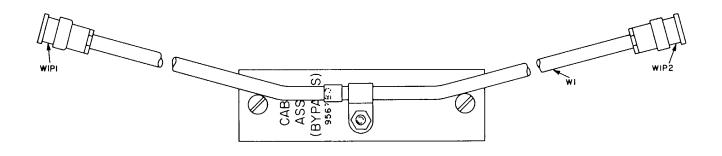

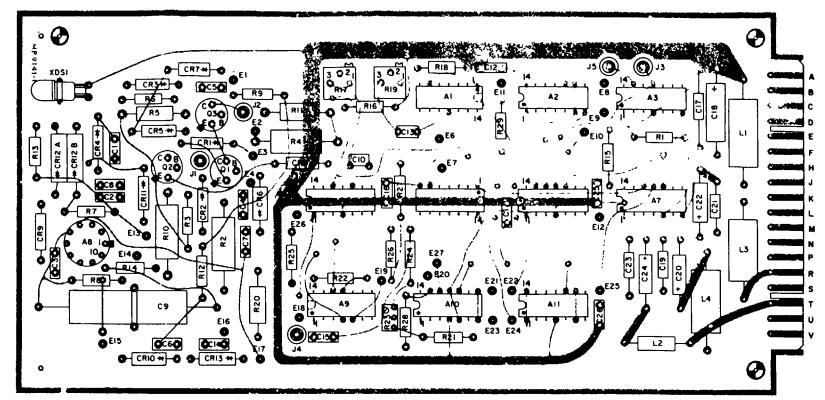

| 4-12.1<br>4-13          | Cable bypass, parts location diagram                                                                     | 4-18.1<br>4-19 |

| 4-13                    | 4.5 MHz low pass filter 1A6, parts location                                                              | 4-19<br>4-20   |

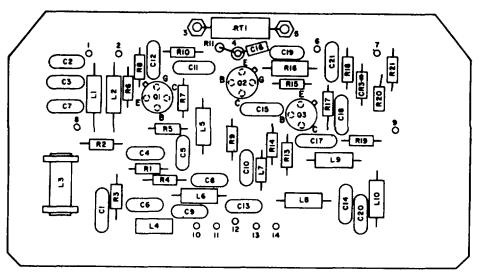

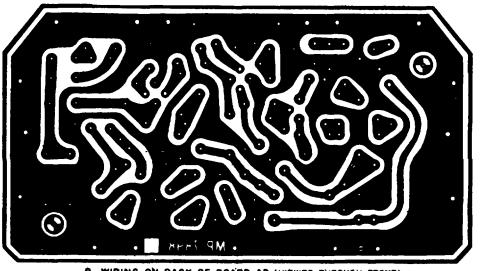

| 4-14                    | Transmitter frequency mixer stage 1A9, wiring diagram                                                    | 4-20           |

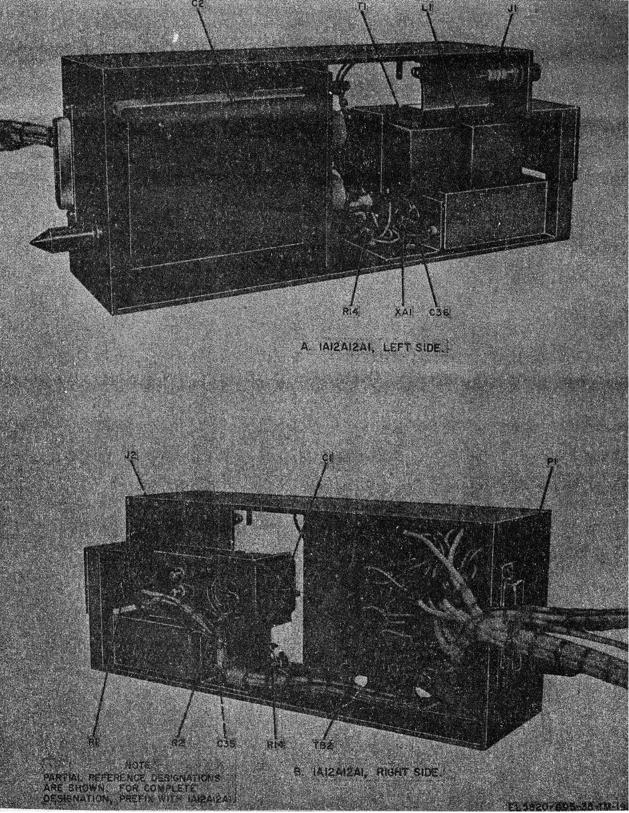

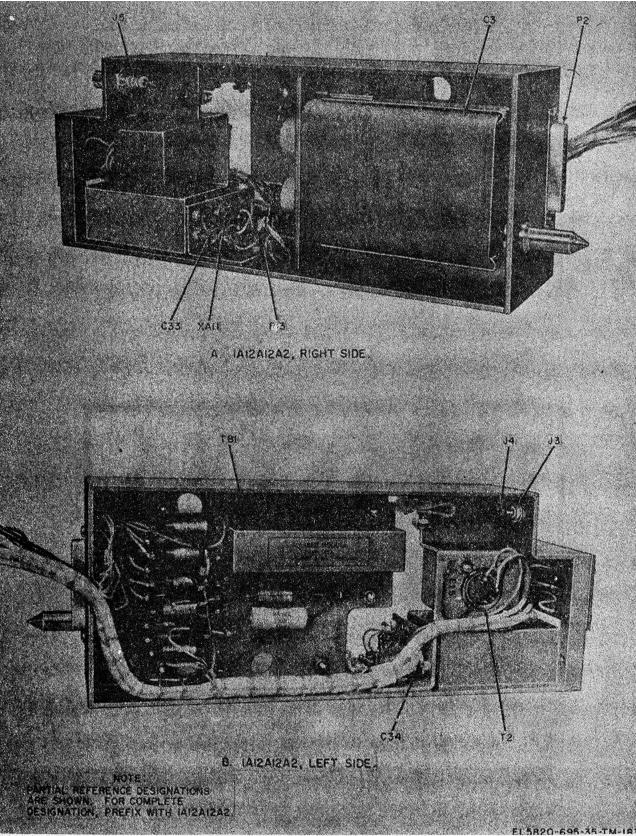

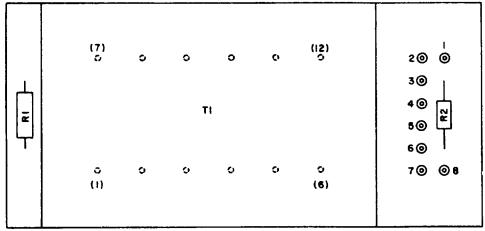

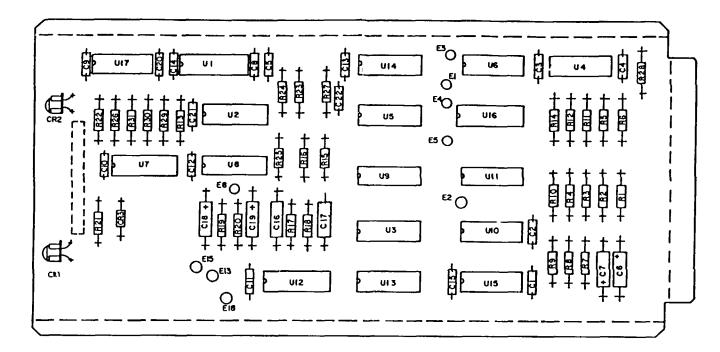

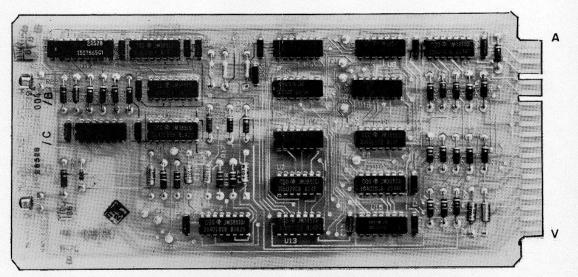

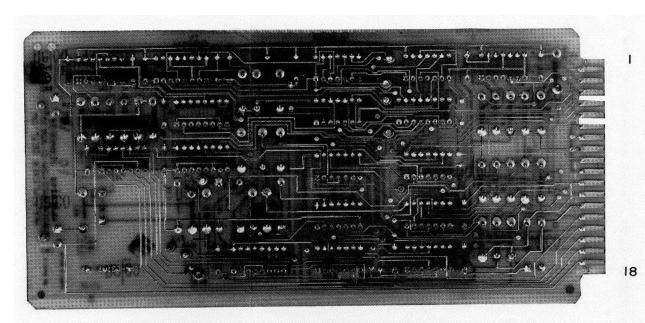

| 4-15                    | Digital data modem chassis 1A12A12 parts location<br>Digital data modem chassis assembly 1A12A12A1 parts | 4-21           |

|                         | location                                                                                                 | 4-22           |

| 4-17                    | Digital data modem chassis assembly 1A12A12A1 parts                                                      | 4-23           |

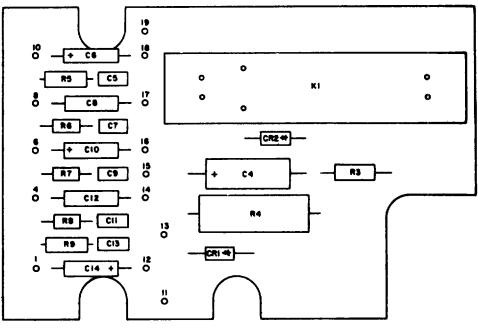

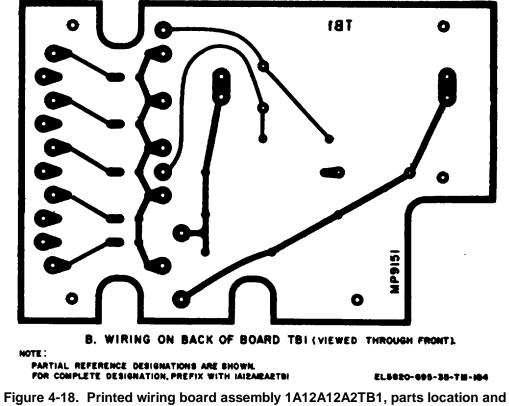

| 4-18                    | location<br>Printed wiring board assembly 1A12A12A2TB1 parts                                             | -              |

| 4-19                    | location and printed wiring diagram<br>Printed wiring board assembly 1A12A12A2TB2 parts                  | 4-24           |

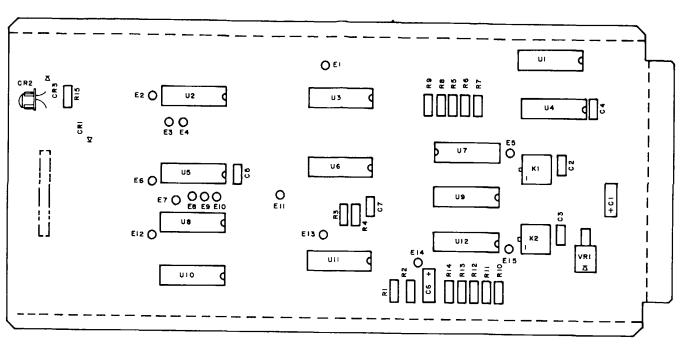

| 4-20                    | location and printed wiring diagram<br>Orderwire chassis 1A13A7 partially disassembled                   | 4-25           |

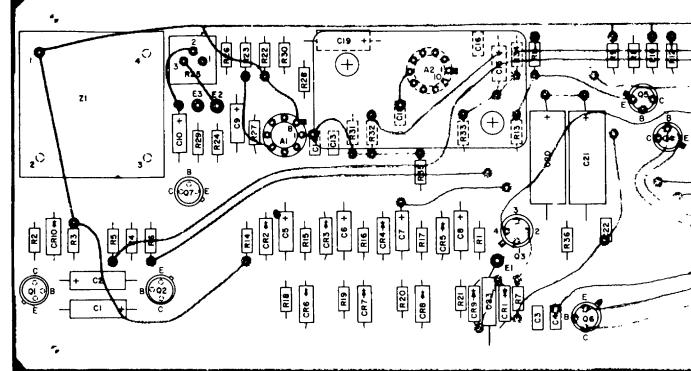

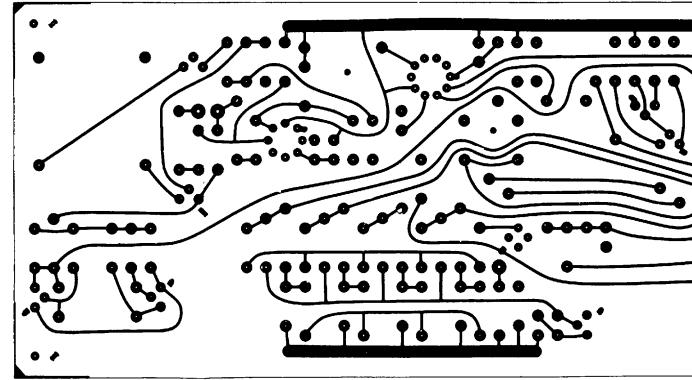

| 4-21                    | parts location<br>Printed wiring board assembly 1A13A7TB1, parts                                         | 4-26           |

|                         | location and printed wiring diagram                                                                      | 4-27           |

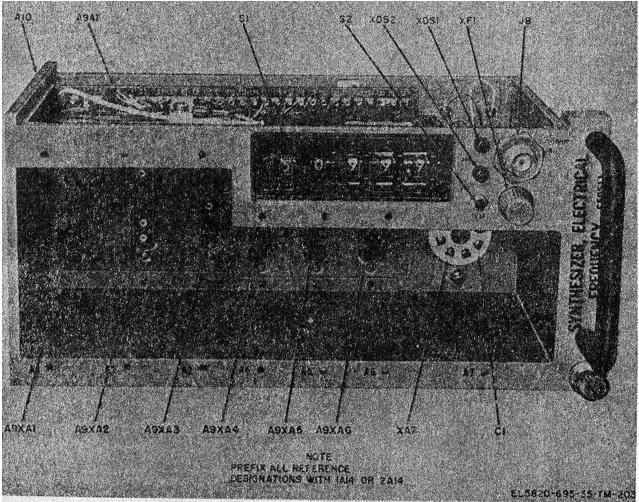

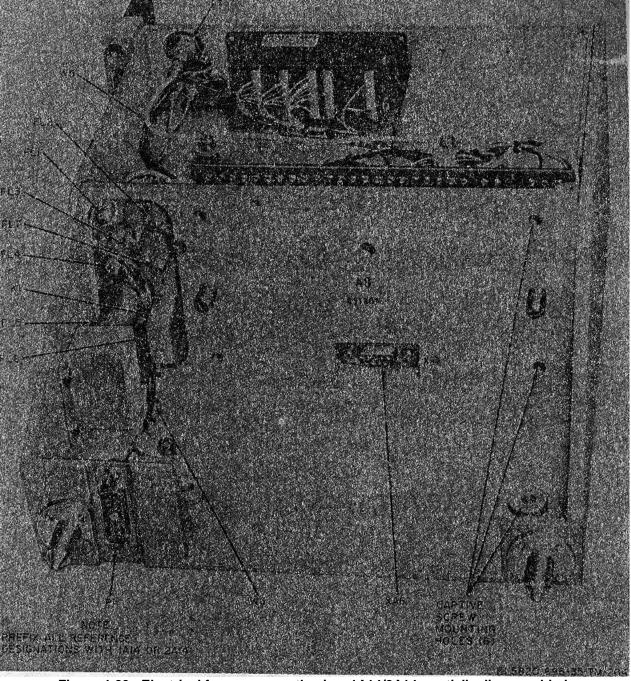

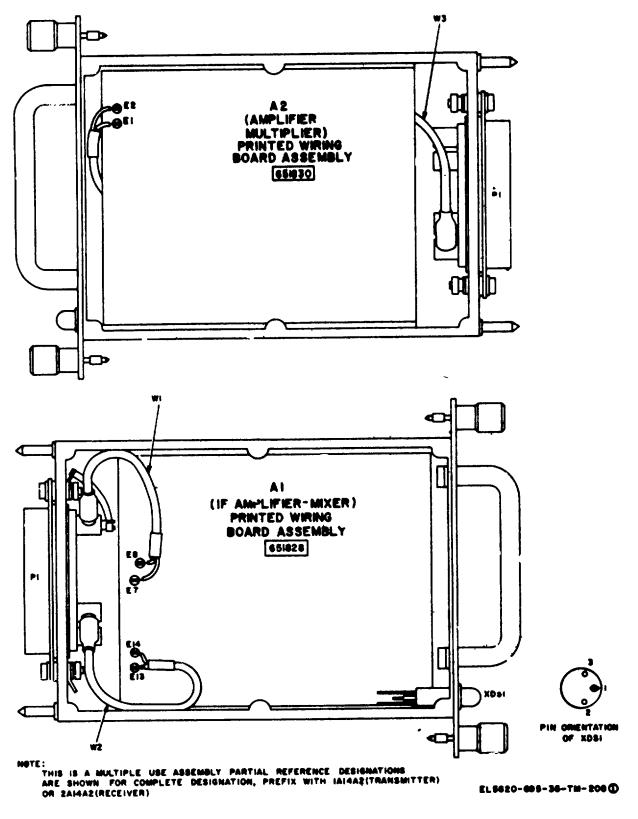

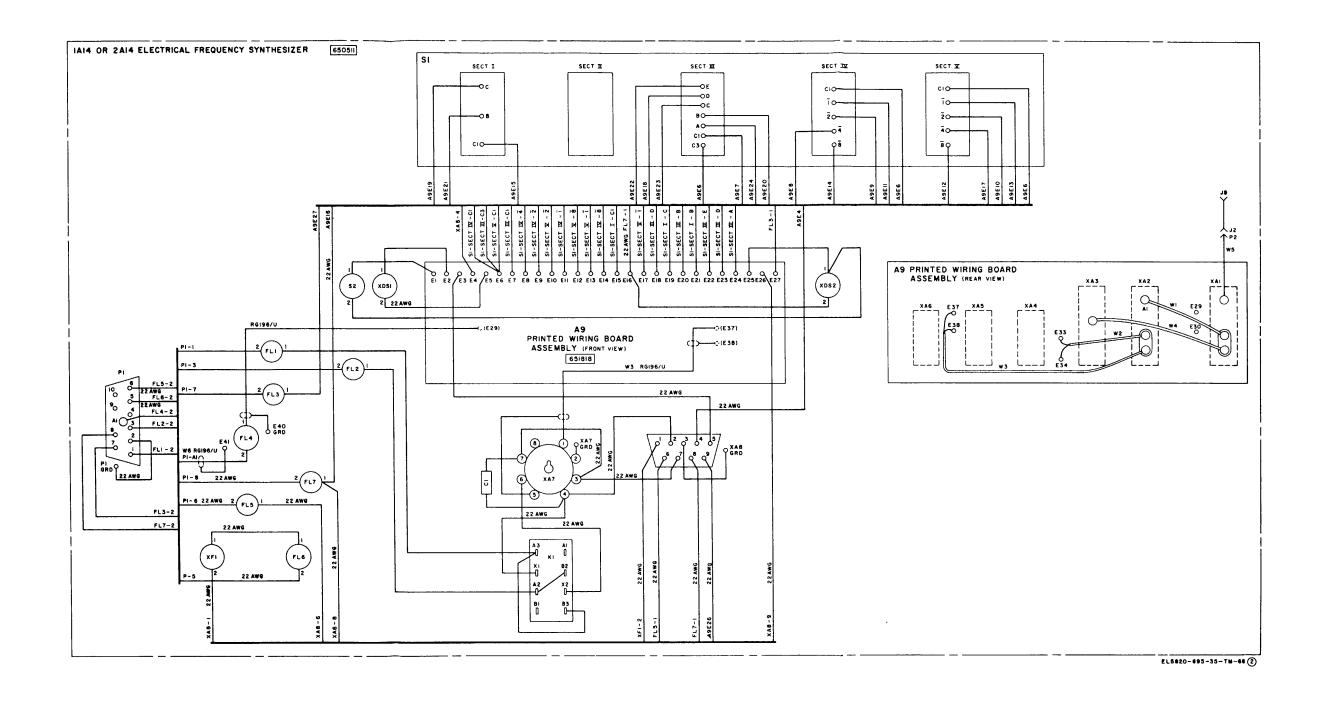

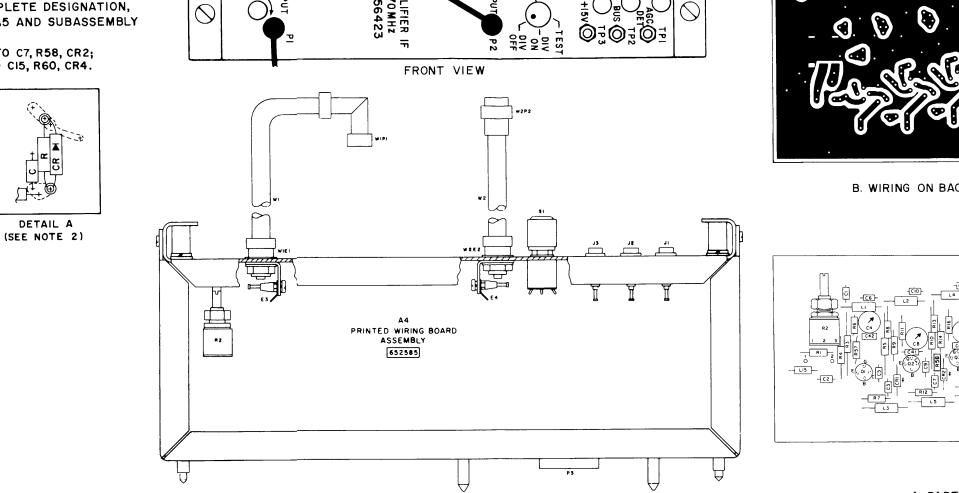

| 4-22                    | Electrical frequency synthesizer 1A14/2A14, partially<br>disassembled, front view parts location         | 4-28           |

| 4-23                    | Electrical frequency synthesizer 1A14/2A14, partially<br>disassembled rear view parts location           | 4-29           |

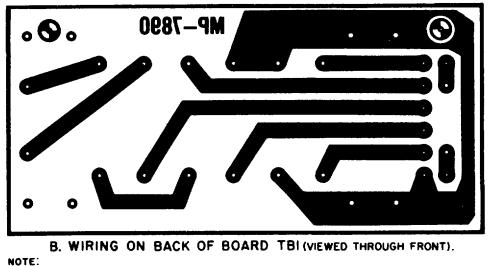

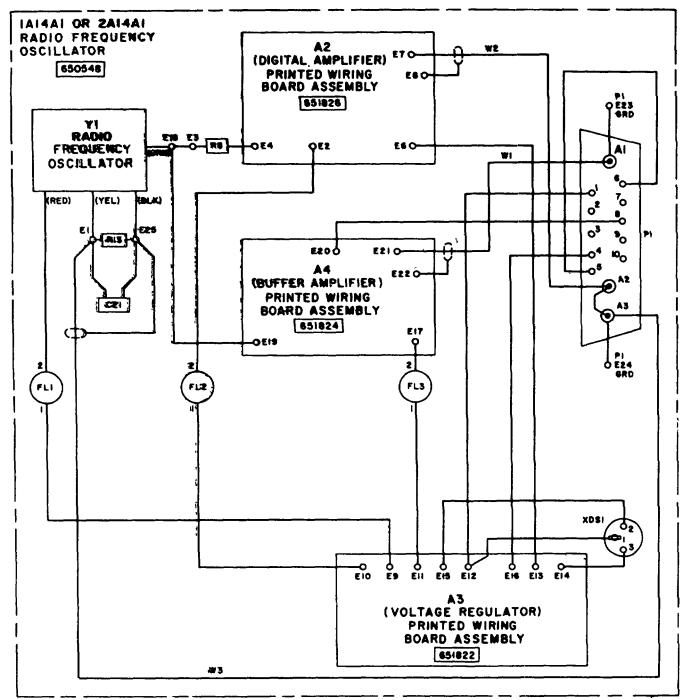

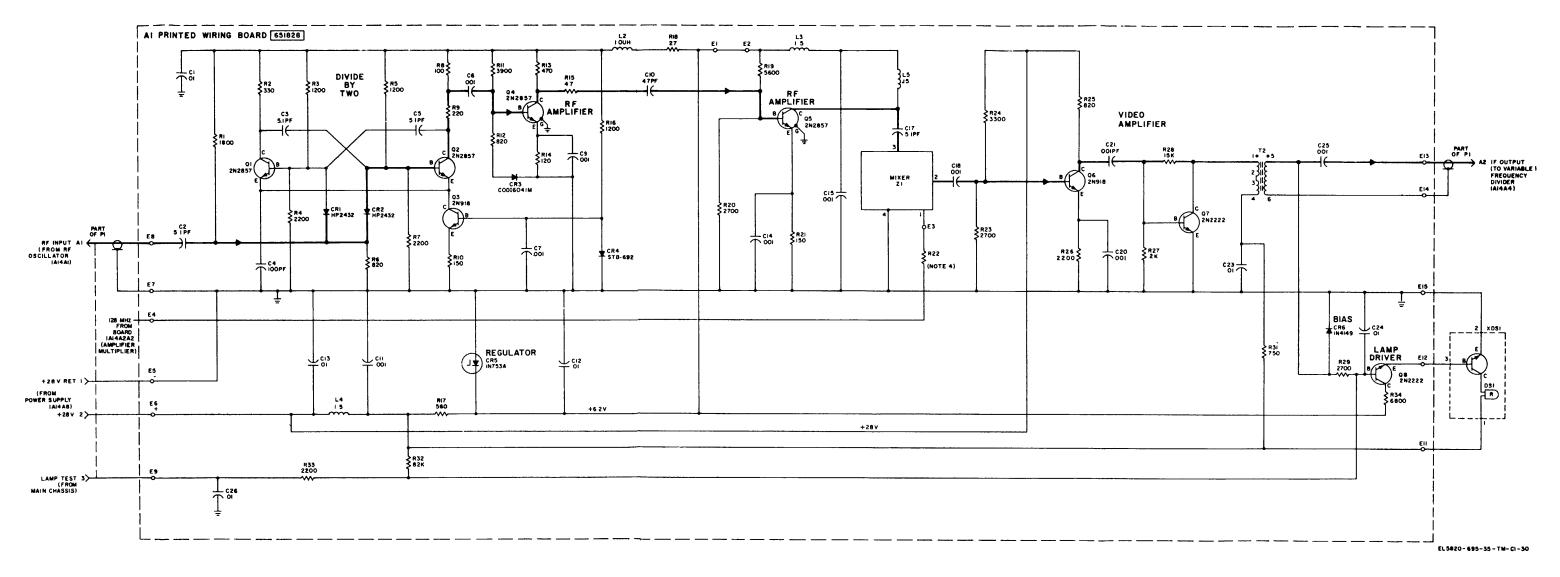

| 4-24                    | Radio frequency oscillator 1A14A1/2A14A1, wiring diagram                                                 | 4-30           |

| 4-250                   | Radio frequency oscillator 1A14A1/2A14A1, parts<br>location and printed wiring diagram (Part 1 of 4)     | 4-31           |

|                         |                                                                                                          | 4-31           |

| Figure<br><u>Number</u> | Title                                                                                                                               | Page             |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 4-25(2)                 | Radio frequency oscillator 1A14A1/2A14A1, parts<br>location and printed wiring diagram (Part 2 of 4)                                | 4-32             |

| 4-25(3)                 | Radio frequency oscillator 1A14A1/2A14A1 parts<br>location and printed wiring diagram (Part 3 of 4)                                 | 4-33             |

| 4-25(4)                 | Radio frequency oscillator 1A14A1/2A14A1 parts<br>location and printed wiring diagram (Part 4 of 4)                                 |                  |

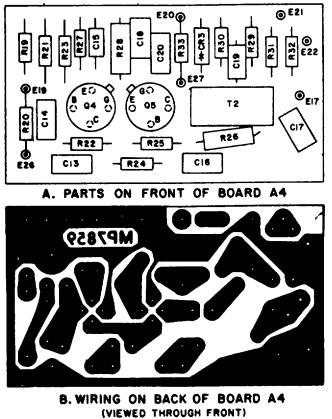

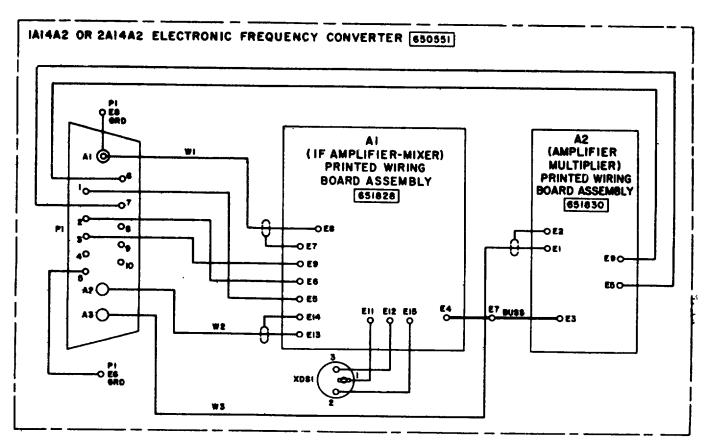

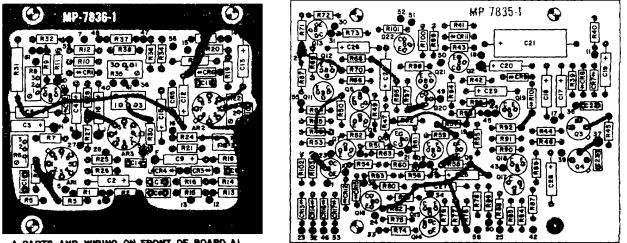

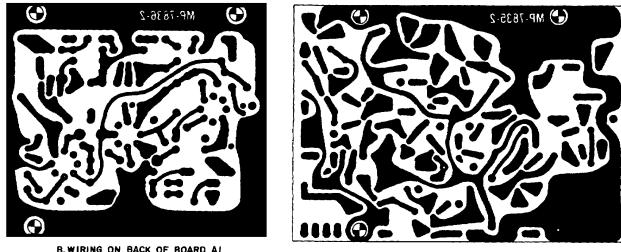

| 4-26                    | Electronic frequency converter 1A14A2/2A14A2                                                                                        | 4-33             |

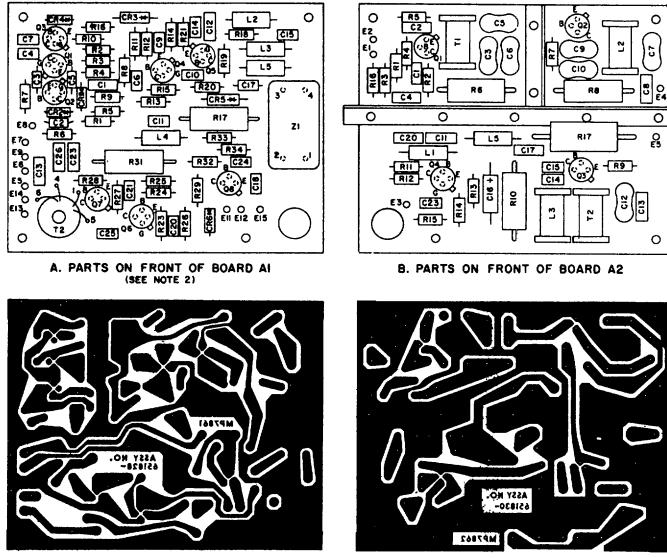

| 4-27(1)                 | wiring diagram<br>Electronic frequency converter 1A14A2/2A14A2, parts                                                               | 4-34             |

| 4-27(2)                 | location and printed wiring diagram (Part 1 of 2)<br>Electronic frequency converter 1A14A2/2A14A2 parts                             | 4-35             |

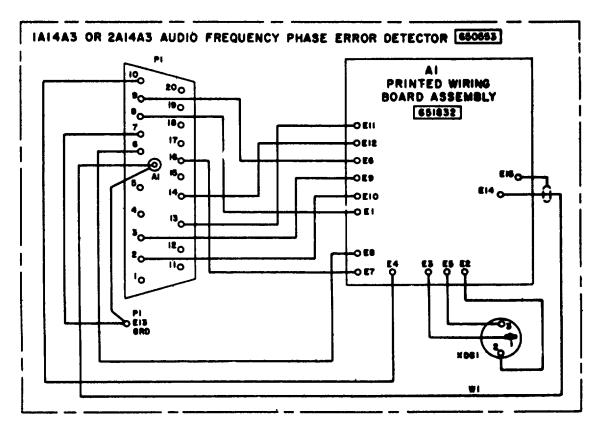

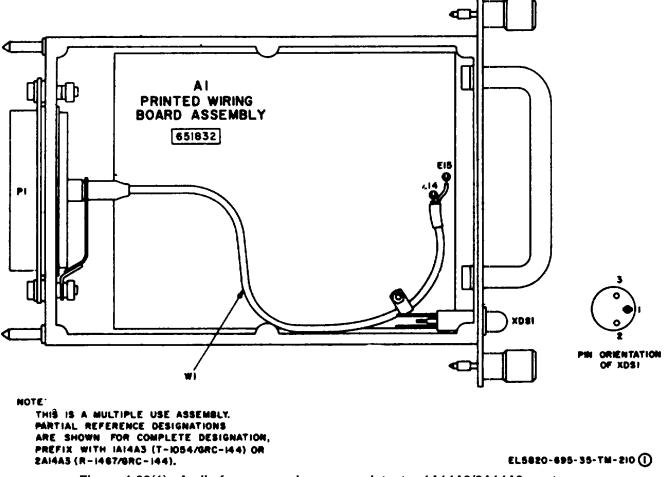

| 4-28                    | location and printed wiring diagram (Part 2 of 2)<br>Audio frequency phase error detector 1A14A3/                                   | 4-36             |

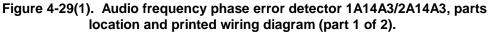

| 4-29(1)                 | 2A14A3 wiring diagram<br>Audio frequency phase error detector 1A14A3/<br>2A14A3, parts location and printed wiring diagram          | 4-37             |

| 4-29(2)                 | (Part 1 of 2)<br>Audio frequency phase error detector 1A14A3/<br>2A14A3, parts location and printed wiring diagram<br>(Part 2 of 2) | 4-38<br>4-39     |

| 4-30                    | Variable 1 frequency divider 1A14A4/2A14A4 wiring<br>diagram                                                                        | 4-39             |

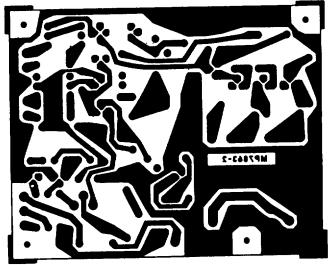

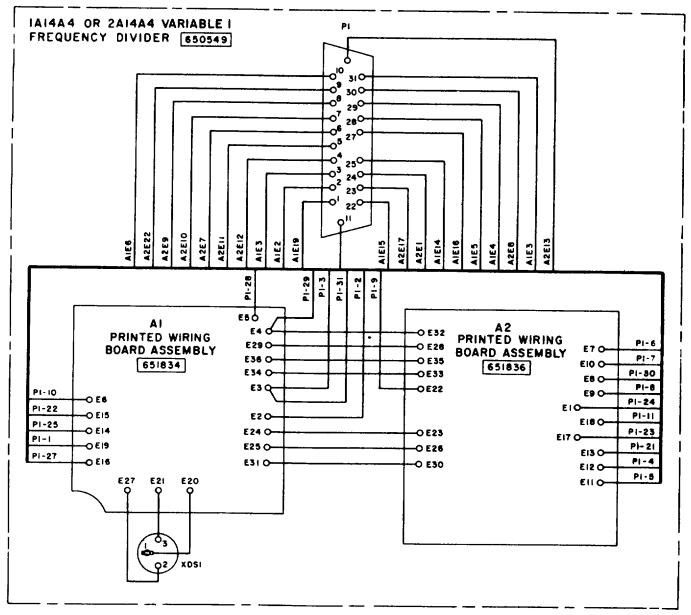

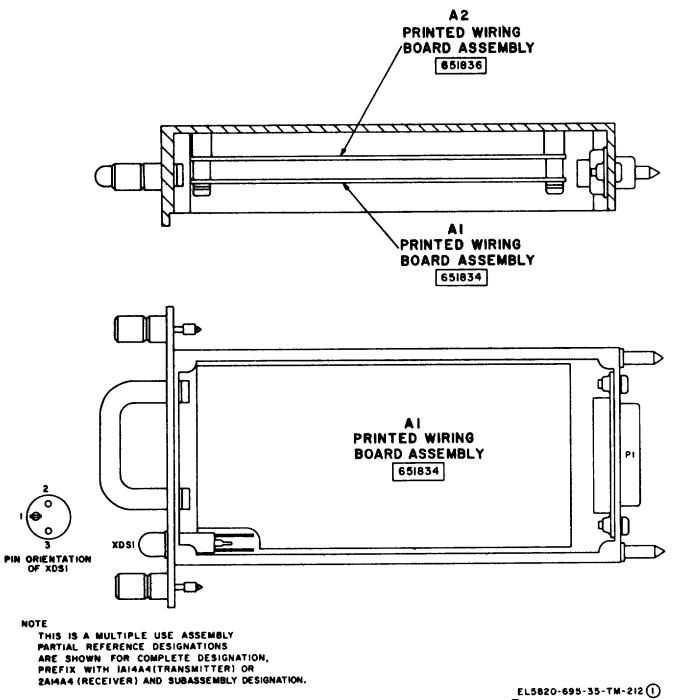

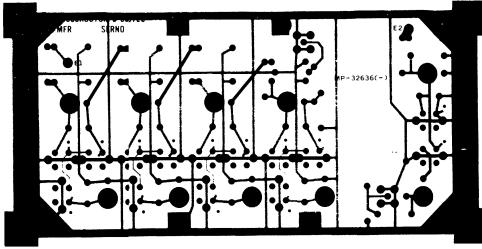

| 4-31(1)                 | Variable 1 frequency divider 1A14A4/2A14A4, parts<br>location and printed wiring diagram (Part 1 of 3)                              | 4-40             |

| 4-31(2)                 | Variable 1 frequency divider 1A14A4/2A14A4, parts<br>location and printed wiring diagram (Part 2 of 3)                              | 4-42             |

| 4-31(3)                 | Variable 1 frequency divider 1A14A4/2A14A4, parts<br>location and printed wiring diagram (Part 3 of 3)                              | 4-42             |

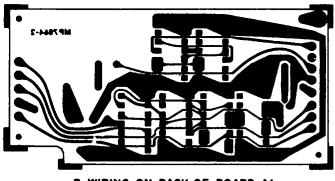

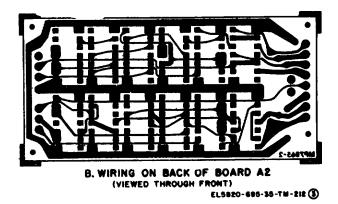

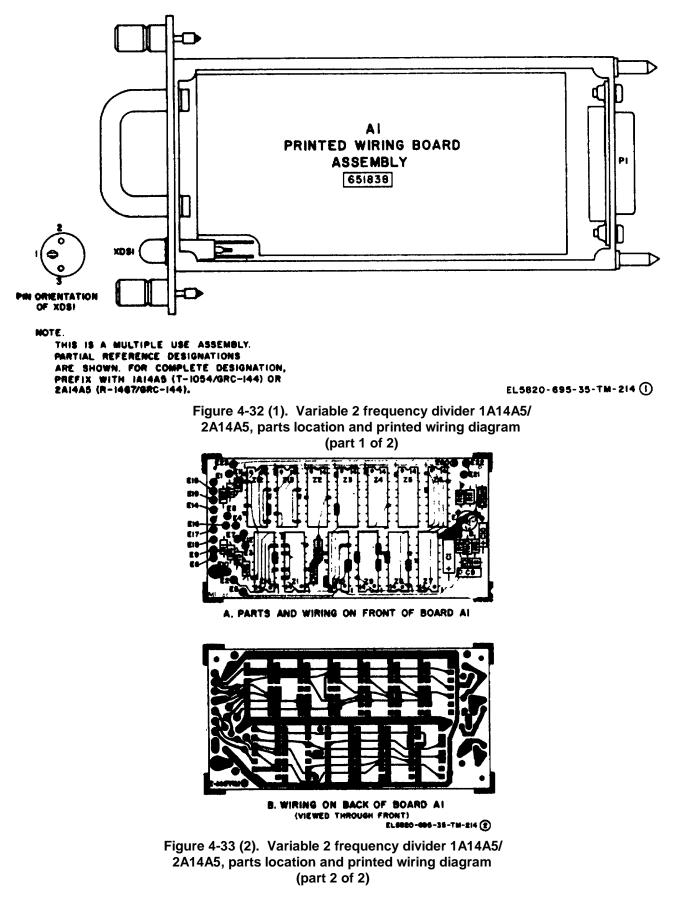

| 4-32                    | Variable 2 frequency divider 1A14A5/2A14A5 wiring<br>diagram                                                                        | 4-43             |

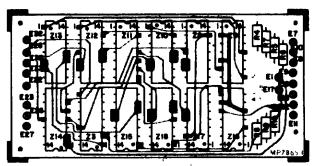

| 4-33(1)                 | Variable 2 frequency divider 1A14A5/2A14A5 parts<br>Location and printed wiring diagram (Part 1 of 2)                               | 4-44             |

| 4-33(2)                 | Variable 2 frequency divider 1A14A5/2A14A5 parts<br>location and printed wiring diagram (Part 2 of 2)                               | 4-44             |

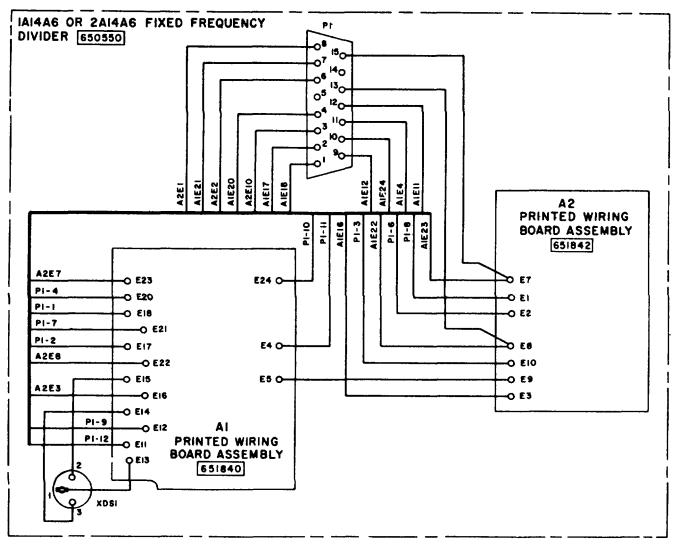

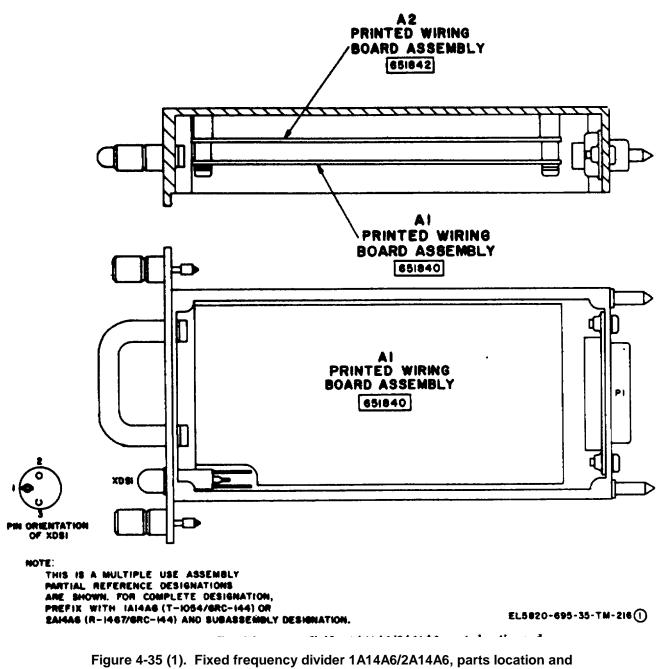

| 4-34<br>4-35(1)         | Fixed frequency divider 1A14A6/2A14A6 wiring diagram<br>Fixed frequency divider 1A14A6/2A14A6 parts location                        | 4-45             |

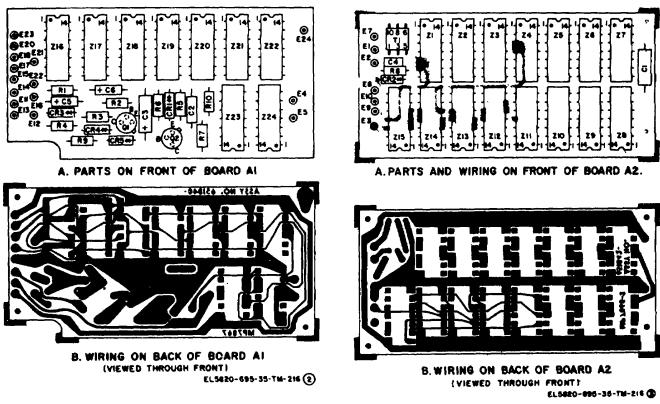

| 4-35(2)                 | and printed wiring diagram (Part 1 of 3)<br>Fixed frequency divider 1A14A6/2A14A6 parts location                                    | 4-46             |

|                         | and printed wiring diagram (Part 2 of 3)                                                                                            | 4-47             |

| 4-35(3)                 | Fixed frequency divider 1A14A6/2A14A6 parts location<br>and printed wiring diagram (Part 3 of 3)                                    | 4-47             |

| 4-36<br>4-36.1          | 1.0 MHz low pass filter 2A3 wiring diagram<br>3.8 MHz low pass filter 2A3 wiring diagram                                            | 4-47<br>4-48     |

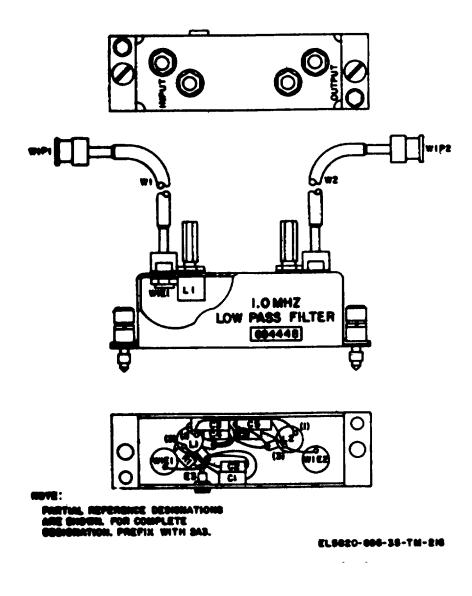

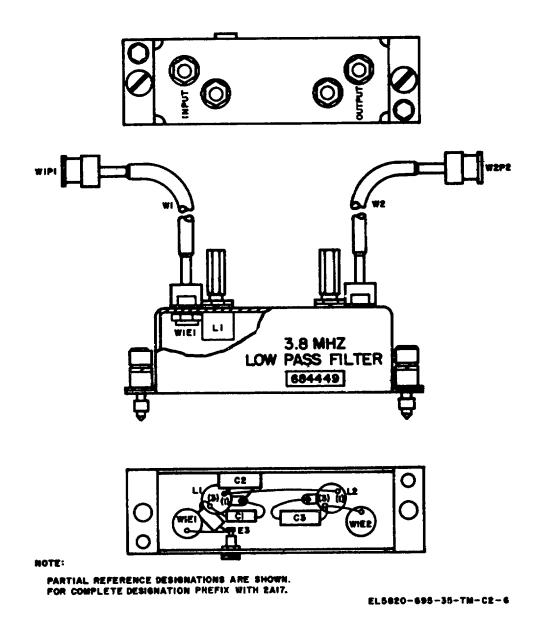

| 4-37<br>4-37.1          | 1.0 MHz low pass filter 2A3, parts location<br>3.8 MHz low pass filter 2A3, parts location                                          | 4-48.1<br>4-48.2 |

| 4-37.2                  | 5.3 MHz low pass filter 2A3 (956419), parts location<br>diagram                                                                     | 4-48.3           |

| 4-37.3                  | 13 MHz low pass filter 2A3 (956421), parts location<br>diagram                                                                      | 4-48.4           |

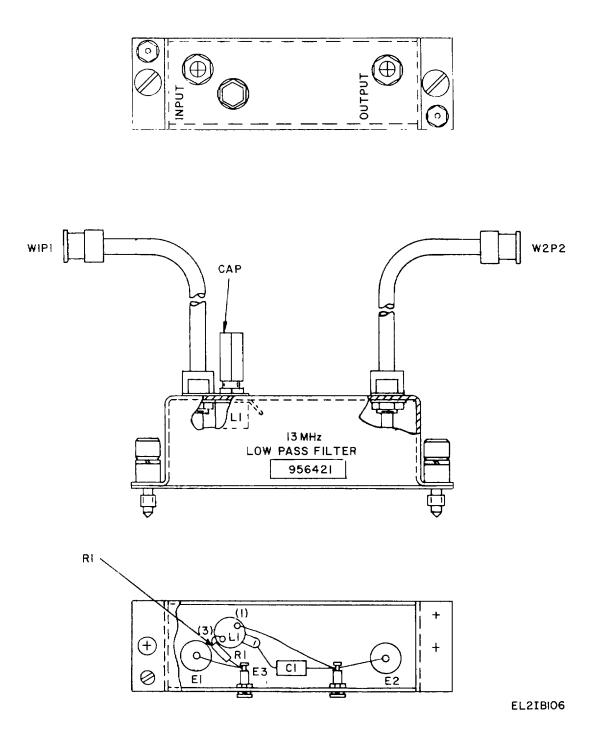

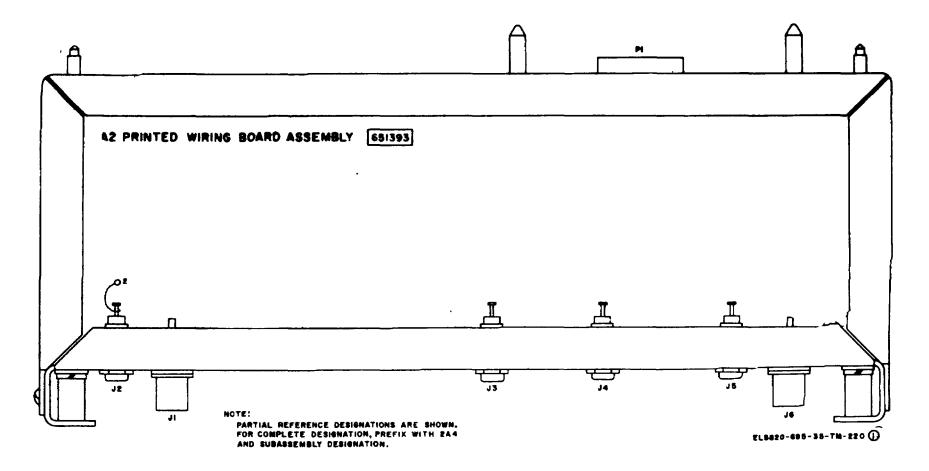

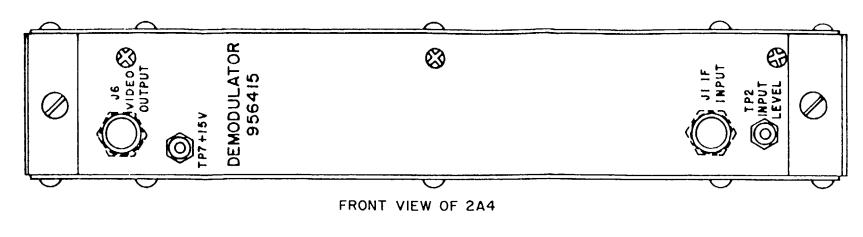

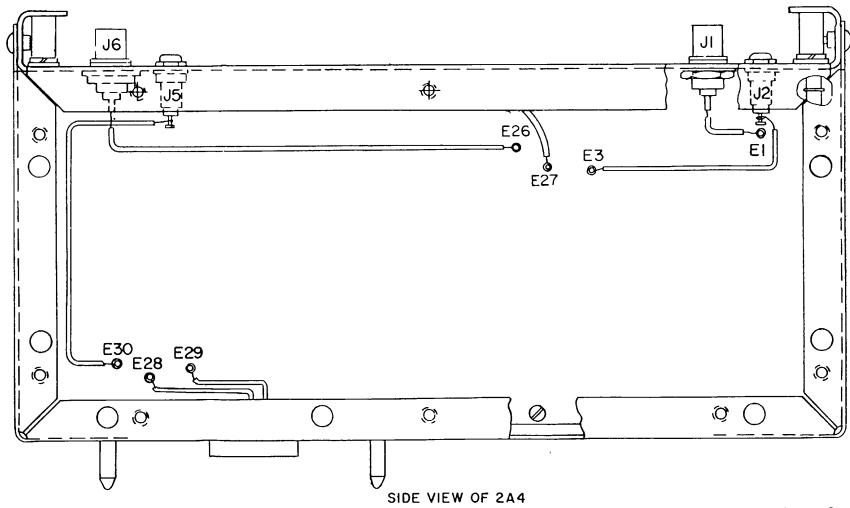

| 4-38                    | Demodulator 2A4 wiring diagram                                                                                                      | 4-49             |

| Figure                  | LIST OF ILLUSTRATIONS - Continued                                                                           |              |

|-------------------------|-------------------------------------------------------------------------------------------------------------|--------------|

| Figure<br><u>Number</u> | Title                                                                                                       | Page         |

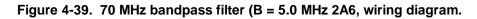

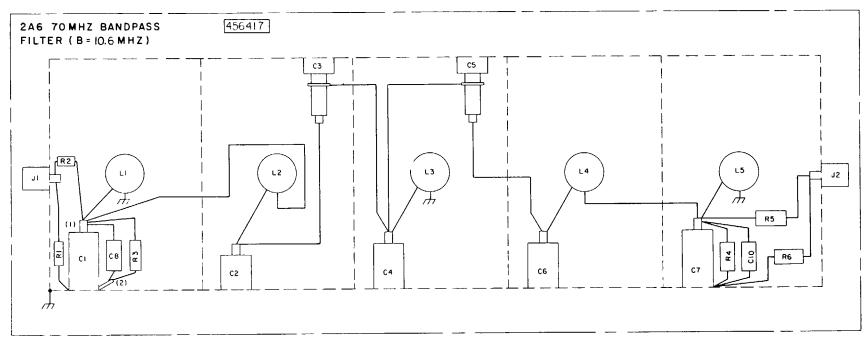

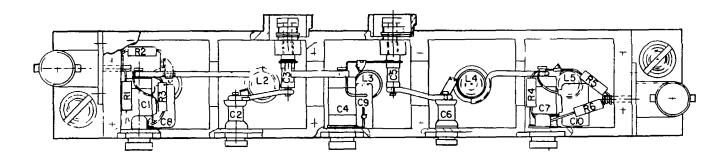

| 4-39<br>4-39.1          | 70 MHz band pass filter (B=5.0 MHz) 2A6 wiring diagram<br>70 MHz band pass filter (B=10.6 MHz) 2A6 (956417) | 4-50         |

| 4-39.2                  | wiring diagram<br>70 MHz band pass filter(B=10.6 MHz)12A6 (956417) parts                                    | 4-50.1       |

|                         | location/diagram,                                                                                           | 4-50.2       |

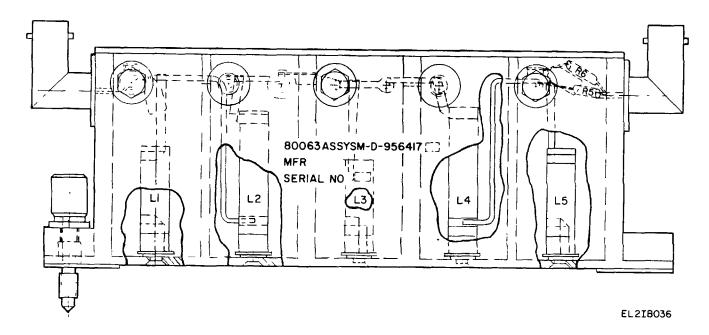

| 4-40                    | 70 MHz band pass filter (B=5.0 MHz) 2A6, parts<br>location                                                  | 4-51         |

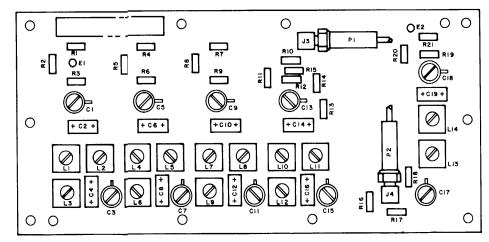

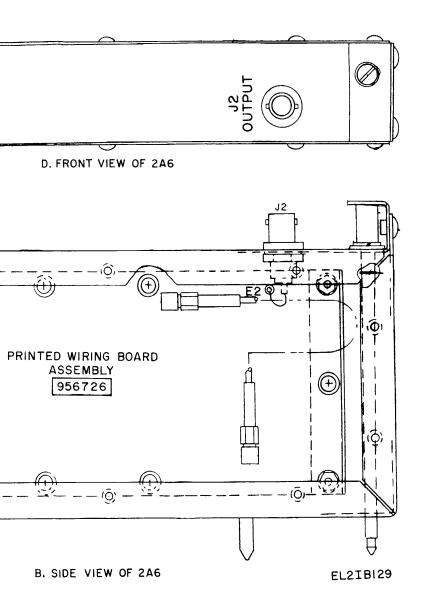

| 4-41(1)                 | Amplifier-mixer 2A7, parts location and printed wiring<br>diagram (Part 1 of 2)                             | 4-52         |

| 4-41(2)                 | Amplifier-mixer 2A7, parts location and printed wiring<br>diagram (Part 2 of 2)                             | 4-53         |

| 4-41.1                  | Amplifier mixer 2A7 (956425), parts location and printed wiring diagram                                     | 4-52.1       |

| 4-42                    | Receiver frequency mixer stage 2A8, wiring diagram                                                          | 4-54         |

| 4-42                    |                                                                                                             | 4-54<br>4-55 |

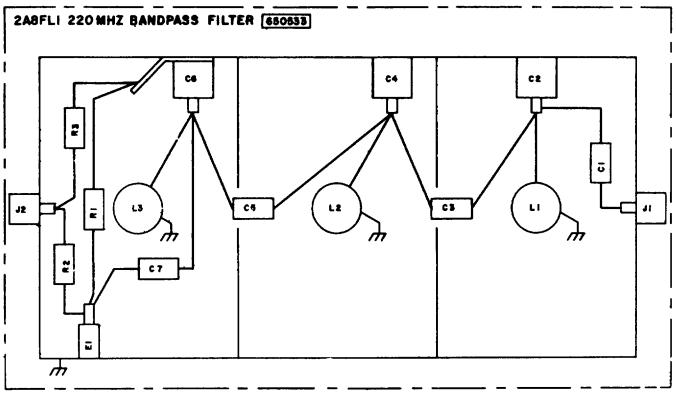

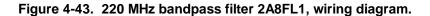

| 4-43<br>4-44            | 220 MHz bandpass filter 2A8FL1, wiring diagram                                                              |              |

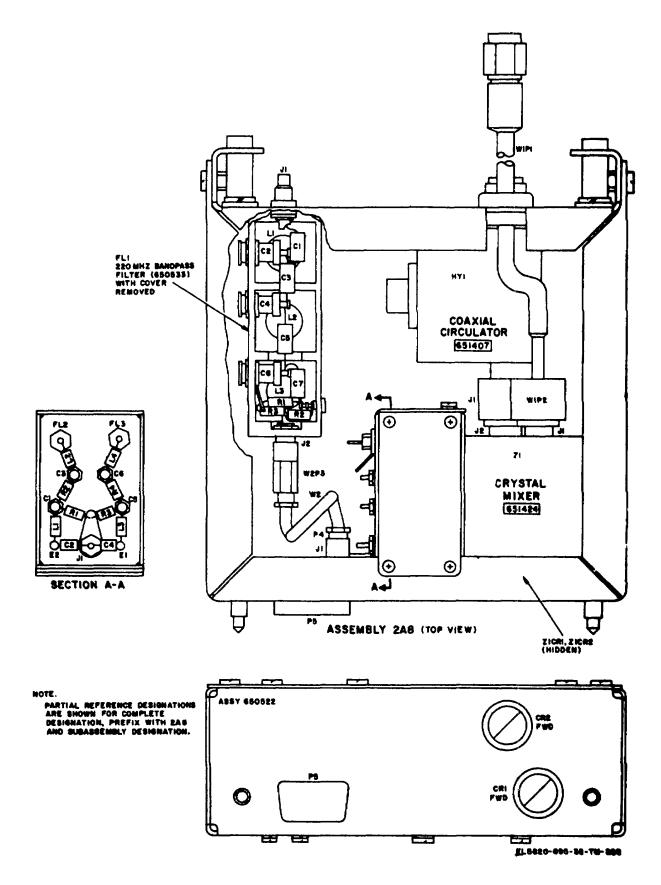

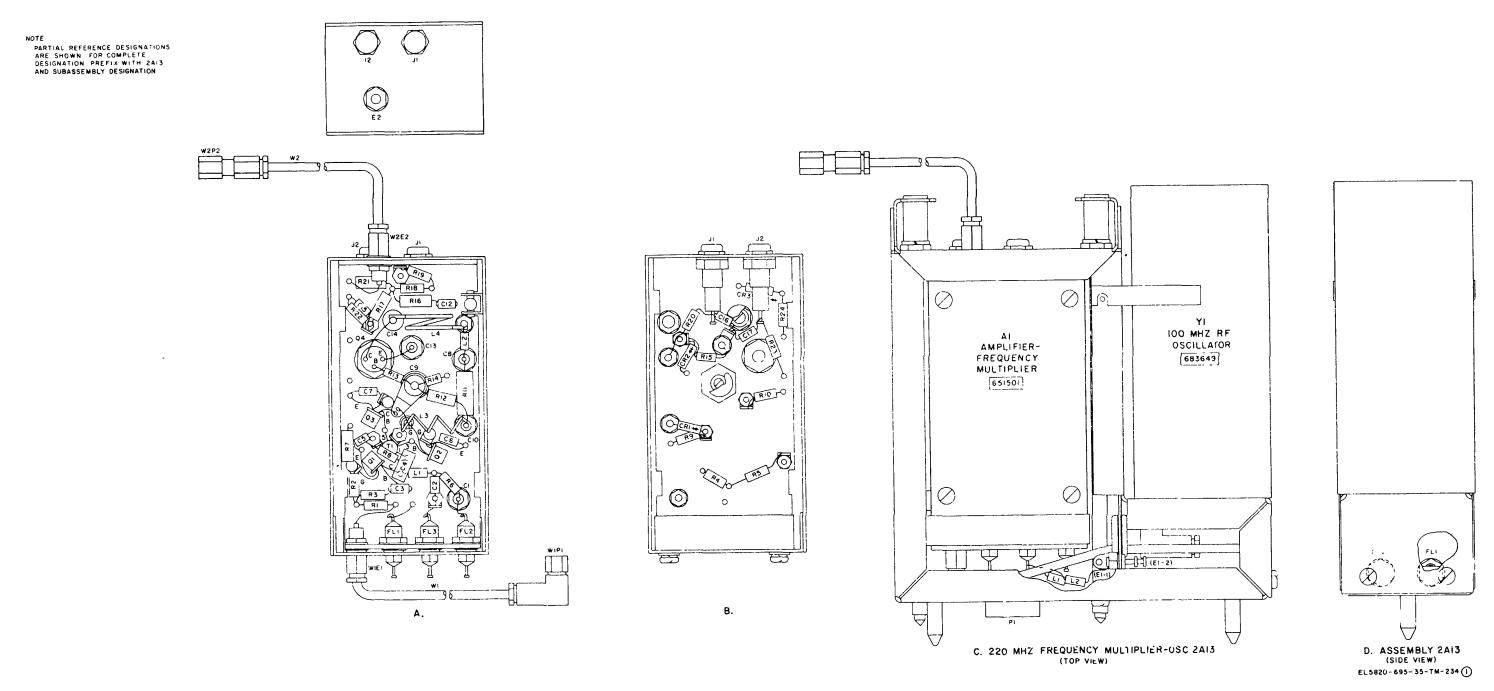

| 4-44<br>4-45            | Receiver frequency mixer stage 2A8, parts location<br>220 MHz frequency multiplier-OSC 2A13, wiring         | 4-56<br>4-57 |

| 4.46                    | diagram                                                                                                     |              |

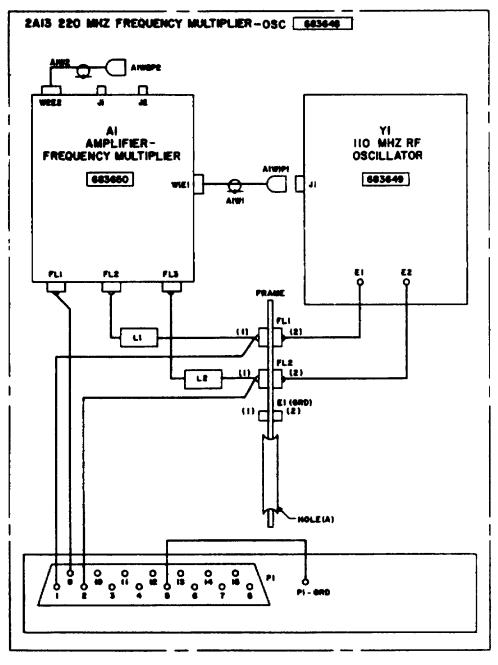

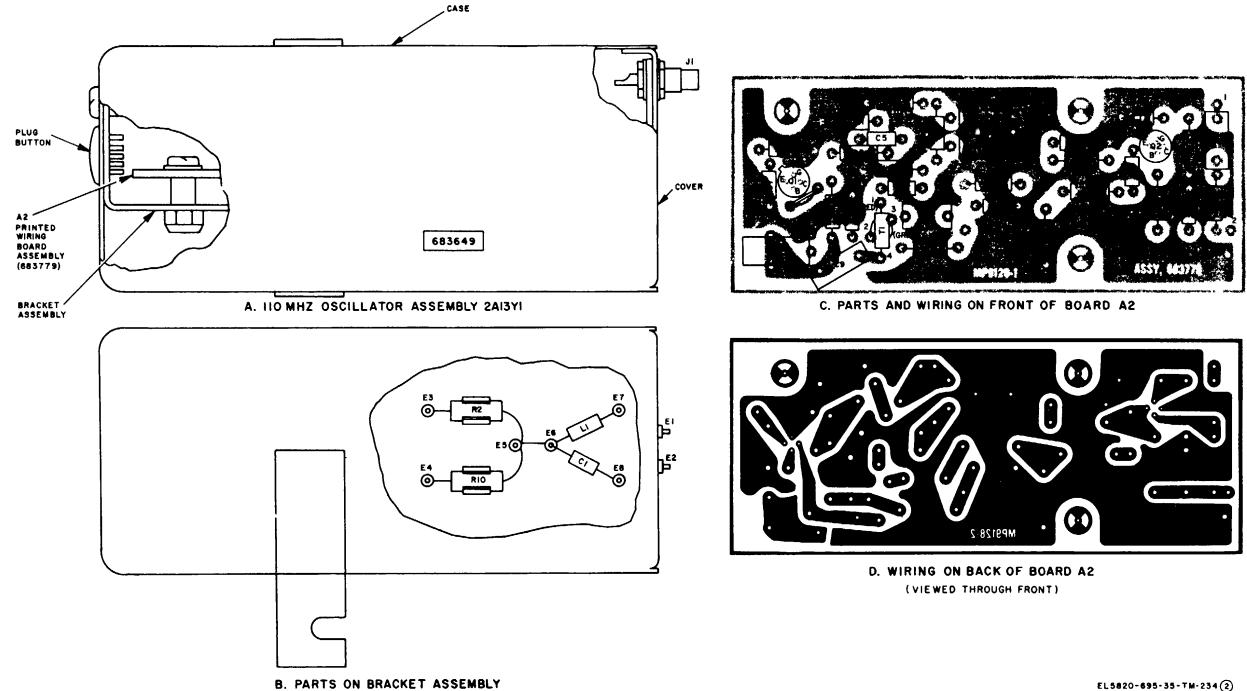

| 4-46                    | 110 MHz RF oscillator 2A13Y1, wiring diagram                                                                | 4-58         |

| 4-47                    | Indicator, Antenna Alignment ID-1708/GRC, wiring<br>diagram                                                 | 4-59         |

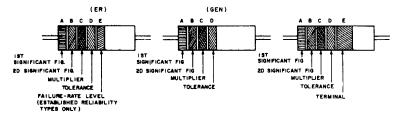

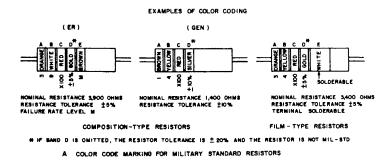

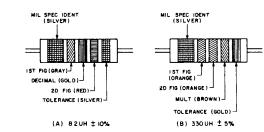

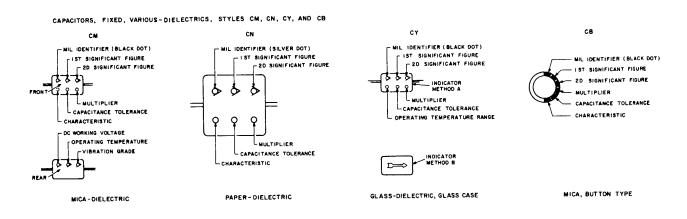

| 5-1                     | Color code marking for MIL-STD resistors, inductors,<br>and capacitors                                      | 5-3          |

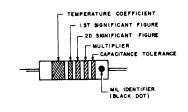

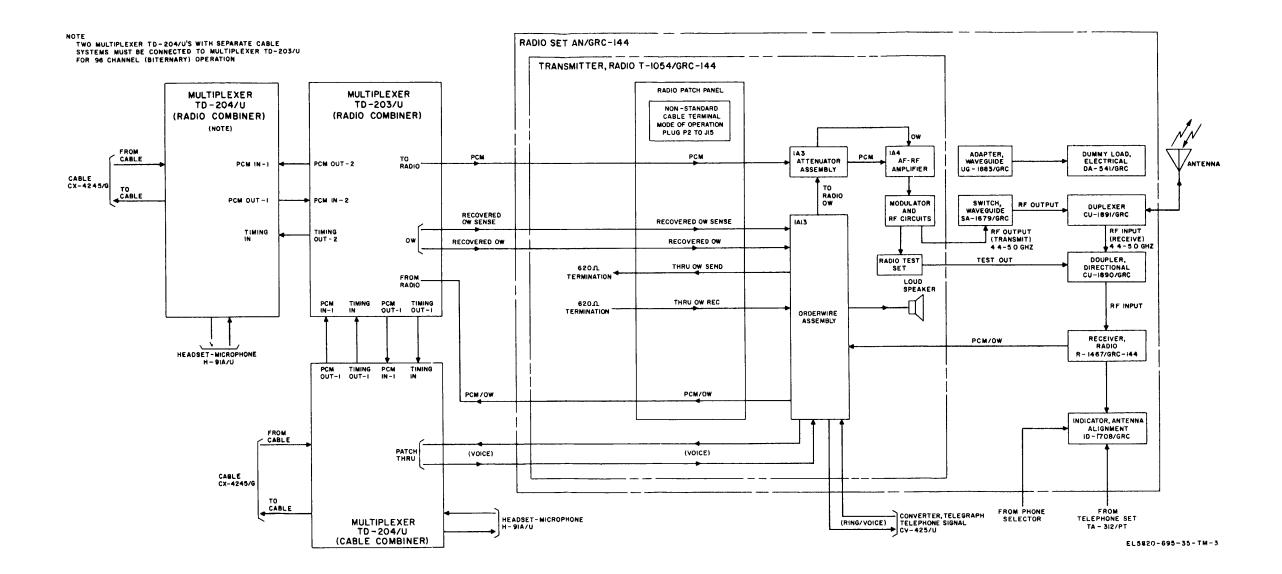

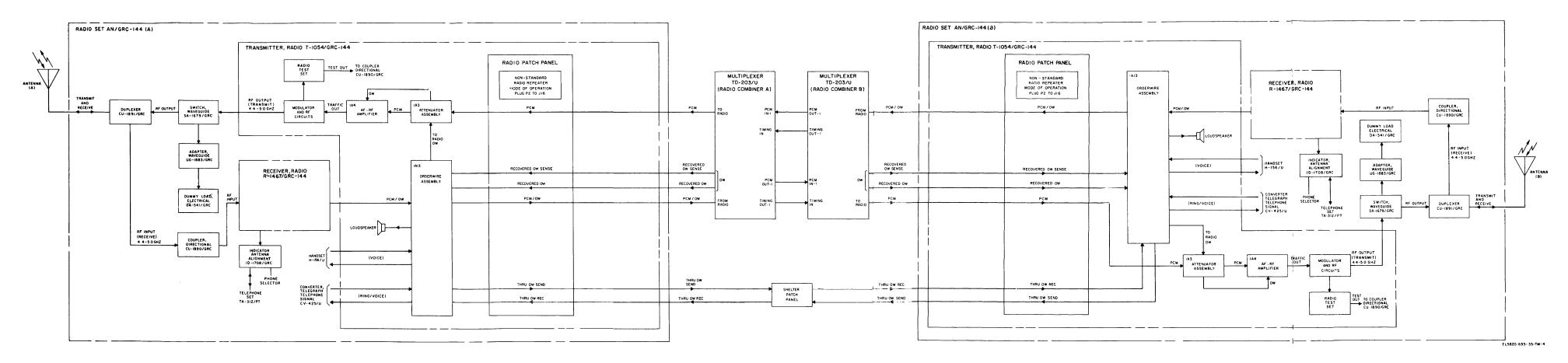

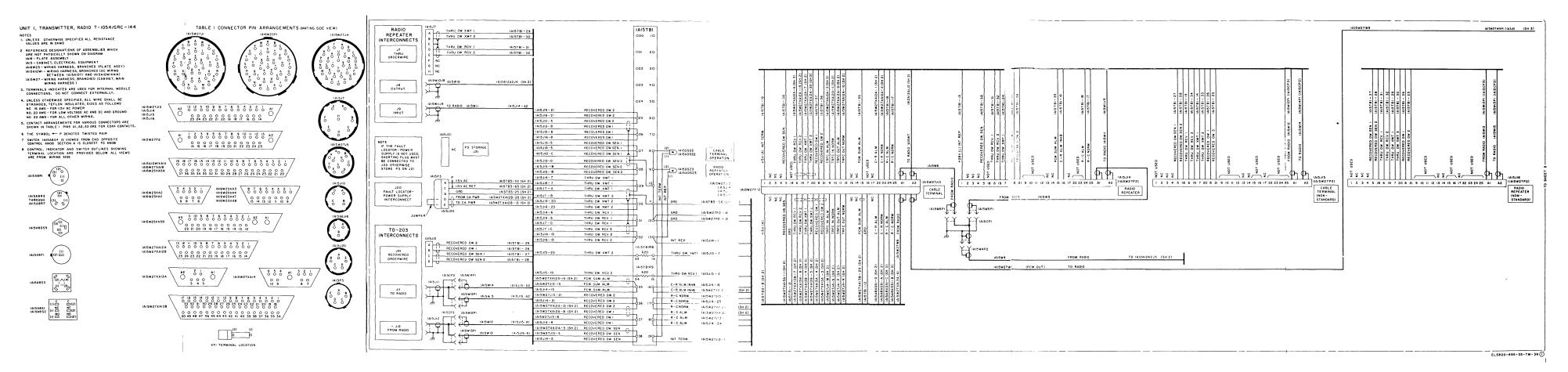

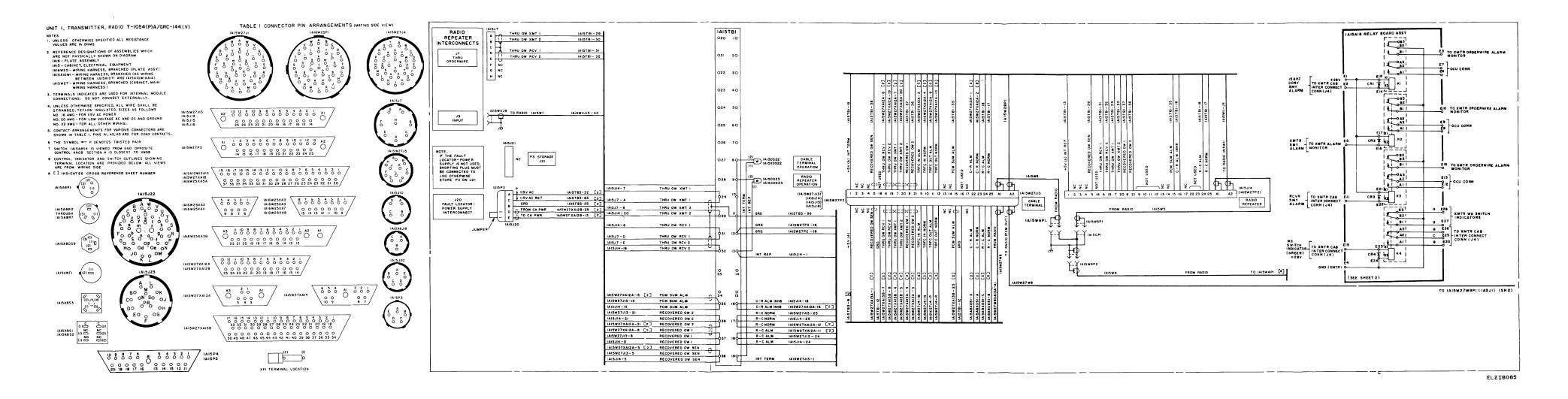

| 5-2                     | AN/GRC-144(V) and AN/GRC-144(V)3 standard cable<br>terminal block diagram                                   | 5-5          |

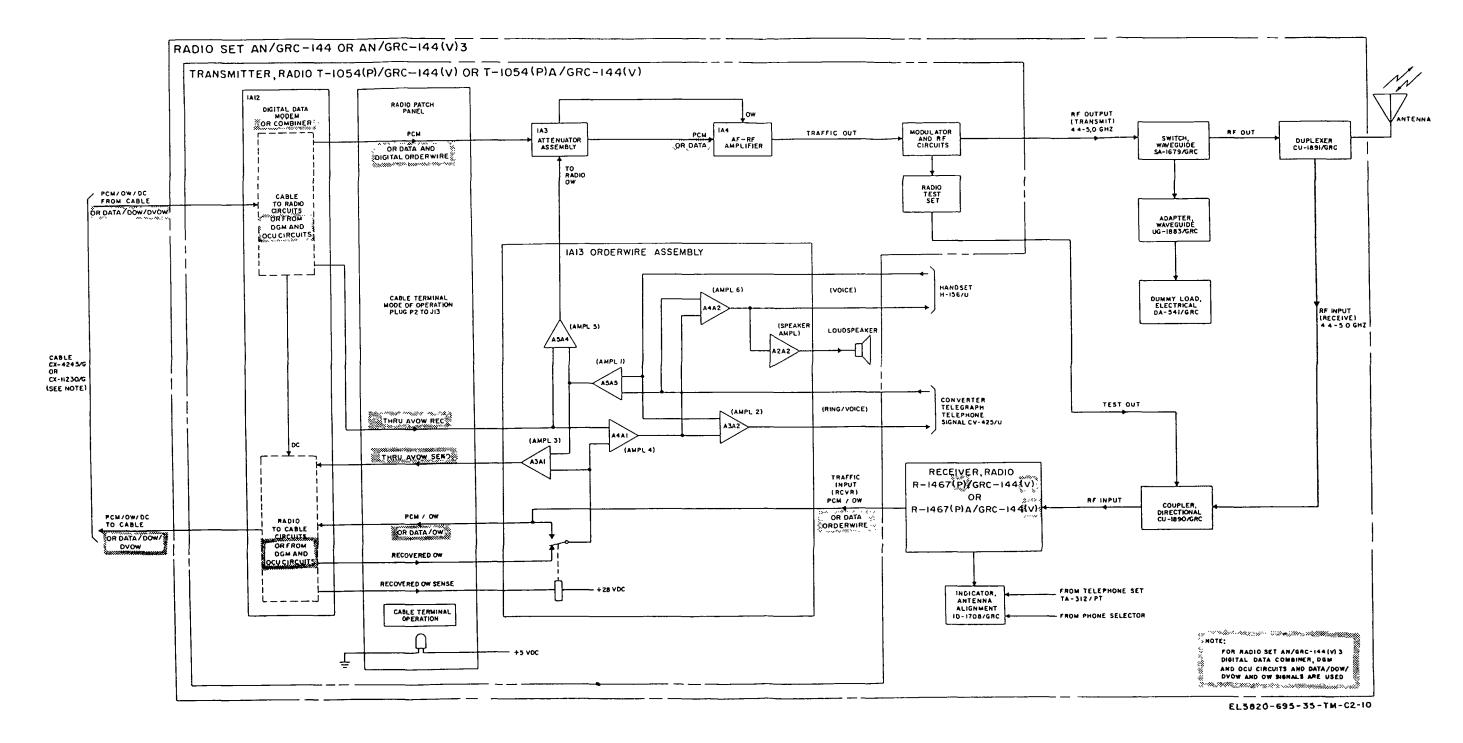

| 5-2.1                   | AN/GRC-144(V)4 standard cable terminal configuration<br>block diagram                                       | 5-5.1        |

| 5-3                     | AN/GRC-144 nonstandard cable terminal configuration,                                                        |              |

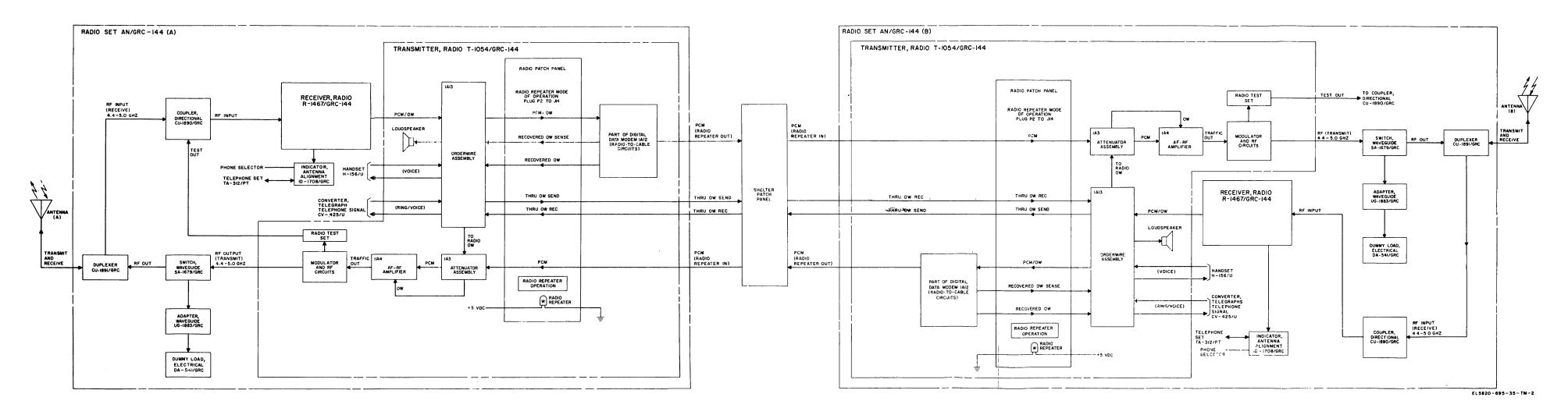

| 5-4                     | block diagram<br>AN/GRC-144 standard radio repeater configuration,                                          | 5-7          |

| 5-5                     | block diagram<br>AN/GRC-144 nonstandard radio repeater configuration,                                       | 5-9          |

|                         | block diagram                                                                                               | 5-11         |

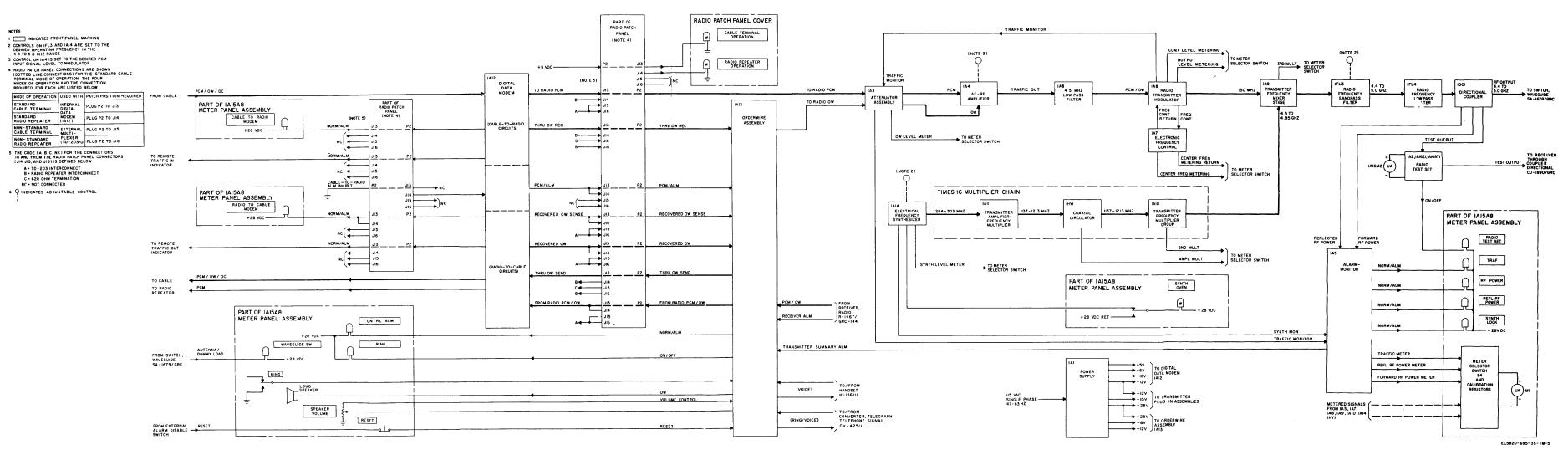

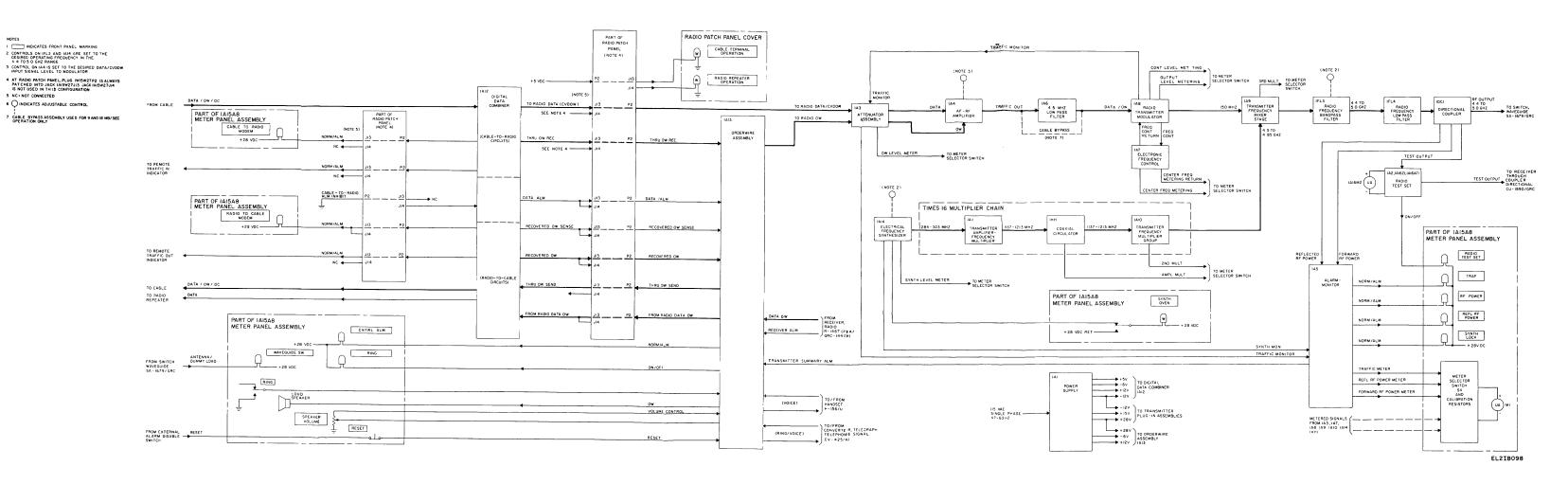

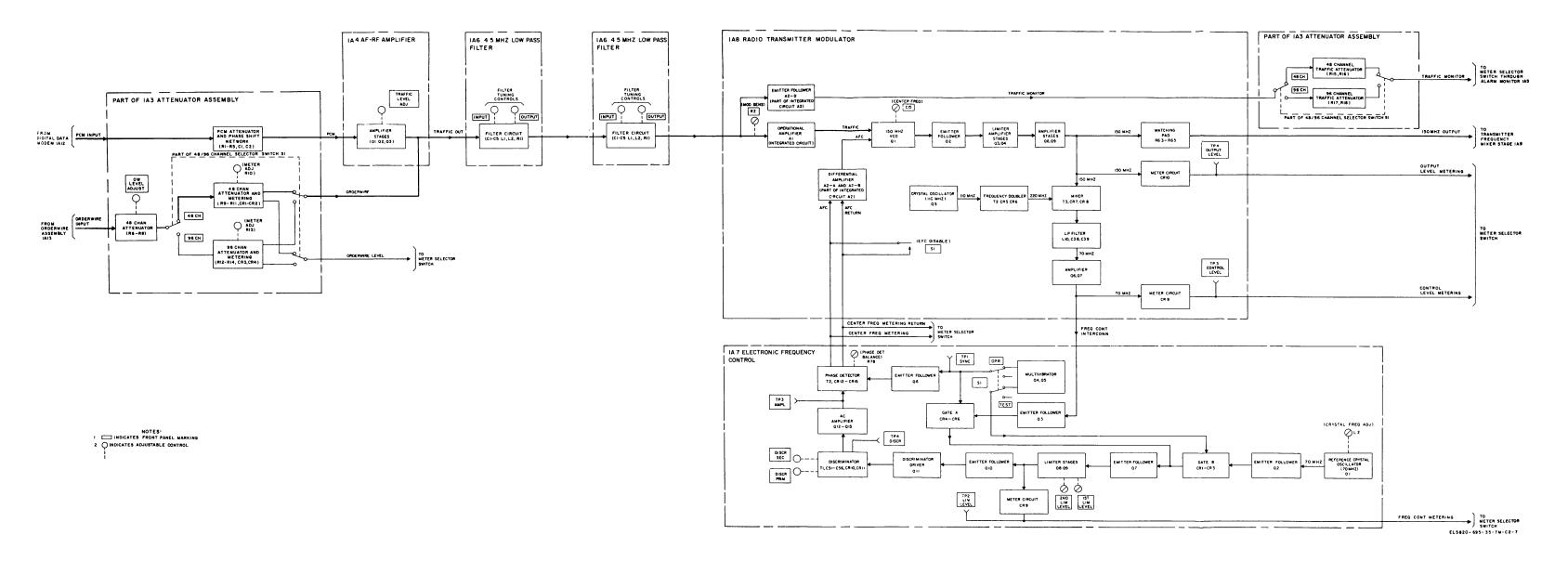

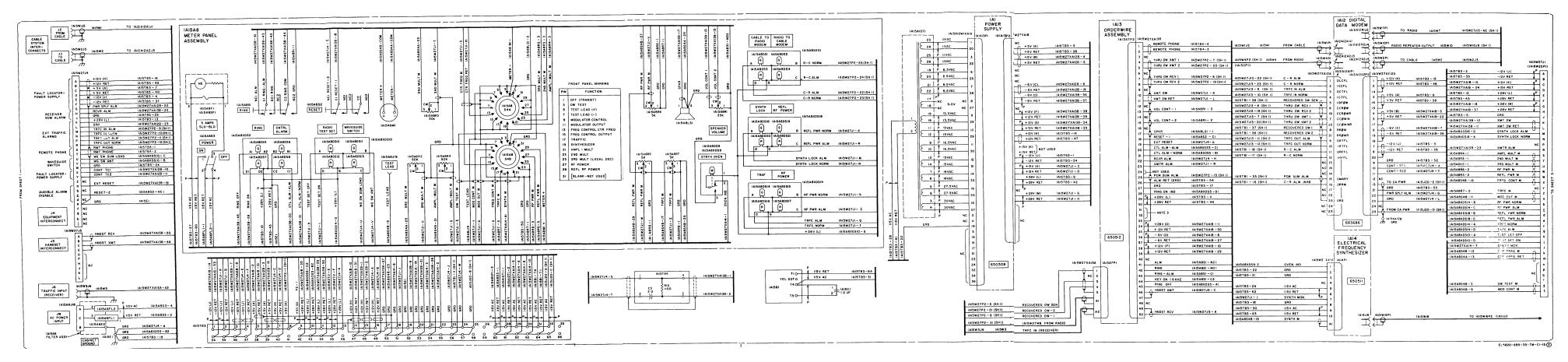

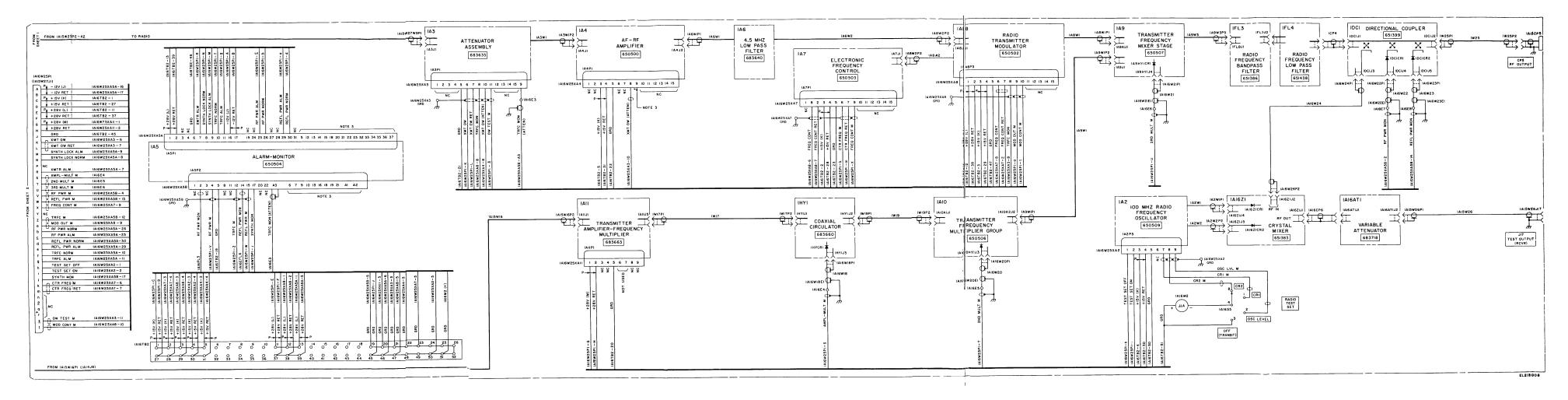

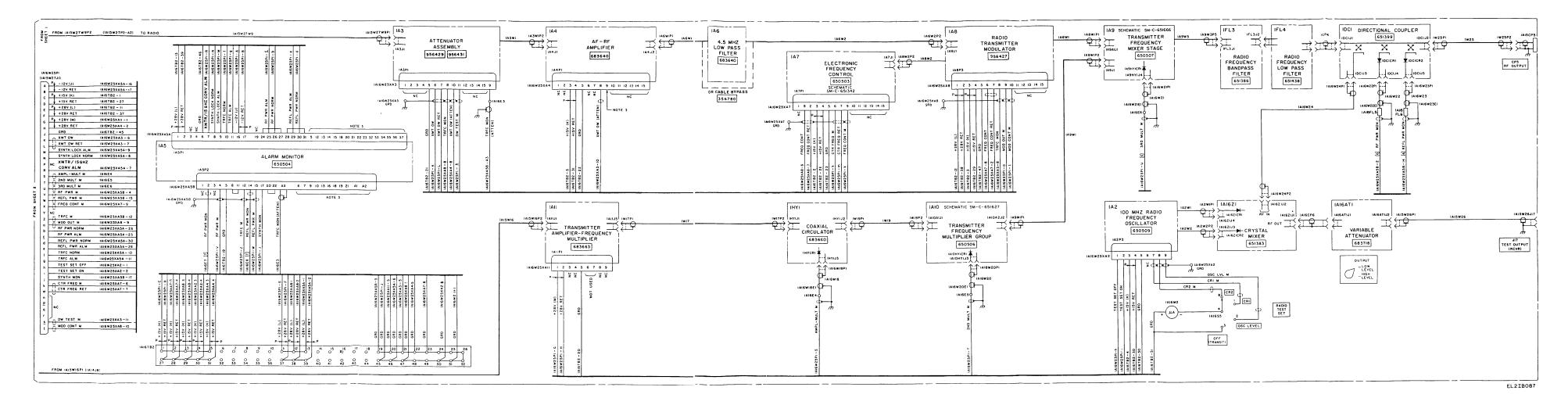

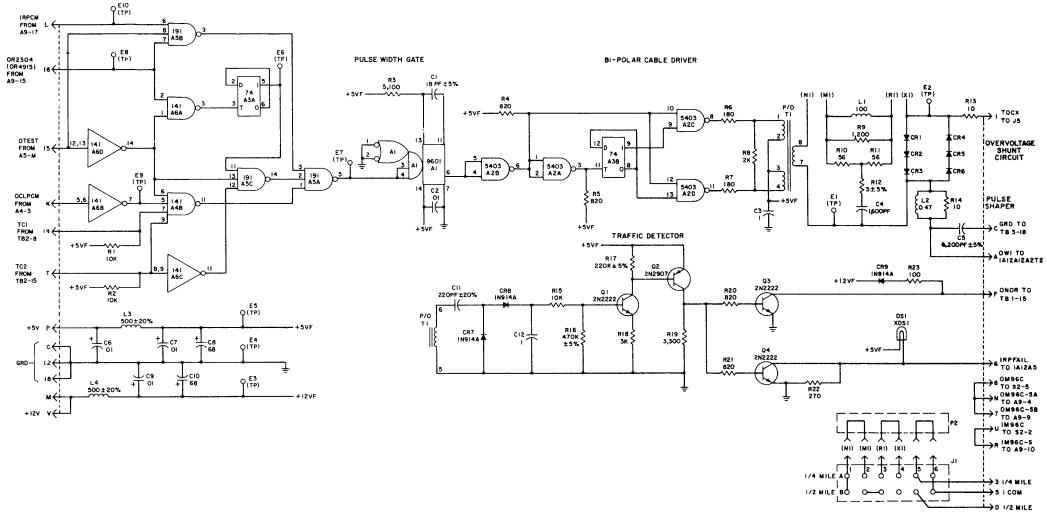

| 5-6<br>5-6.1            | Transmitter Radio T-1054(P)/GRC-144(V), block diagram<br>Transmitter, Radio T-1054(P)A/GRC-144(V) block     | 5-13         |

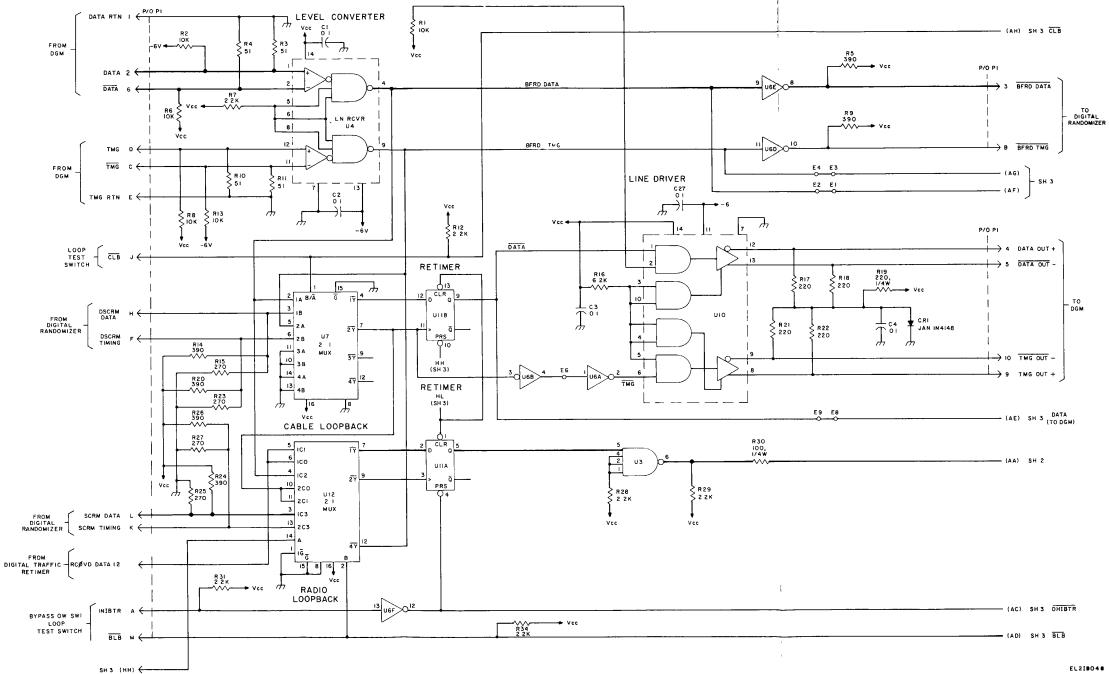

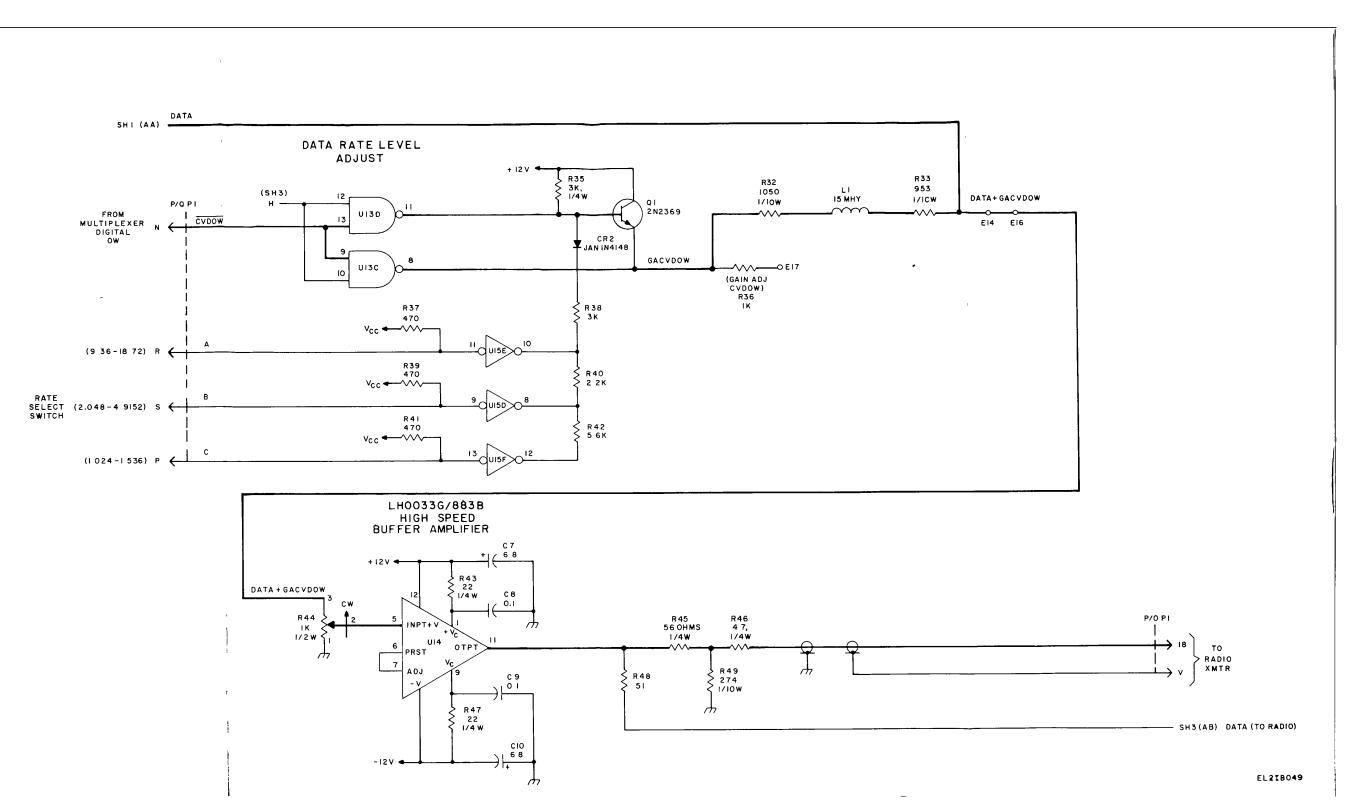

| 5-7                     | diagram<br>Digital data modem 1A12, cable-to-radio circuits,                                                | 5-13.1       |

| 5-7.1                   | functional block diagram<br>Digital data modem 1A12 cable-to-radio circuits,                                | 5-15         |

|                         | functional block diagram asynchronous mode                                                                  | 5-16.1       |

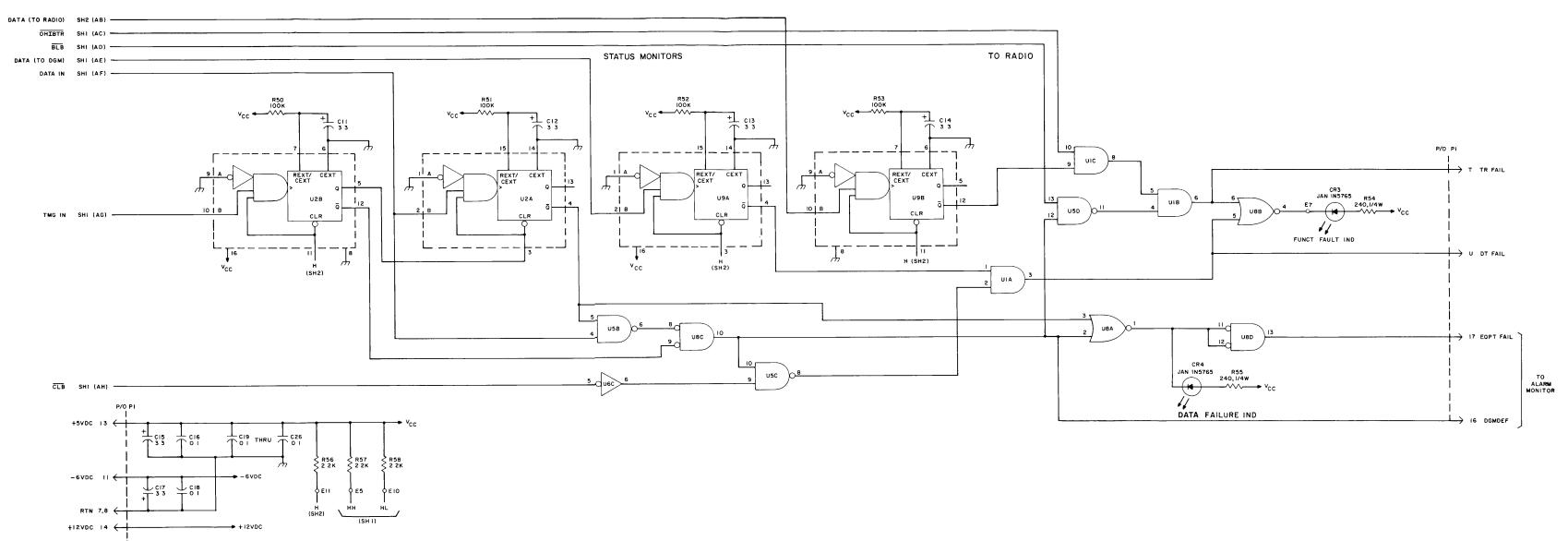

| 5-8                     | Digital data modem 1A12, radio-to-cable circuits,<br>functional block diagram synchronous mode              | 5-17         |

| 5-8.1                   | Digital data modem 1A12, radio-to-cable circuits,<br>functional block diagram asynchronous mode             | 5-18.1       |

| 5-8.2                   | Digital data combiner 1A12, cable-to-radio circuits,                                                        |              |

| 5-8.3                   | functional block diagram<br>Digital data combiner 1A12, radio-to-cable circuits,                            | 5-18.3       |

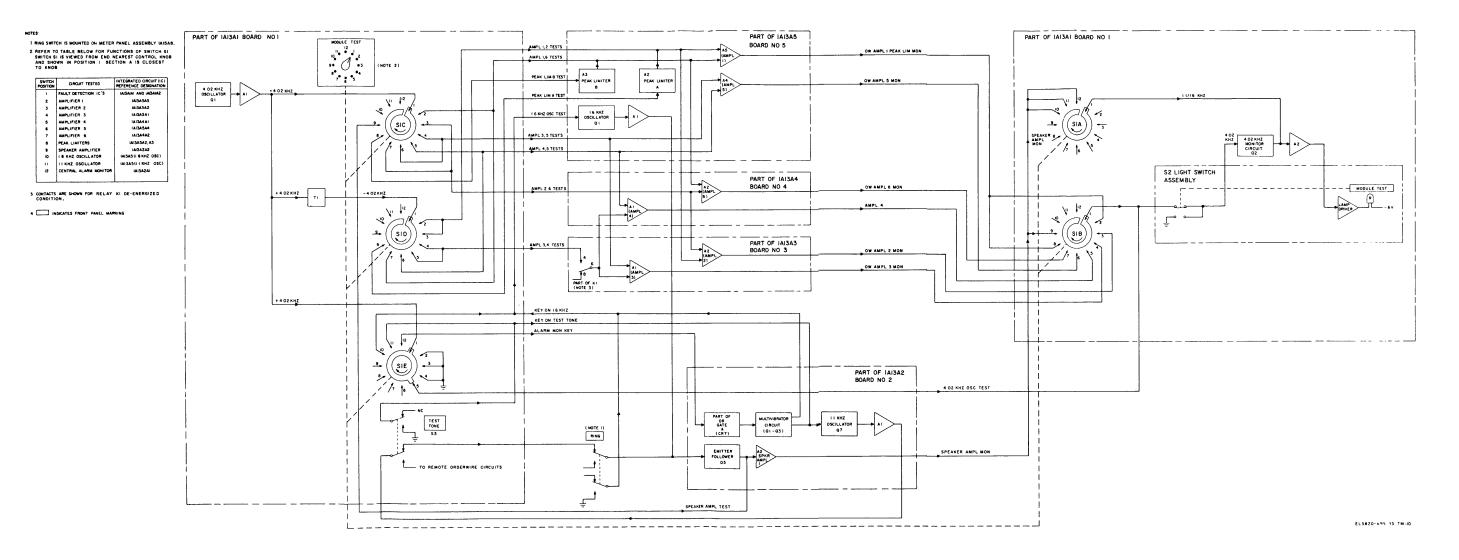

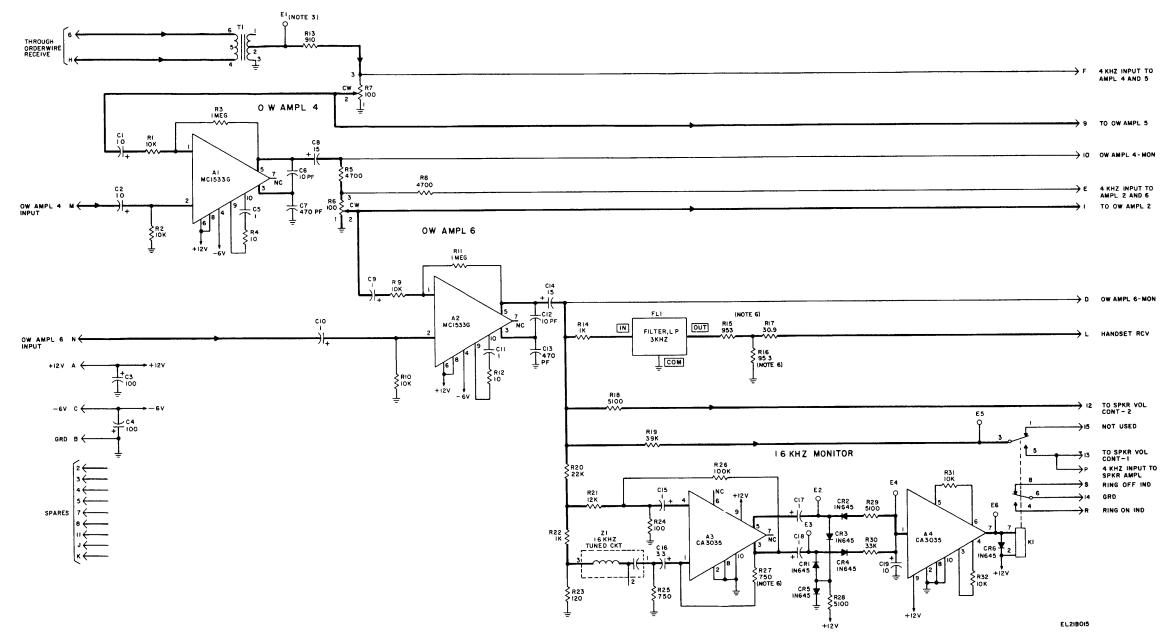

| 5-9                     | functional block diagram<br>Orderwire assembly 1A13, signal distribution circuits                           | 5-18.5       |

|                         | block diagram                                                                                               | 5-19         |

Change 6 vii

| <b>-</b>                | LIST OF ILLUSTRATIONS - Continued                                                                                     |              |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------|

| Figure<br><u>Number</u> | Title                                                                                                                 | <u>Page</u>  |

| 5-10                    | Orderwire assembly 1A13, fault detection circuits,<br>block diagram                                                   | 5-21         |

| 5-11                    | Transmitter, Radio T-1054(P)/GRC-144(V) modulator<br>circuits, functional block diagram                               | 5-23         |

| 5-11.1                  | Transmitter, Radio T-1054(P)A/GRC-144(V) modulator<br>circuits, functional block diagram                              | 5-23.1       |

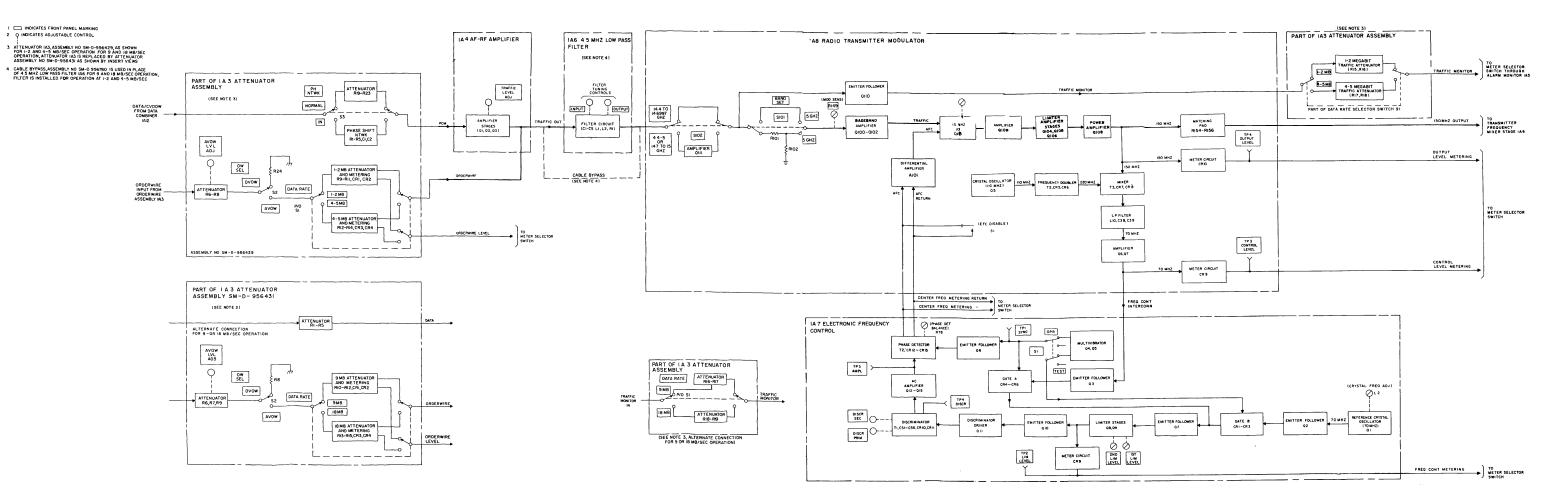

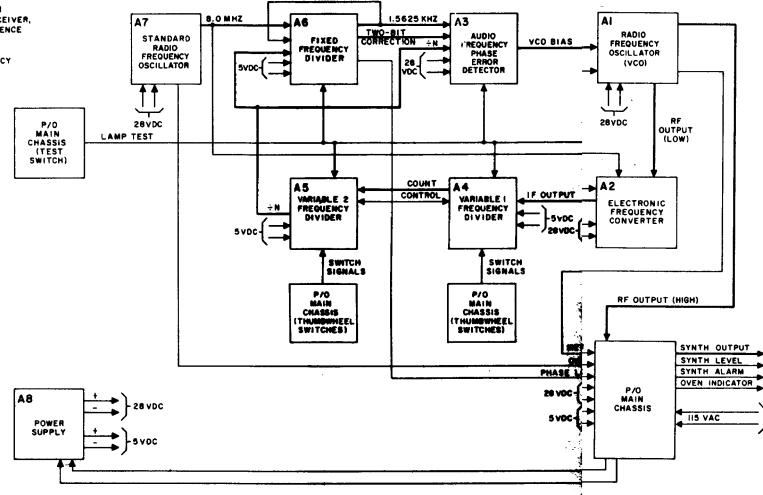

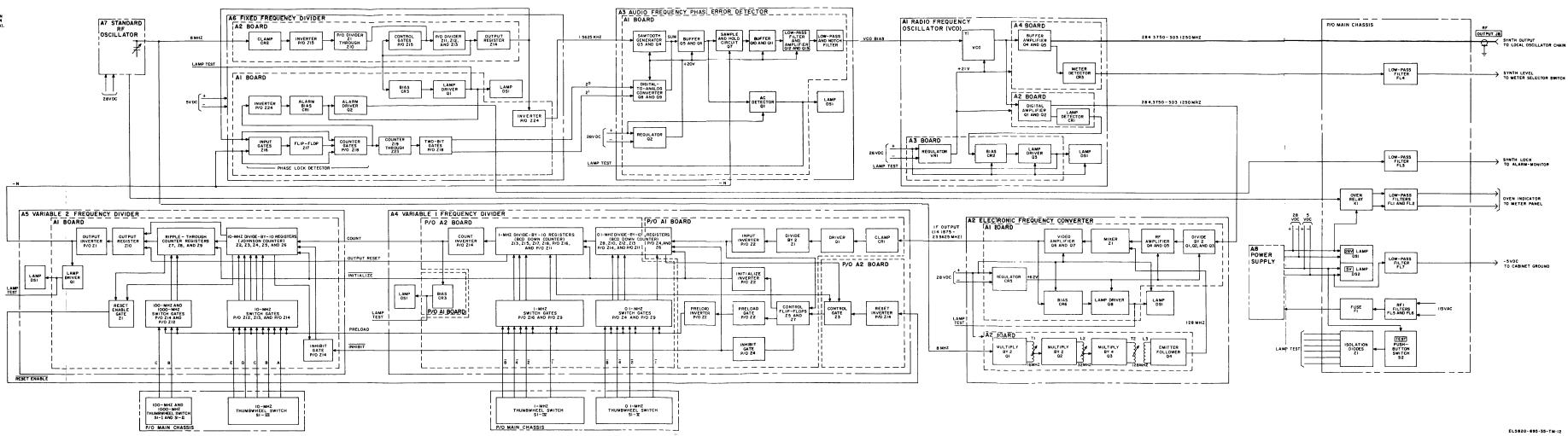

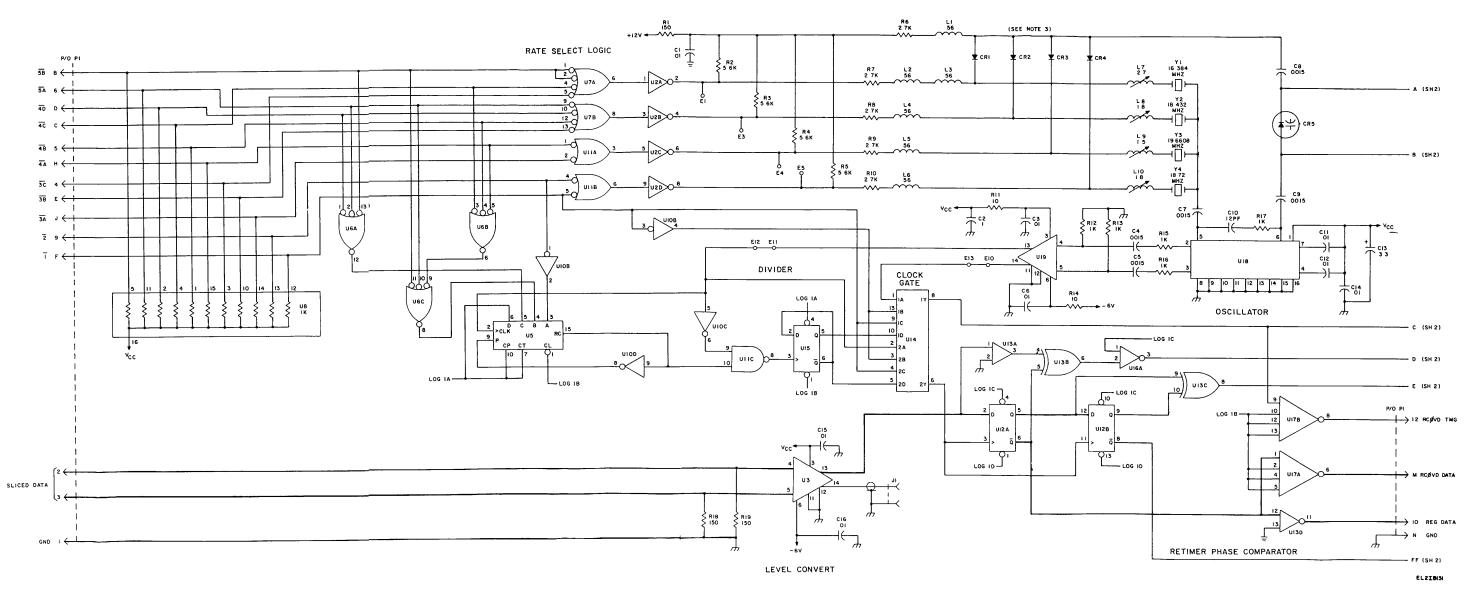

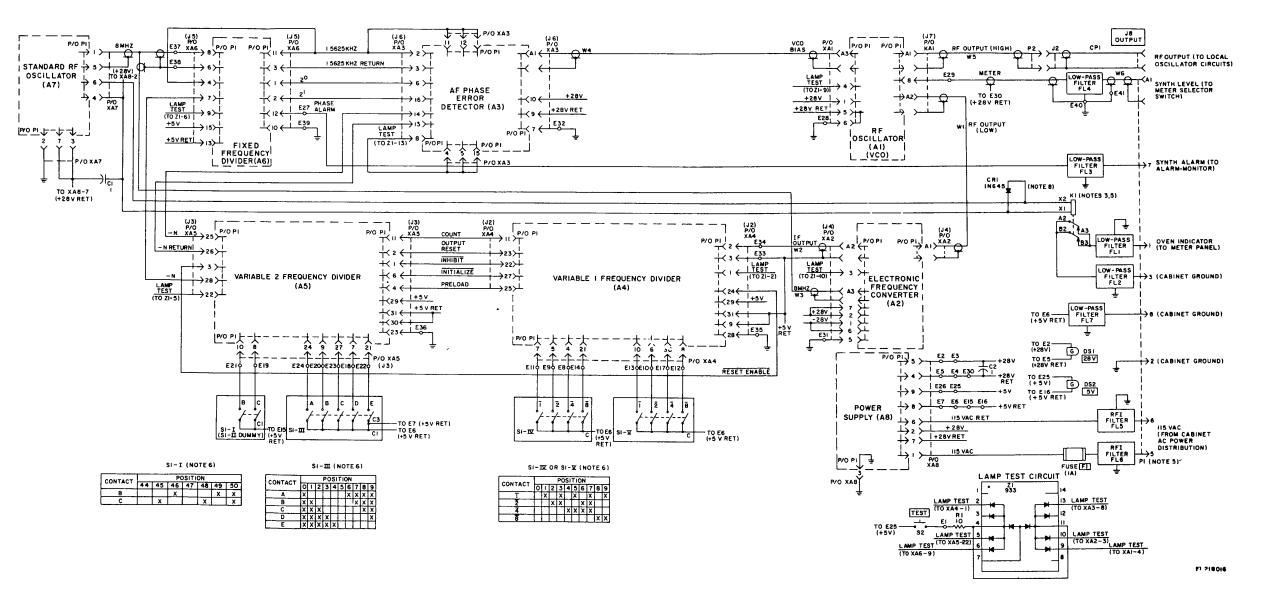

| 5-12                    | Electrical frequency synthesizer 1A14/2A14 overall<br>block diagram                                                   | 5-25         |

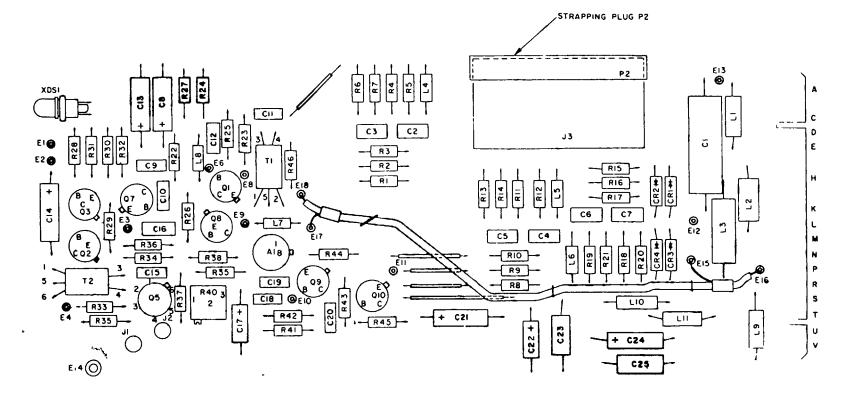

| 5-13                    | Electrical frequency synthesizer 1A14/2A14 functional<br>block diagram                                                | 5-27         |

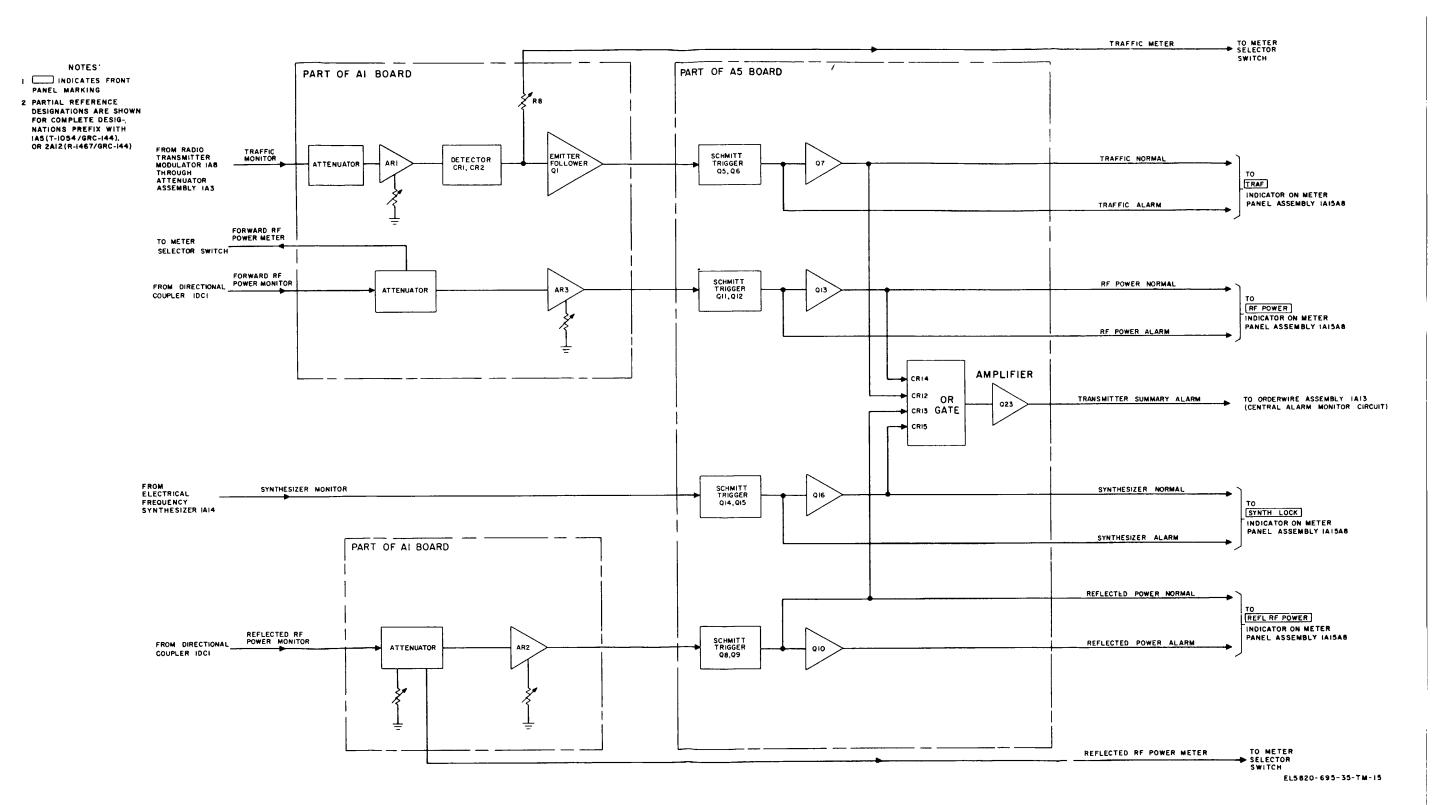

| 5-14<br>5-15(1)         | Alarm monitor 1A5, block diagram<br>Transmitter Radio T-1054(P)/GRC-144(V), interconnecting<br>diagram (Sheet 1 of 3) | 5-29<br>5-31 |

| 5-15(2)                 | Transmitter Radio T-1054(P)/GRC-144(V), interconnecting<br>diagram (Sheet 2 of 3)                                     | 5-33         |

| 5-15(3)                 | Transmitter Radio T-1054(P)/GRC-144(V), interconnecting<br>diagram (Sheet 3 of 3)                                     | 5-35         |

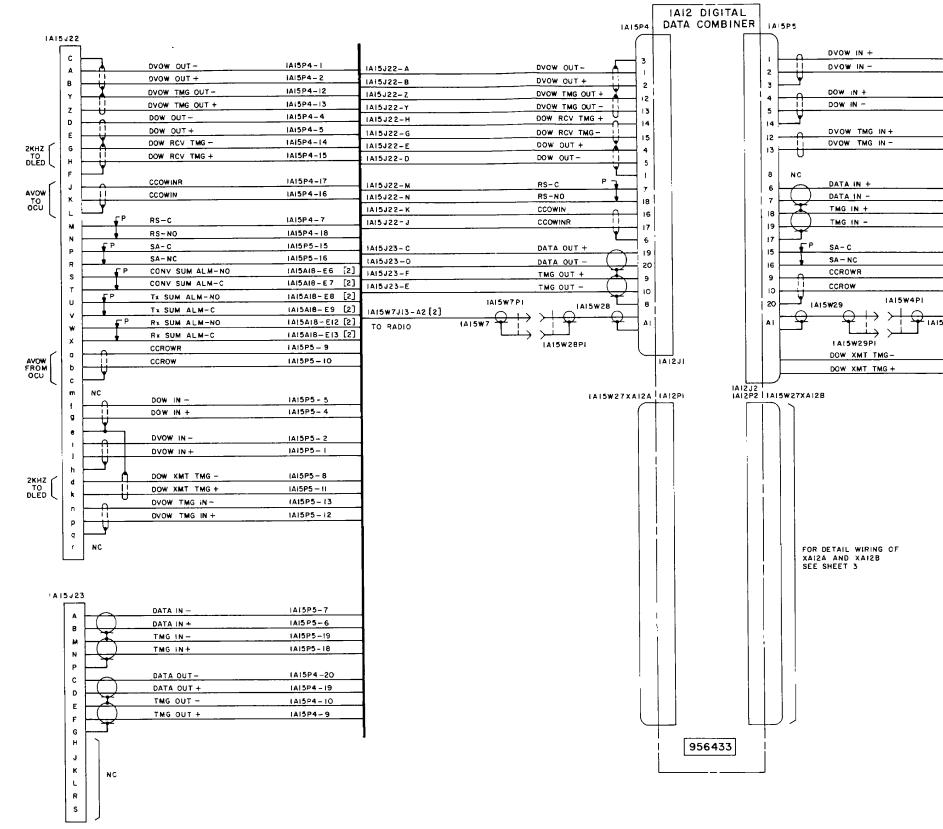

| 5-15.1(1)               | Transmitter, Radio T-1054(P)A/GRC-144(V) inter-<br>connecting diagram, (Sheet 1 of 4)                                 | 5-35.1       |

| 5-15.1(2)               | Transmitter, Radio T-1054(P)A/GRC-144(V) inter-<br>connecting diagram, (Sheet 2 of 4)                                 | 5-35.3       |

| 5-15.1(3)               | Transmitter, Radio T-1054(P)A/GRC-144(V) inter-<br>connecting diagram, (Sheet 3 of 4)                                 | 5-35.5       |

| 5-15.1(4)               | Transmitter, Radio T-1054(P)A/GRC-144(V) inter-<br>connecting diagram, (Sheet 4 of 4)                                 | 5-35.7       |

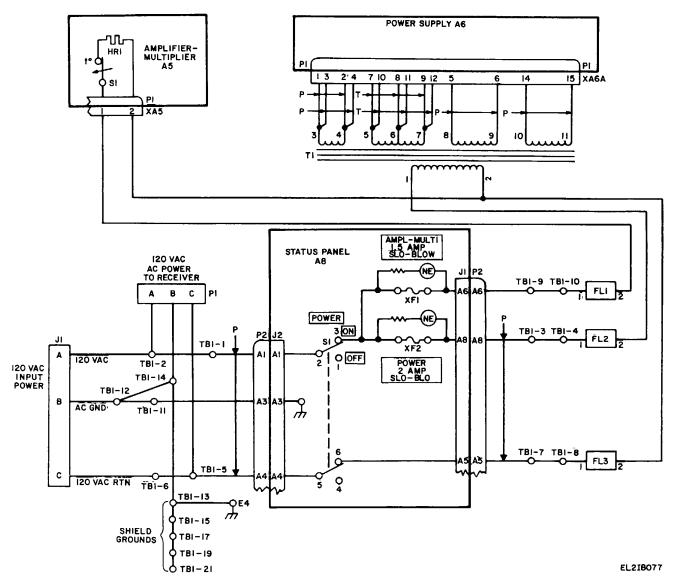

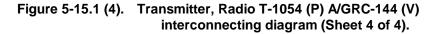

| 5-16                    | Transmitter, Radio T-1054(P)/GRC-144(V) and T-1054(P)A/<br>GRC-144(V), DC power distribution diagram                  | 5-37         |

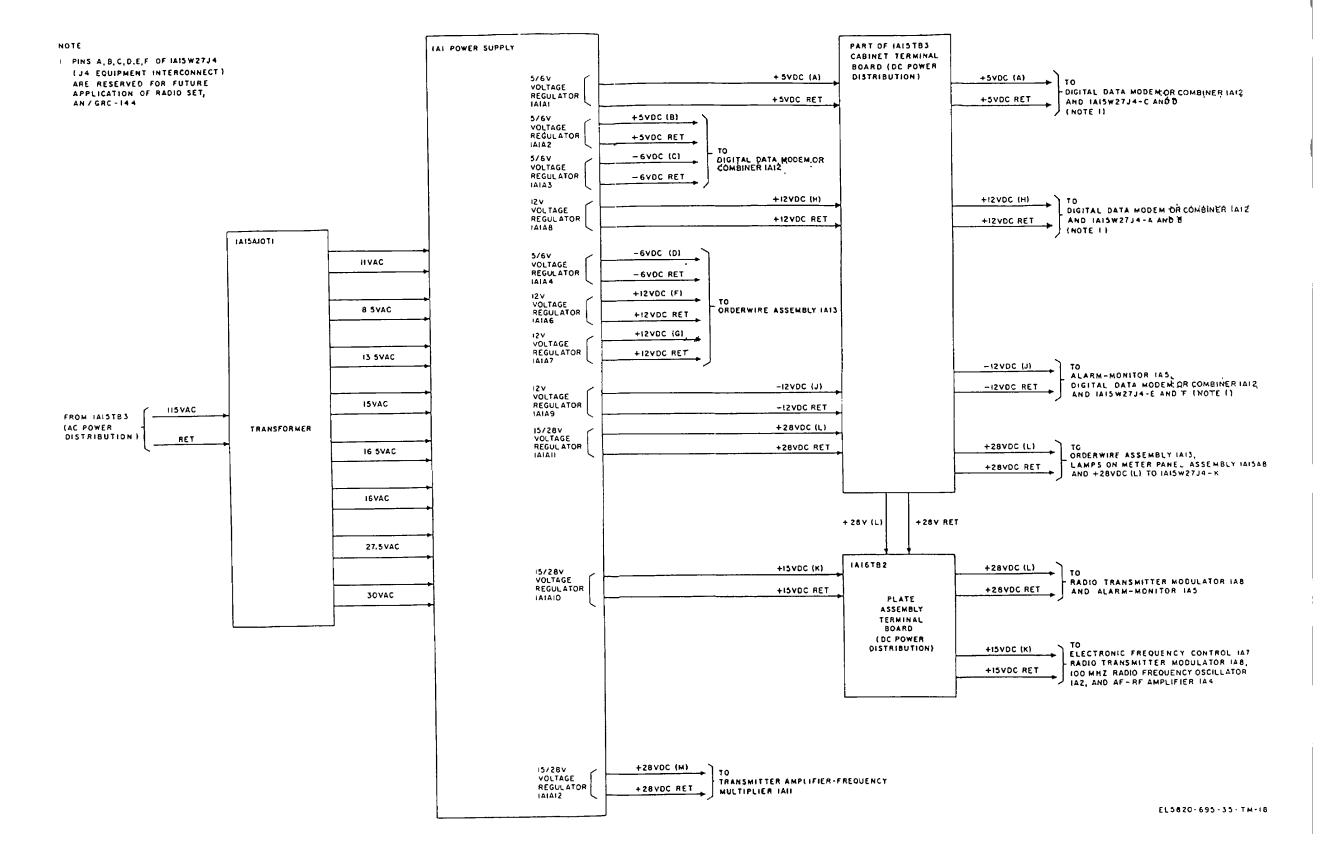

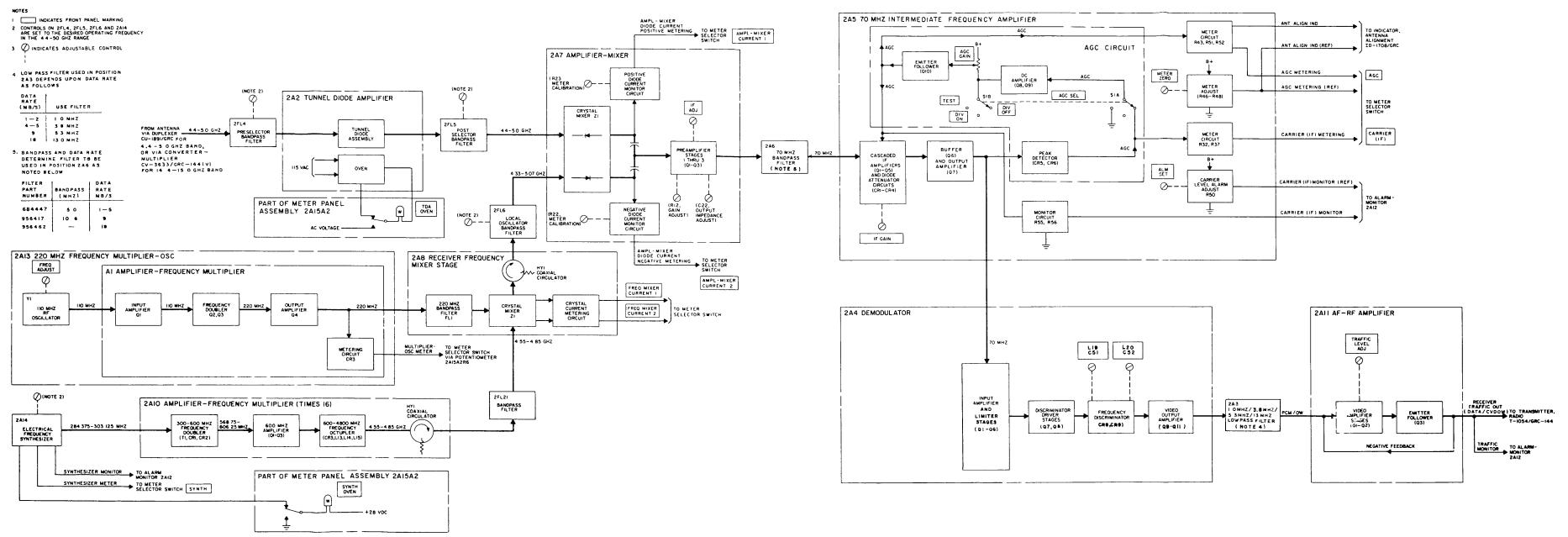

| 5-17<br>5-18            | Power Supply 1A1, interconnecting diagram<br>Receiver, Radio R-1467(P)/GRC-144(V), overall block diag                 | 5-39<br>5-41 |

| 5-18.1                  | Receiver, Radio R-1467(P)A/GRC-144(V) overall block<br>diagram                                                        | 5-41.1       |

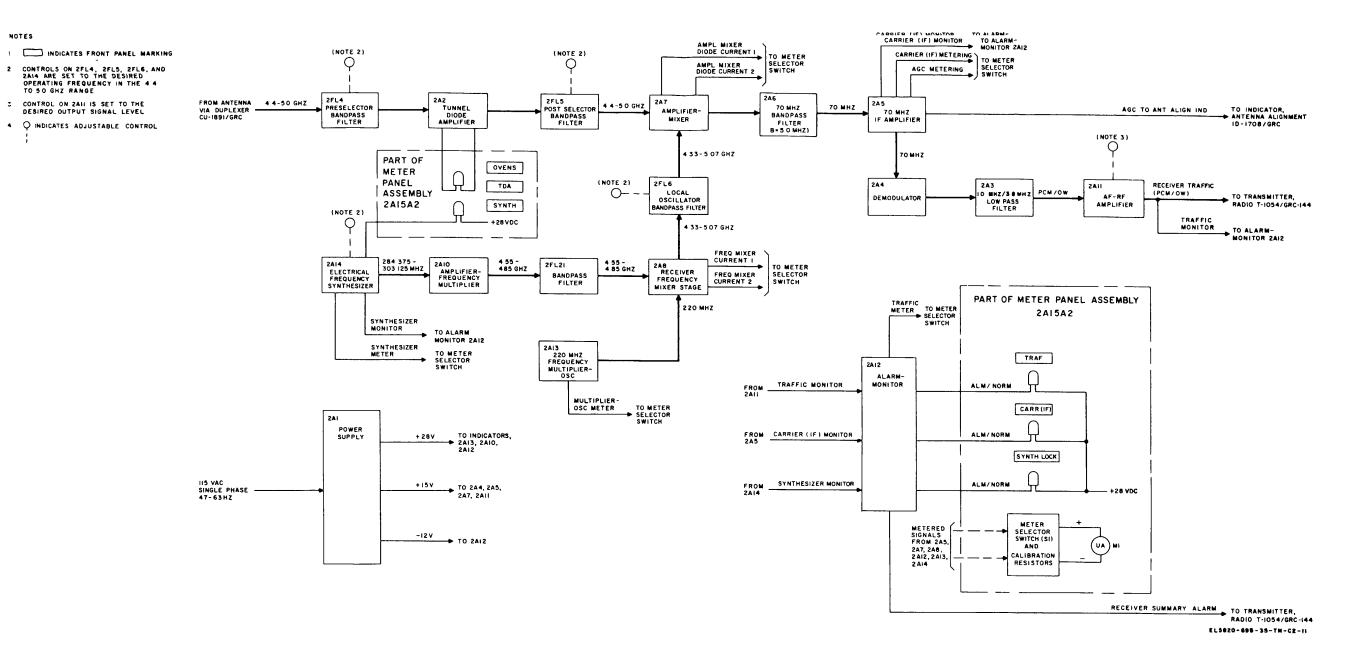

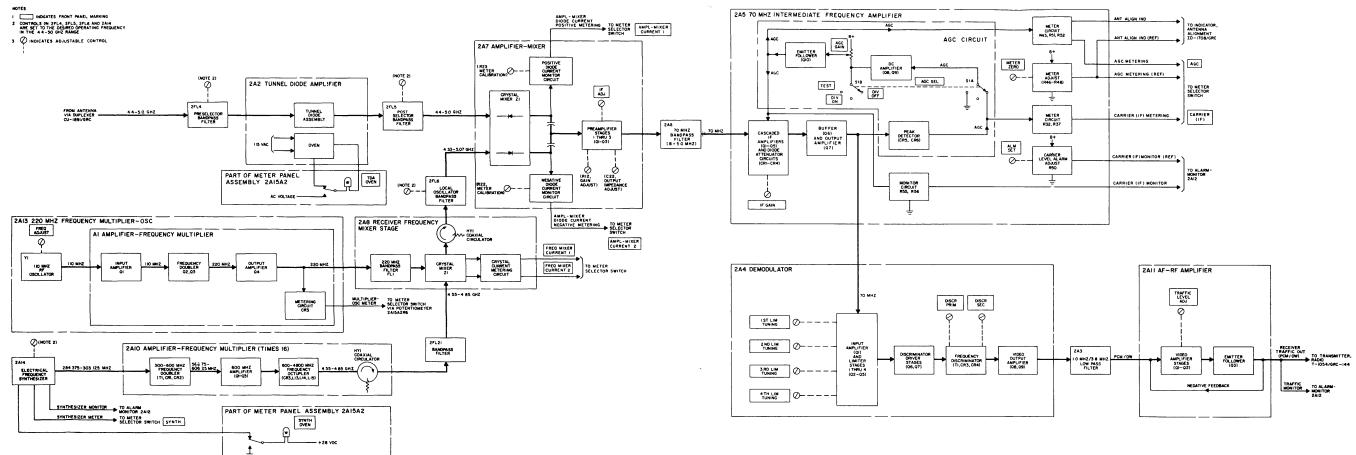

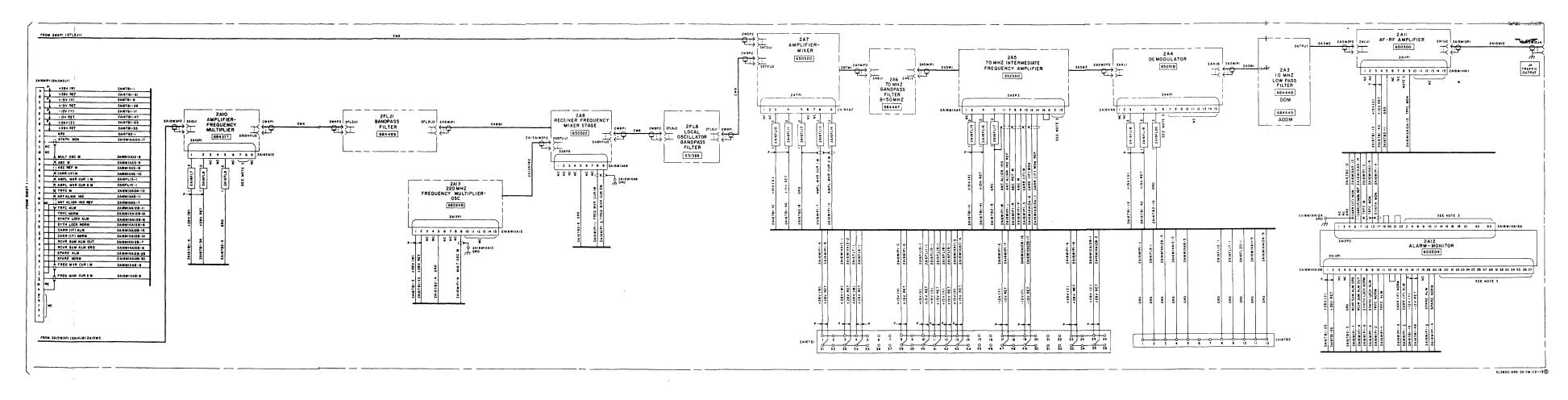

| 5-19                    | Receiver, Radio R-1467(P)/GRC-144(V), functional block<br>diagram                                                     | 5-43         |

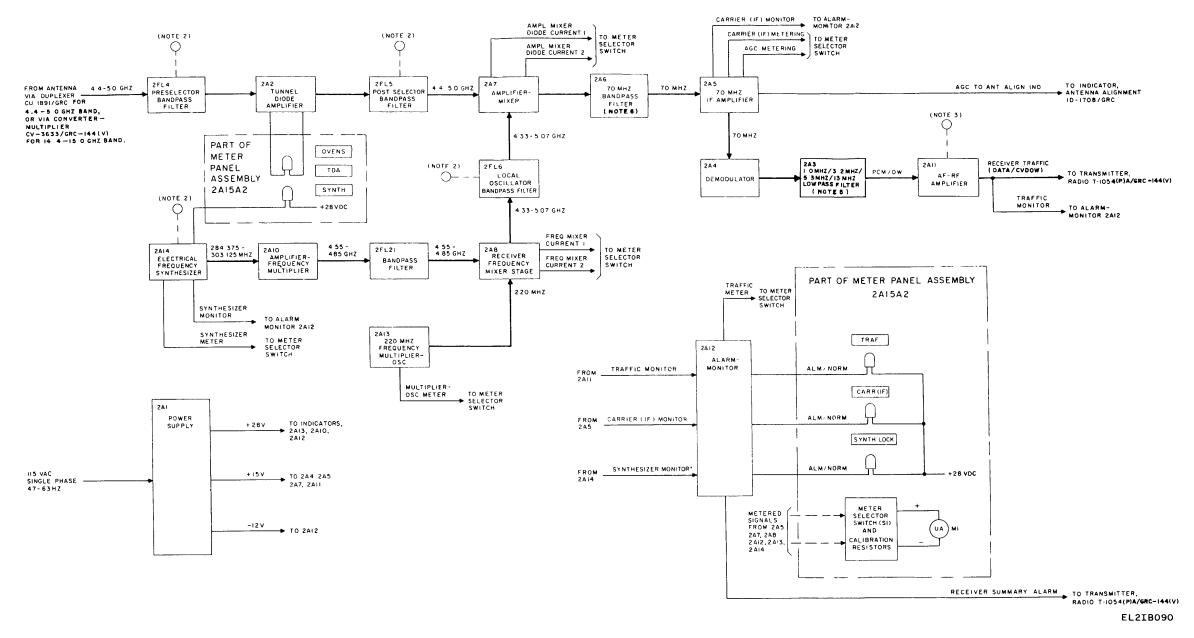

| 5-19.1                  | Receiver, Radio R-1467(P)A/GRC-144(V) functional<br>block diagram                                                     | 5-43.1       |

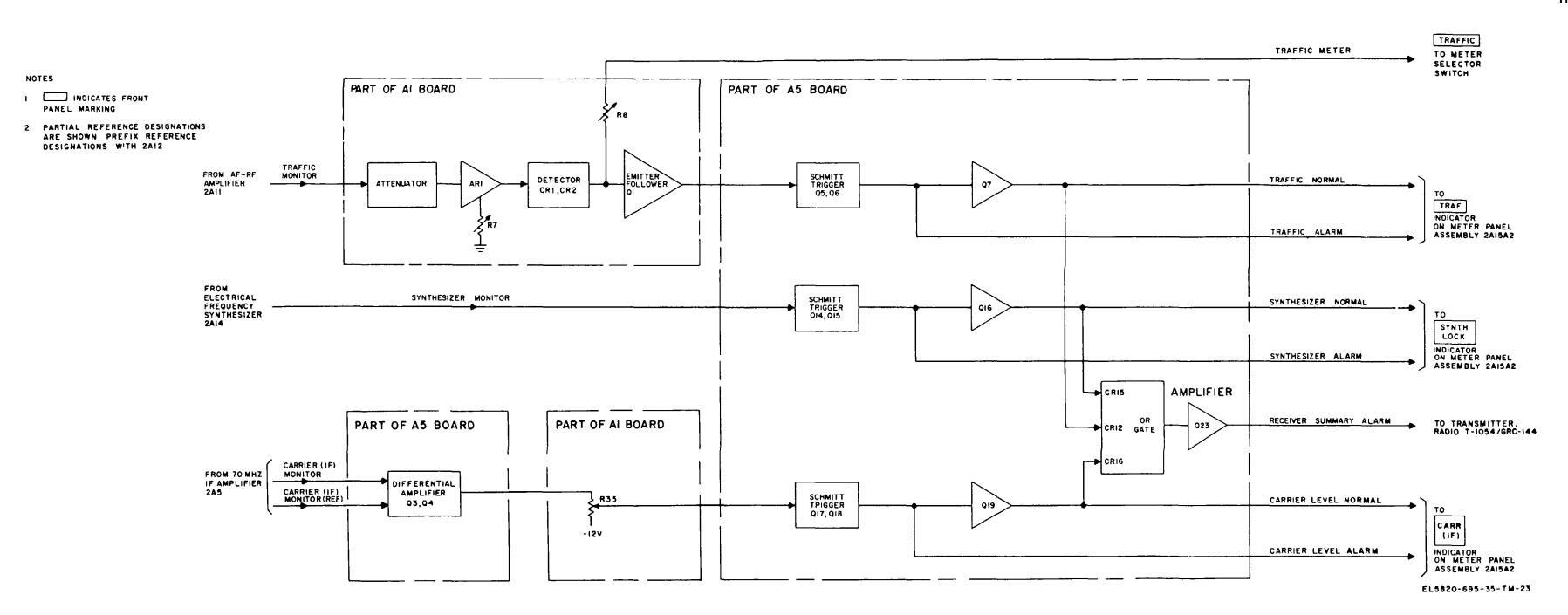

| 5-20                    | Alarm Monitor 2A12, block diagram                                                                                     | 5-45         |

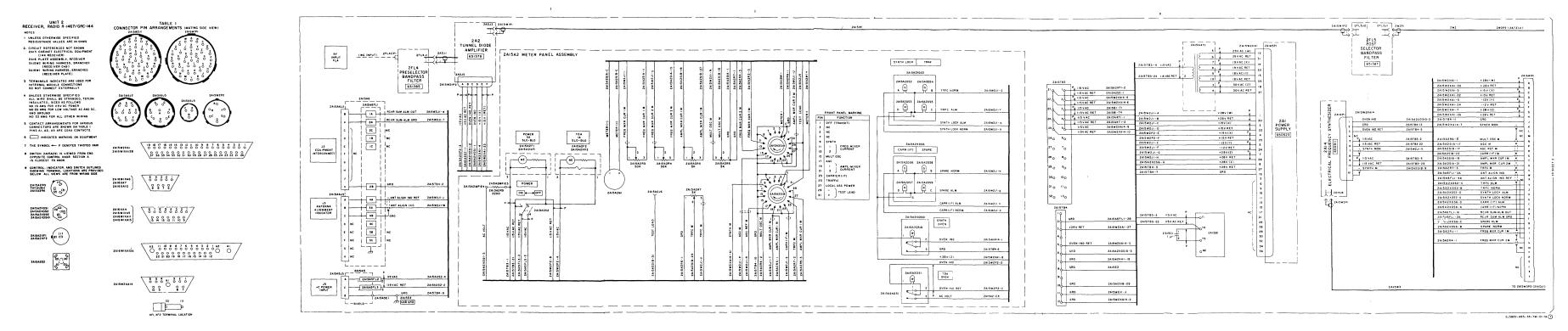

| 5-21(1)                 | Receiver, Radio R-1467(P)/GRC-144(V) interconnecting<br>diagram (Part 1 of 2)                                         | 5-47         |

| 5-21(2)                 | Receiver, Radio R-1467(P)/GRC-144(V) interconnecting<br>diagram (Part 2 of 2)                                         | 5-49         |

| 5-21.1                  | Receiver, Radio R-1467(P)A/GRC-144(V) interconnecting<br>diagram                                                      | 5-49.1       |

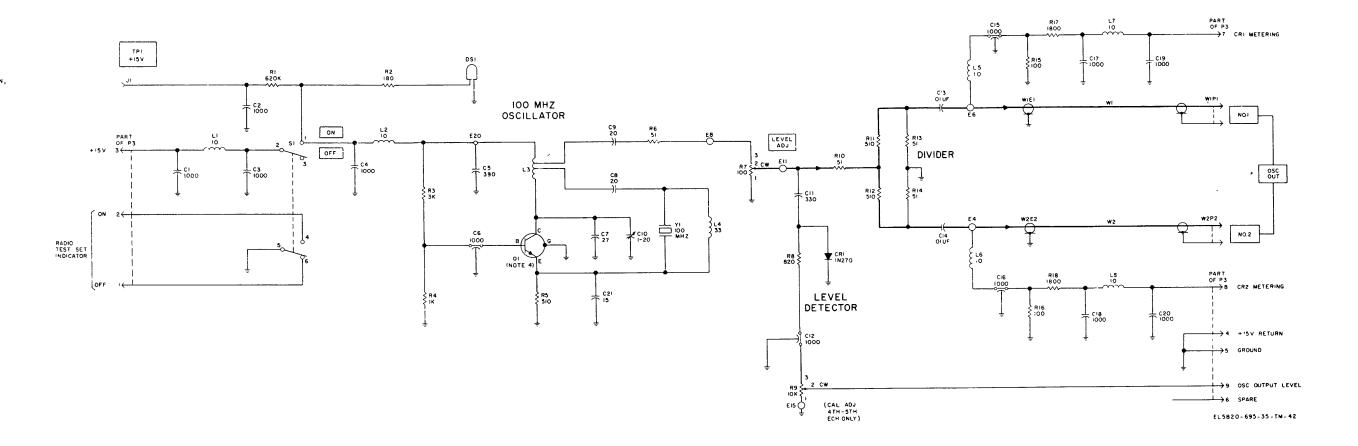

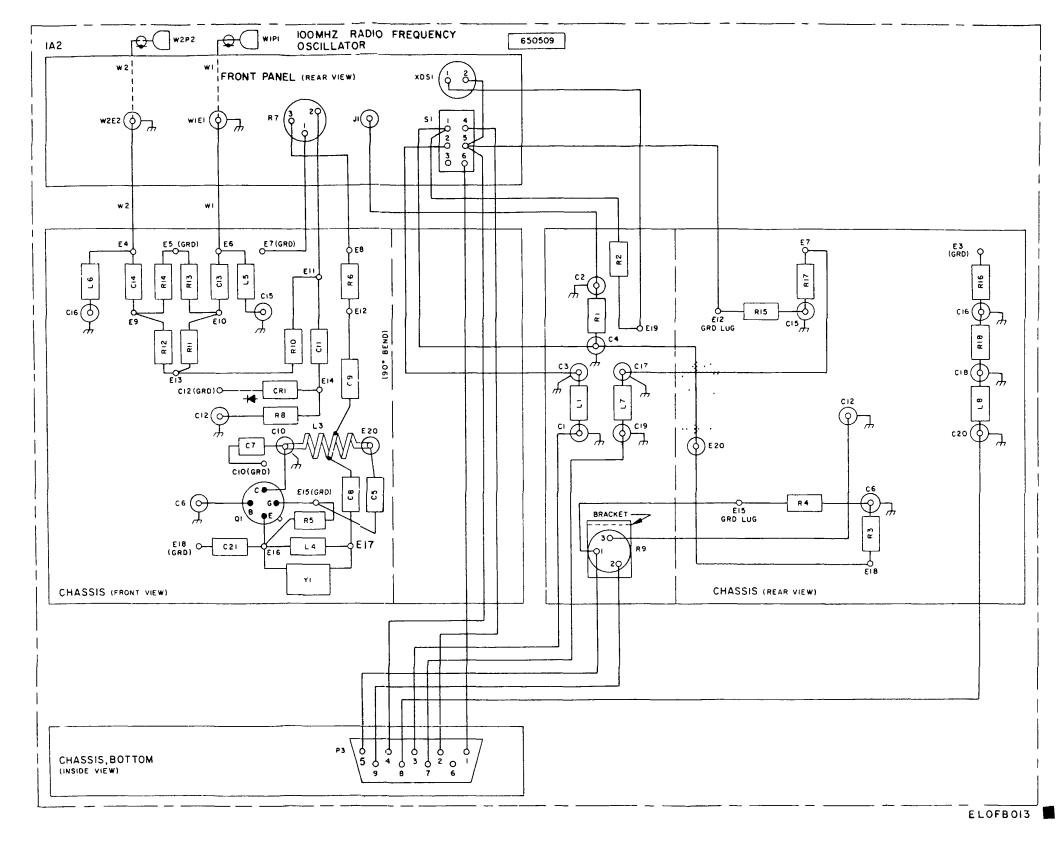

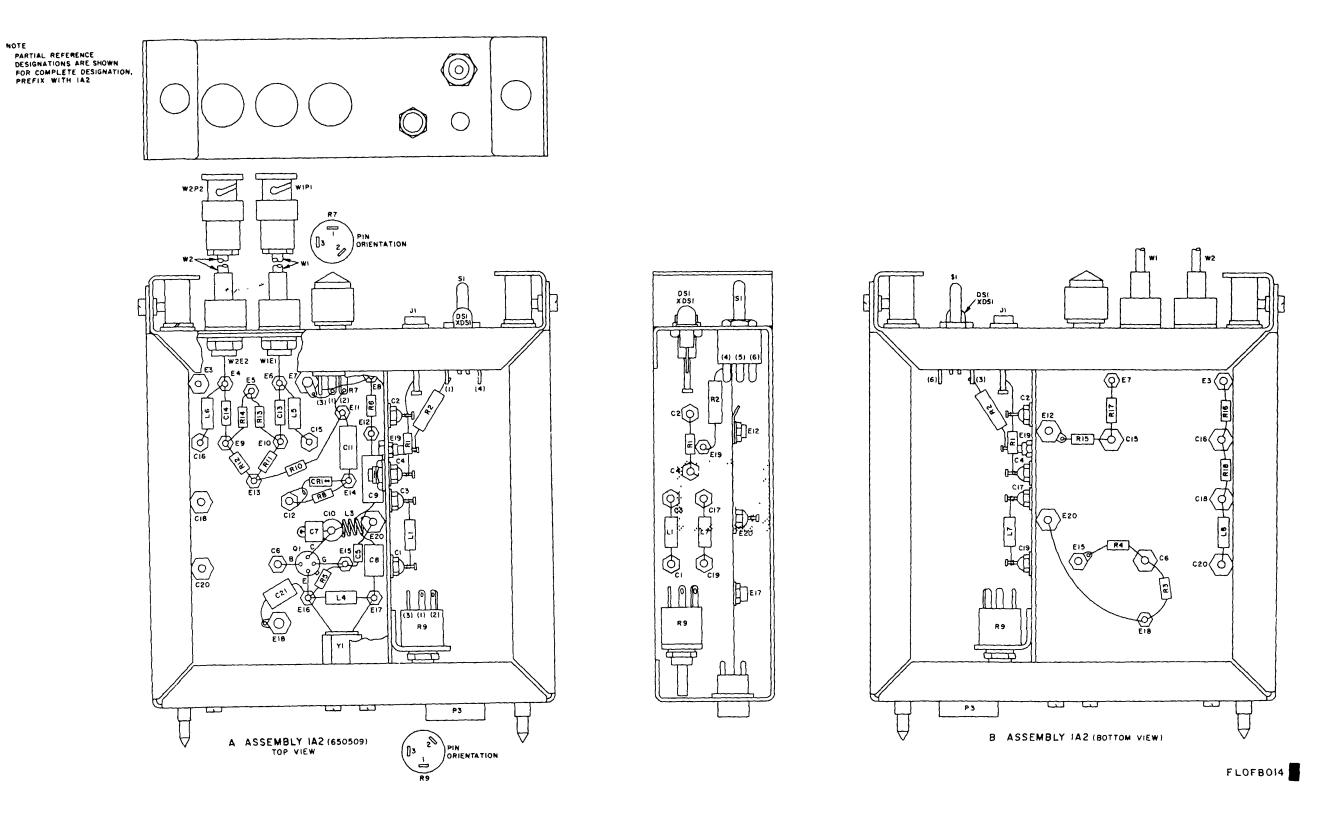

| 5-22<br>5-23            | Power Supply 2A1, interconnecting diagram<br>100 MHz radio frequency oscillator 1A2 schematic                         | 5-51         |

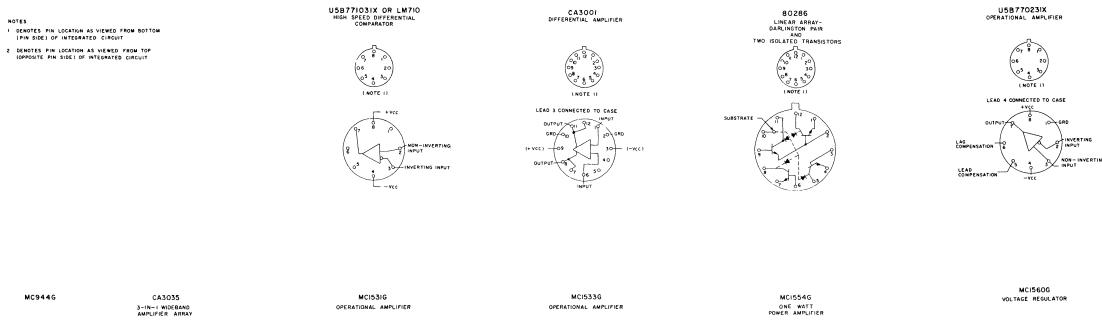

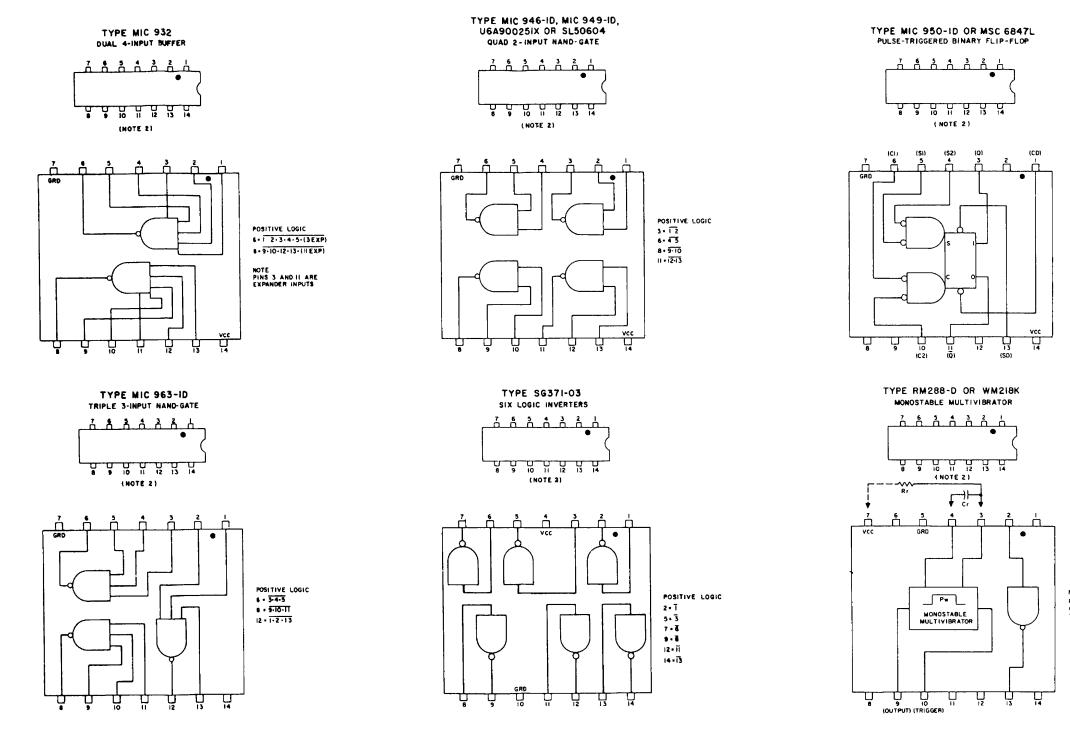

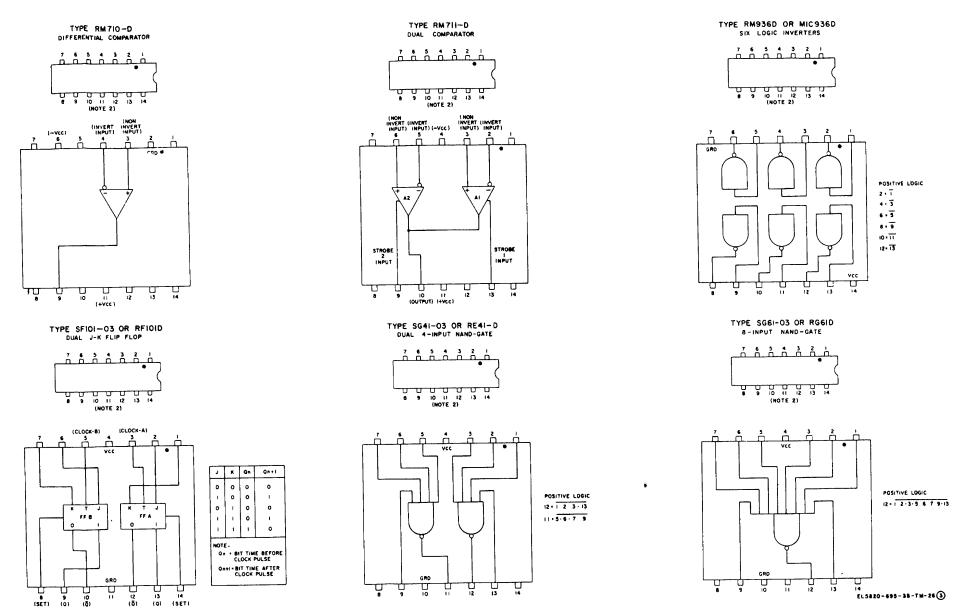

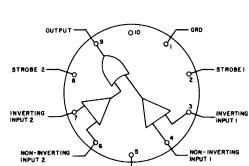

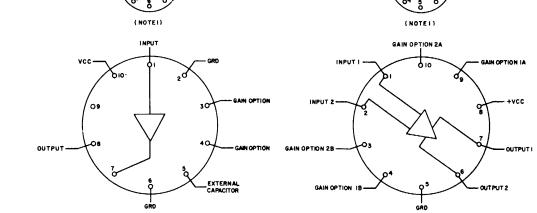

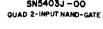

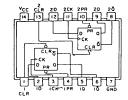

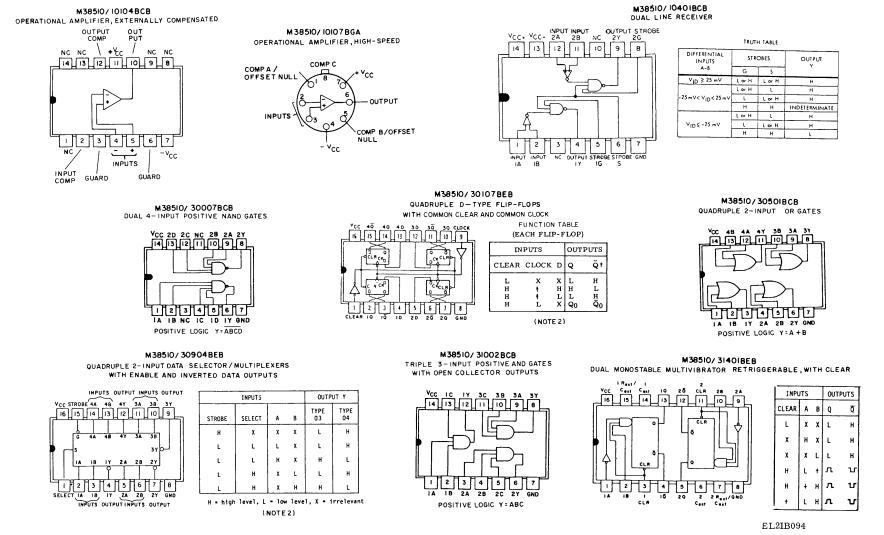

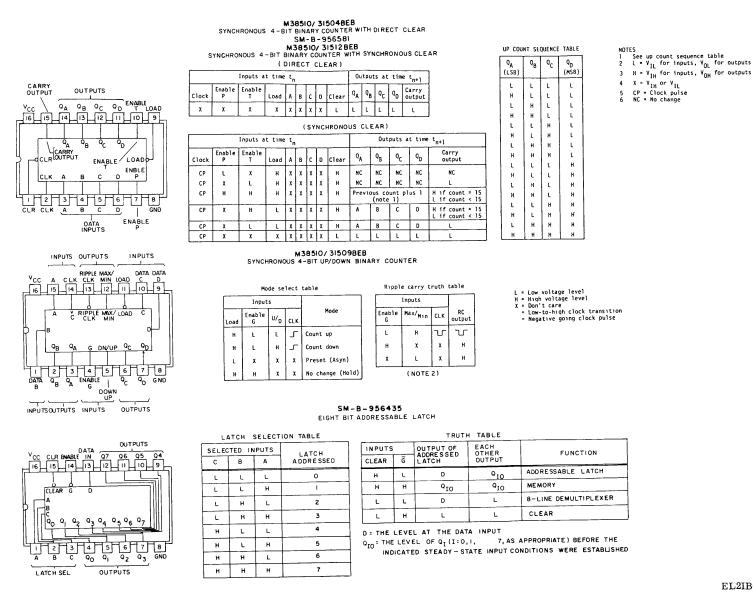

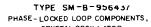

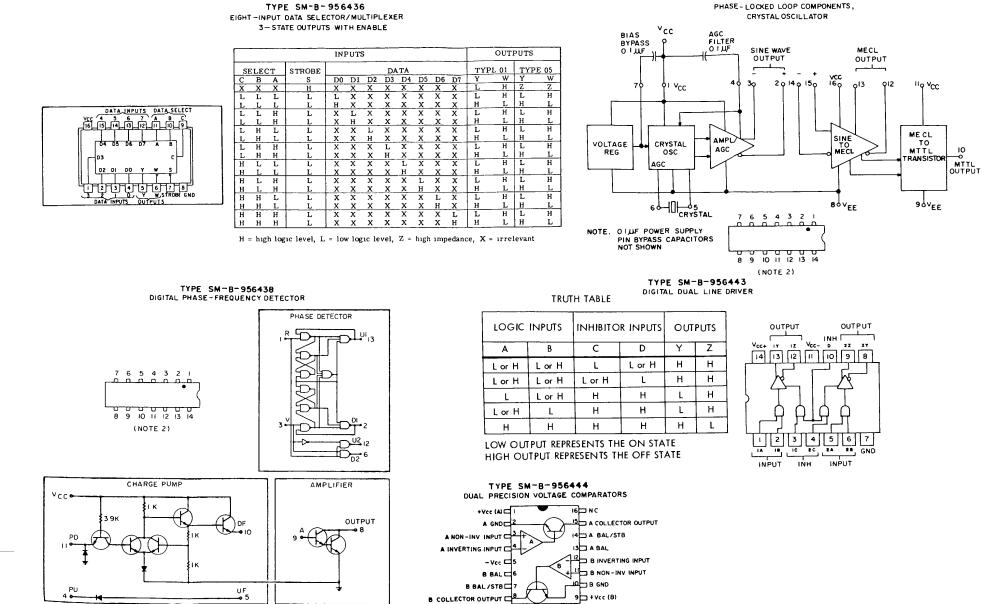

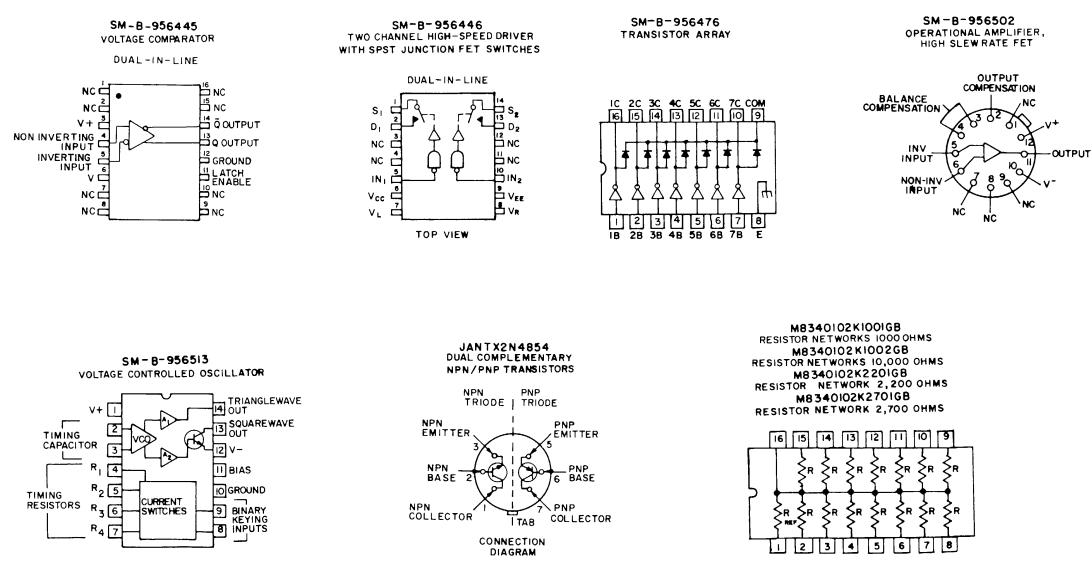

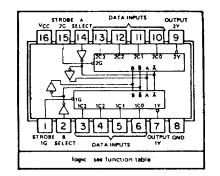

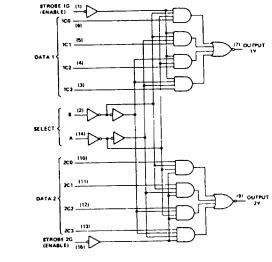

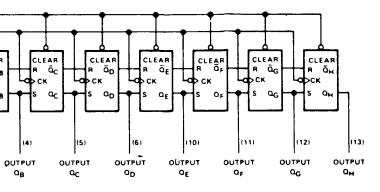

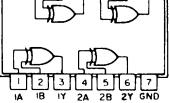

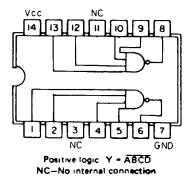

| 5-24(1)                 | diagram<br>Radio Set AN/GRC-144 integrated circuits schematic<br>diagrams (Part 1 of 5)                               | 5-53         |

| 5-24(2)                 | diagrams (Part 1 of 5)<br>Radio Set AN/GRC-144 integrated circuits schematic<br>diagrams (Part 2 of 5)                | 5-55         |

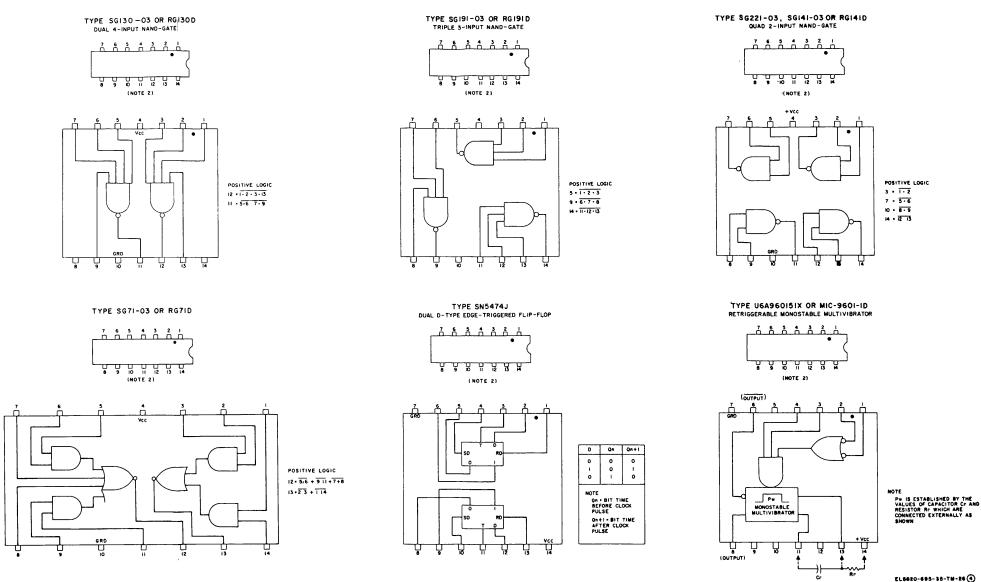

| 5-24(3)                 | diagrams (Part 2 of 5)<br>Radio Set AN/GRC-144 integrated circuits schematic<br>diagrams (Part 3 of 5)                | 5-57<br>5-59 |

|                         |                                                                                                                       | 0.00         |

Change 6 viii

| <b>F</b> :              | LIST OF ILLUSTRATIONS - Continued                                                                                              |         |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------|

| Figure<br><u>Number</u> | Title                                                                                                                          | Page    |

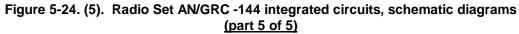

| 5-24(4)                 | Radio Set AN/GRC-144 integrated circuits schematic<br>diagrams (Part 4 of 5)                                                   | 5-61    |

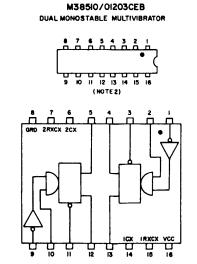

| 5-24(5)                 | Radio Set AN/GRC-144 integrated circuits schematic<br>diagrams (Part 5 of 5)                                                   | 5-62.1  |

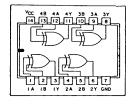

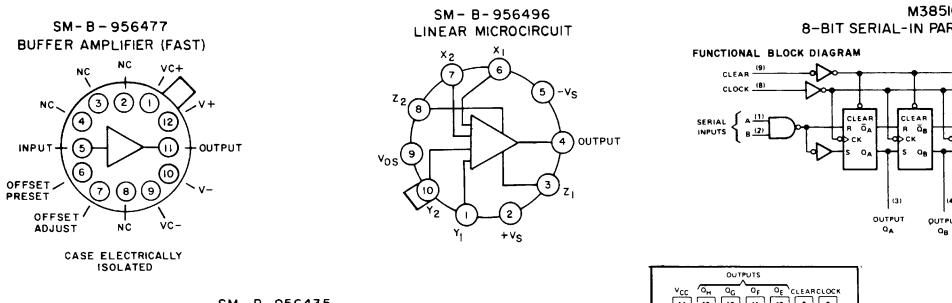

| 5-24.1(1)               | Radio Set AN/GRC-144(V)3 and (V)4 integrated circuits<br>(Sheet 1 of 6)                                                        | 5-62.3  |

| 5-24.1(2)               | Radio Set AN/GRC-144(V)3 and (V)4 integrated circuits<br>(Sheet 2 of 6)                                                        | 5-62.5  |

| 5-24.1(3)               | Radio Set AN/GRC-144(V)3 and (V)4 integrated circuits<br>(Sheet 3 of 6)                                                        | 5-62.7  |

| 5-24.1(4)               | Radio Set AN/GRC-144(V)3 and (V)4 integrated circuits<br>(Sheet 4 of 6)                                                        | 5-62.9  |

| 5-24.1(5)               | Radio Set AN/GRC-144(V)3 and (V)4 integrated circuits<br>(Sheet 5 of 6)                                                        | 5-62.11 |

| 5-24.1(6)               | Radio Set AN/GRC-144(V)3 and (V)4 integrated circuits<br>(Sheet 6 of 6)                                                        | 5-62.13 |

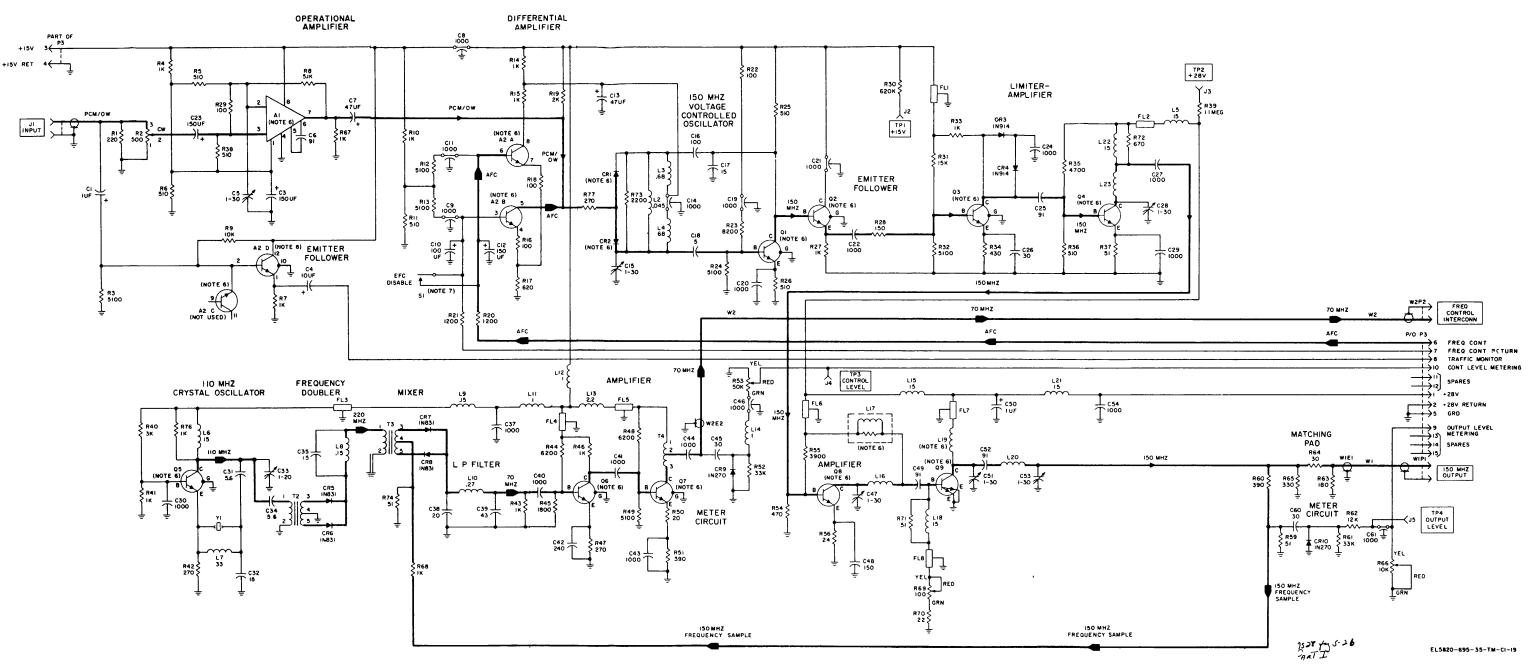

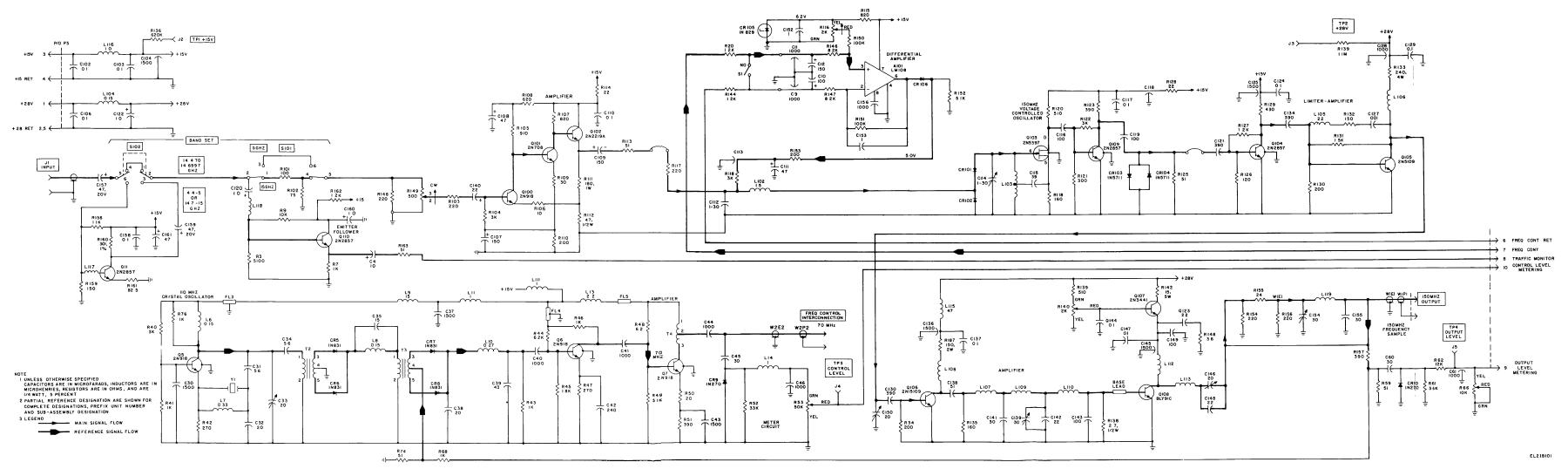

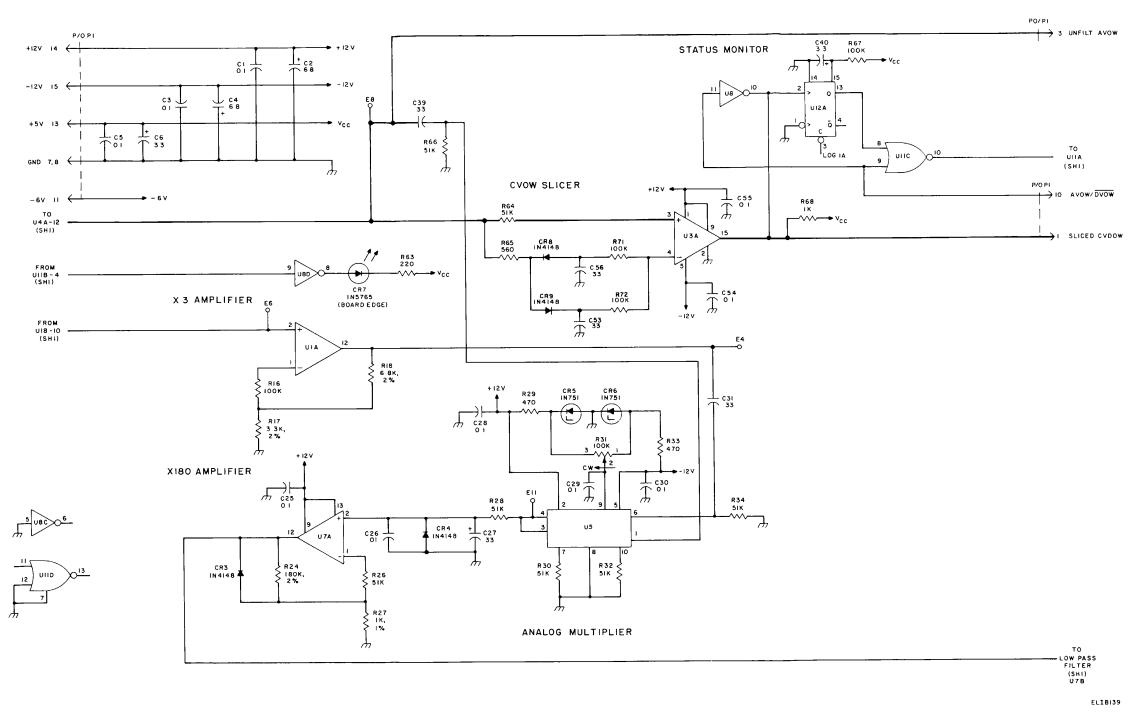

| 5-25                    | Electronic frequency control 1A7, schematic diagram                                                                            | 5-63    |

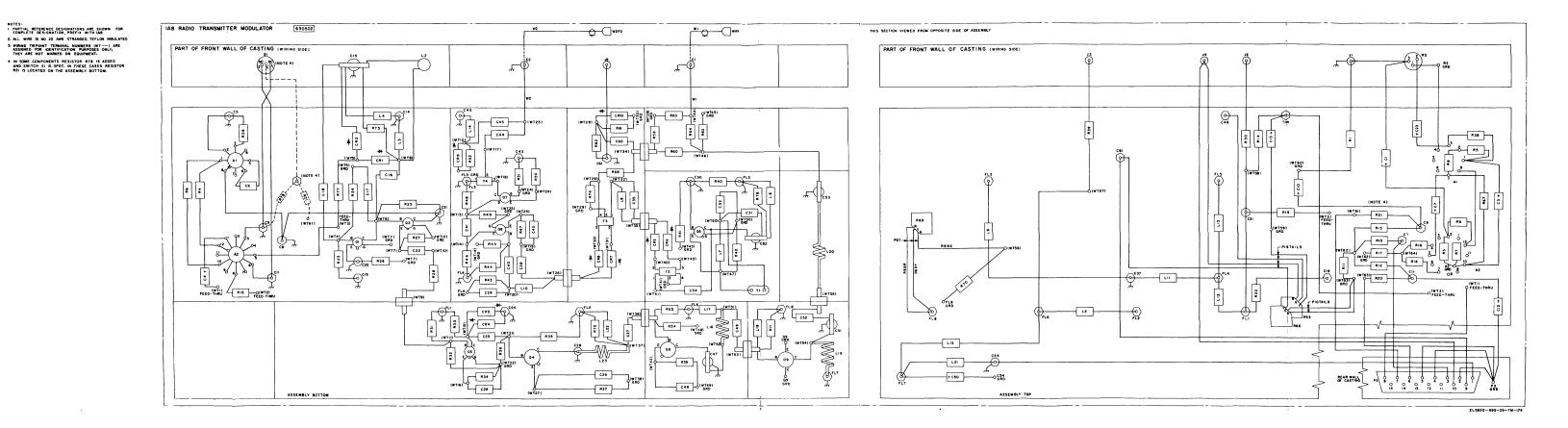

| 5-26                    | Radio transmitter modulator 1A8, schematic diagram                                                                             | 5-65    |

| 5-26.1                  | Modulator, radio transmitter 1A8 (956427), schematic<br>diagram                                                                | 5-65.1  |

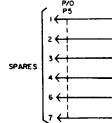

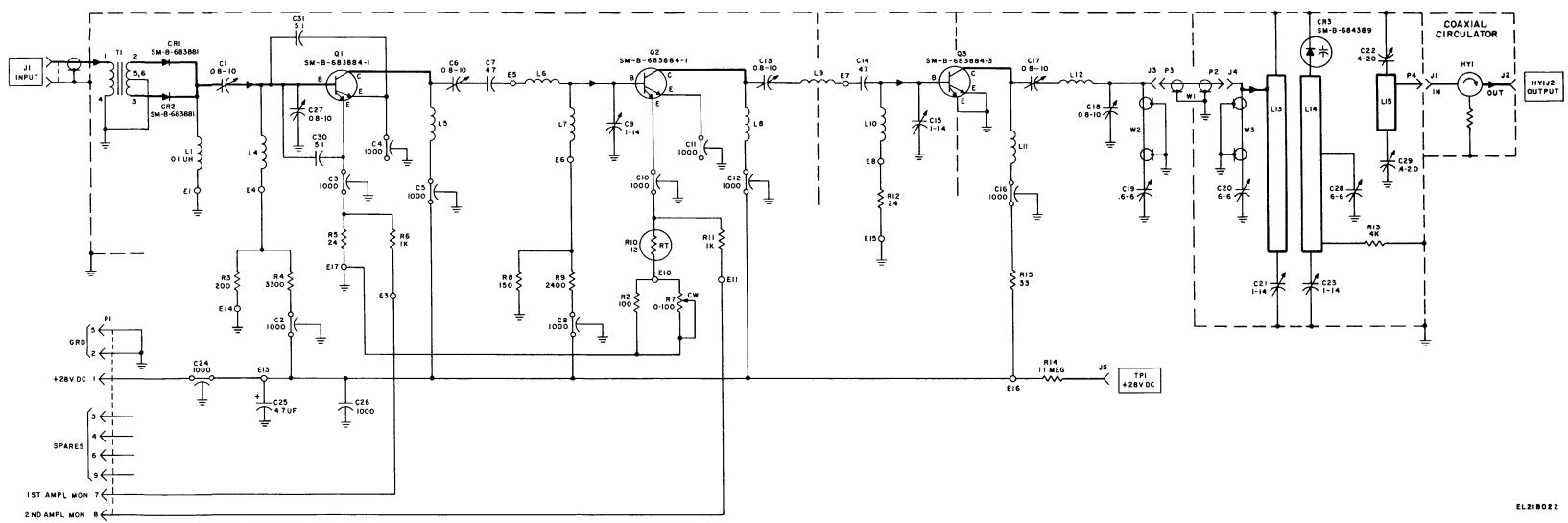

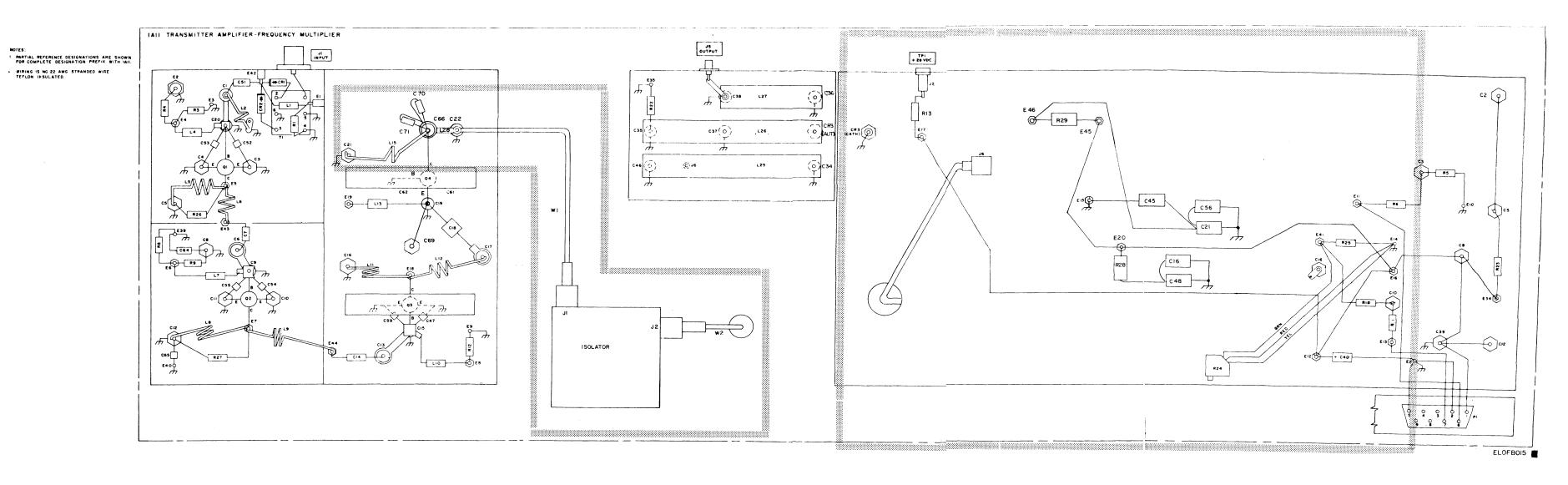

| 5-27                    | Transmitter amplifier-frequency multiplier 1A11,<br>schematic diagram                                                          | 5-67    |

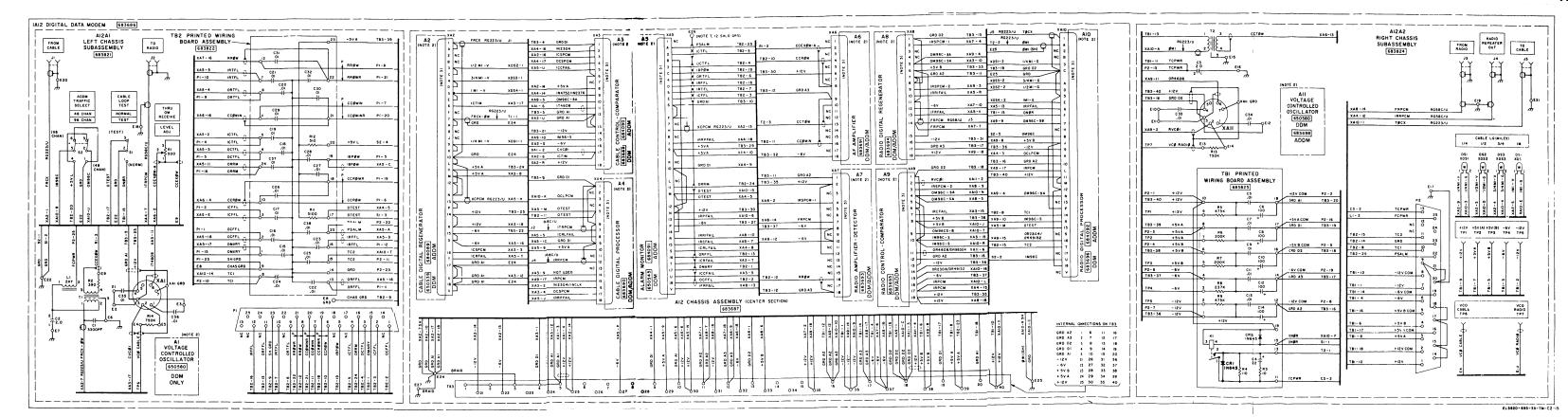

| 5-28                    | Digital data modem 1A12, interconnecting diagram                                                                               | 5-69    |

| 5-29                    | DC path through digital data modem 1A12, simplified<br>schematic diagram                                                       | 5-71    |

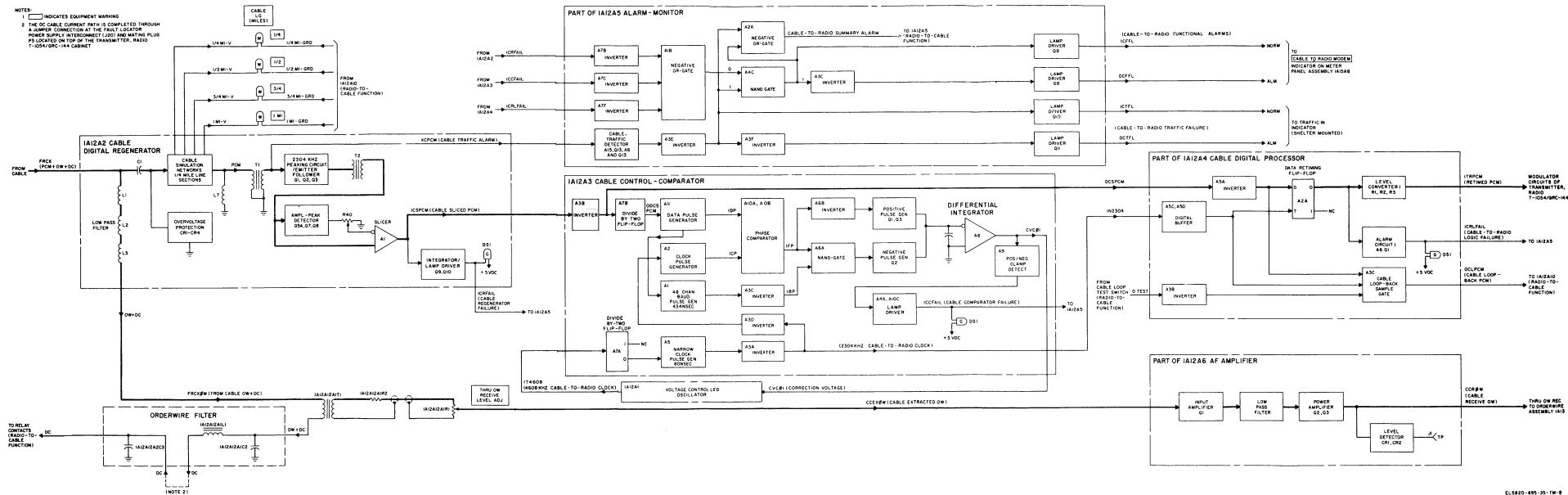

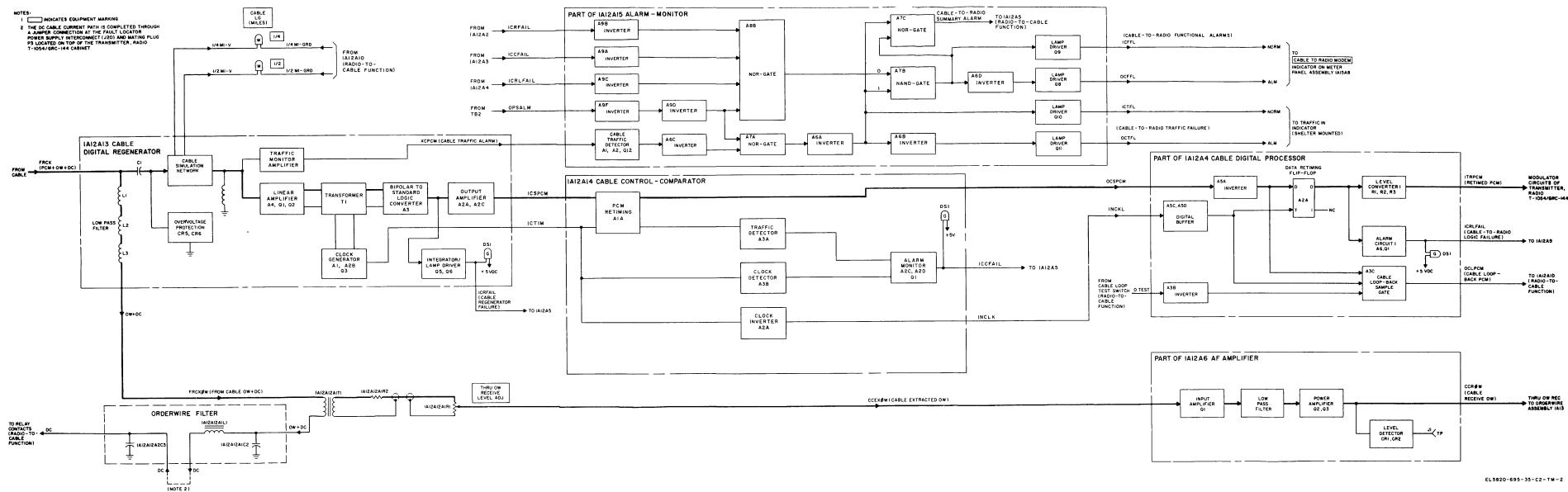

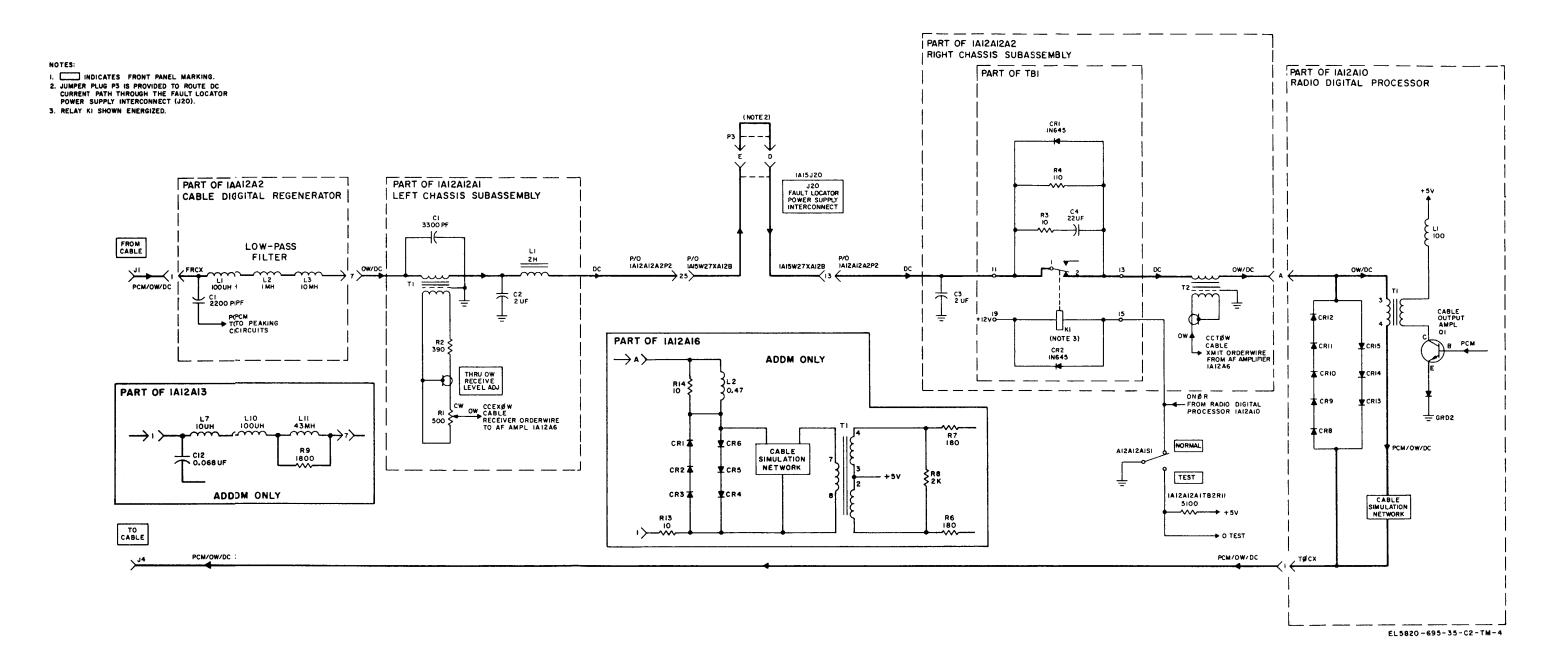

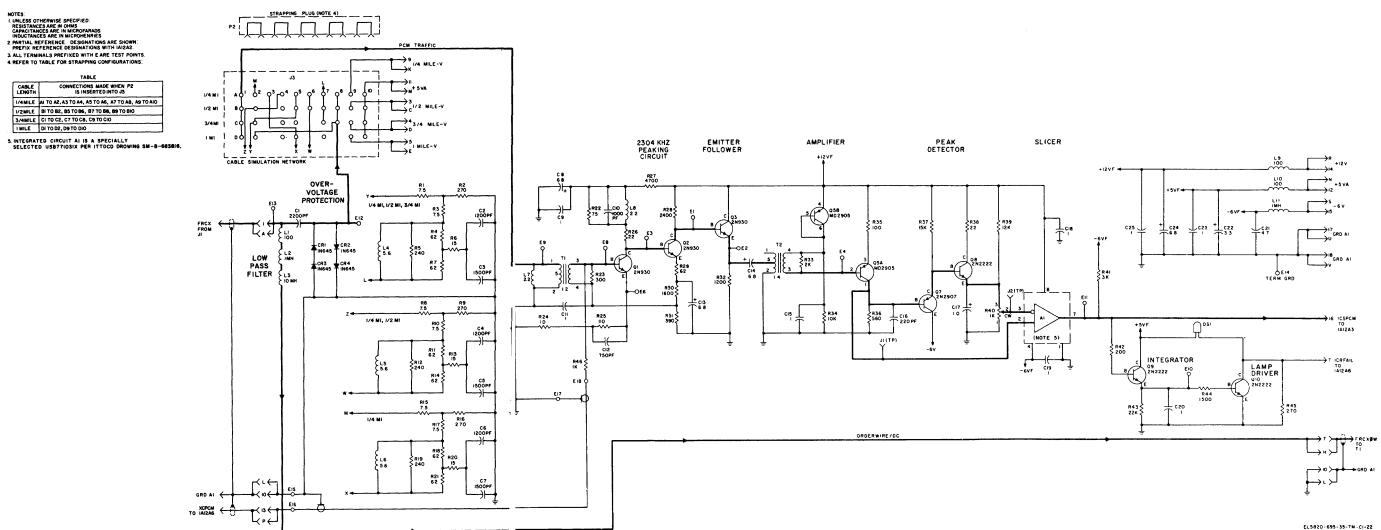

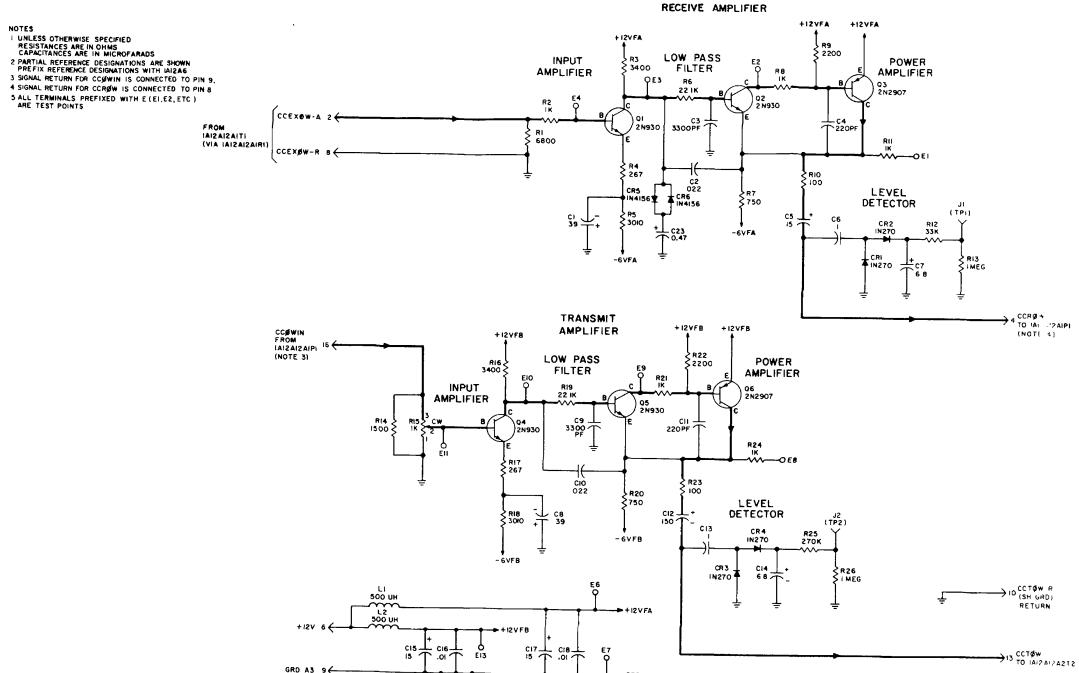

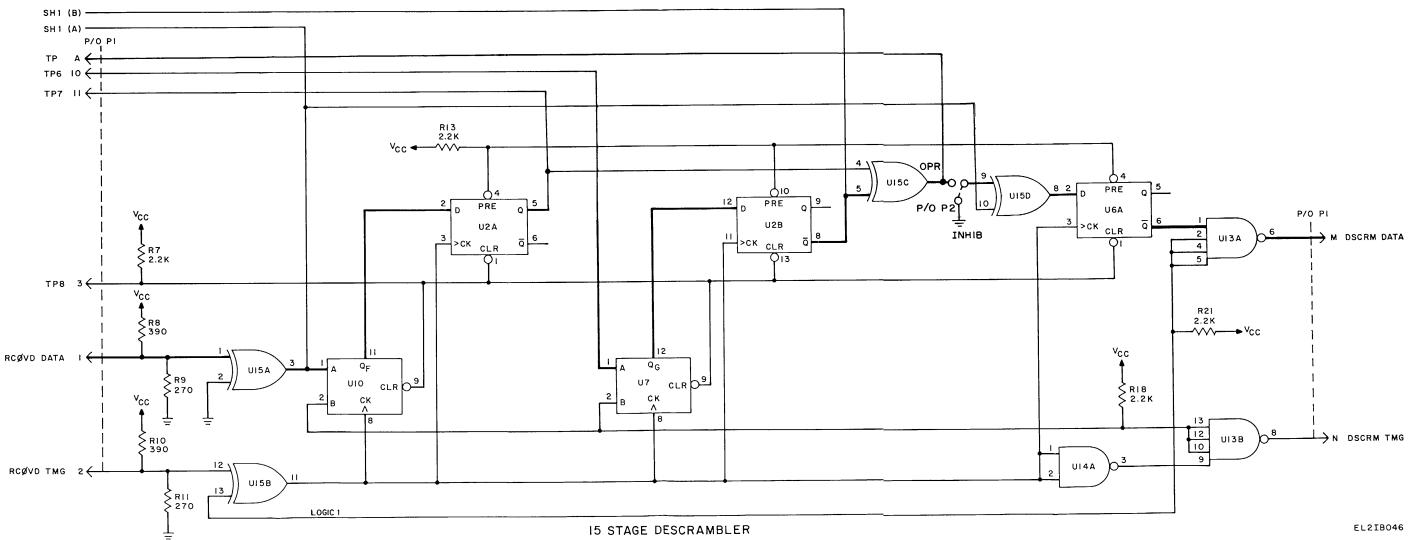

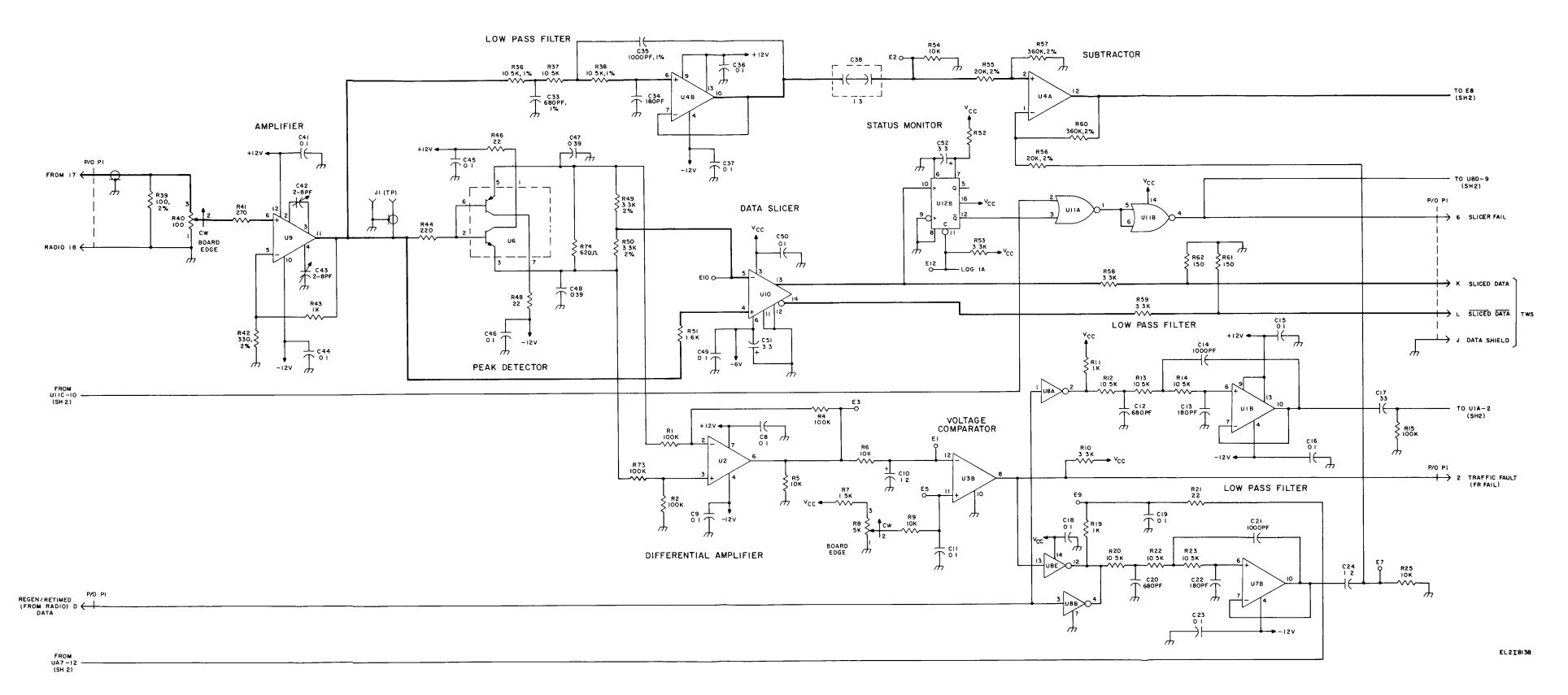

| 5-30                    | Cable digital regenerator 1A12A2, schematic diagrams,<br>synchronous mode                                                      | 5-73    |

| 5-30.1                  | Cable digital regenerator 1A12A13 schematic diagram,<br>asynchronous mode                                                      | 5-74.1  |

| 5-31                    | Cable control comparator 1A12A3, schematic diagram,<br>synchronous mode                                                        | 5-75    |

| 5-31.1                  | Cable control comparator 1A12A14 schematic diagram,<br>asynchronous mode                                                       | 5-76.1  |

| 5-32                    | Cable digital processor 1A12A4, schematic diagram                                                                              | 5-77    |

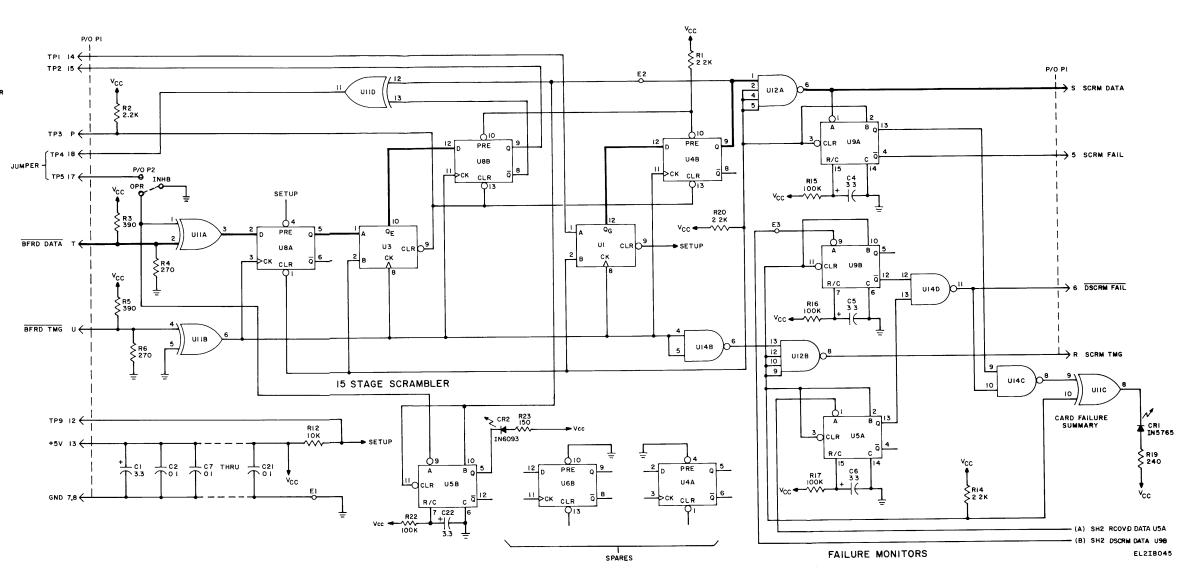

| 5-33                    | Alarm monitor 1A12A5, schematic diagram, synchronous<br>mode                                                                   | 5-79    |

| 5-33.1                  | Alarm monitor 1A12A15, schematic diagram, asynchronous mode                                                                    | 5-80.1  |

| 5-34                    | AF amplifier 1A12A6, schematic diagram                                                                                         | 5-81    |

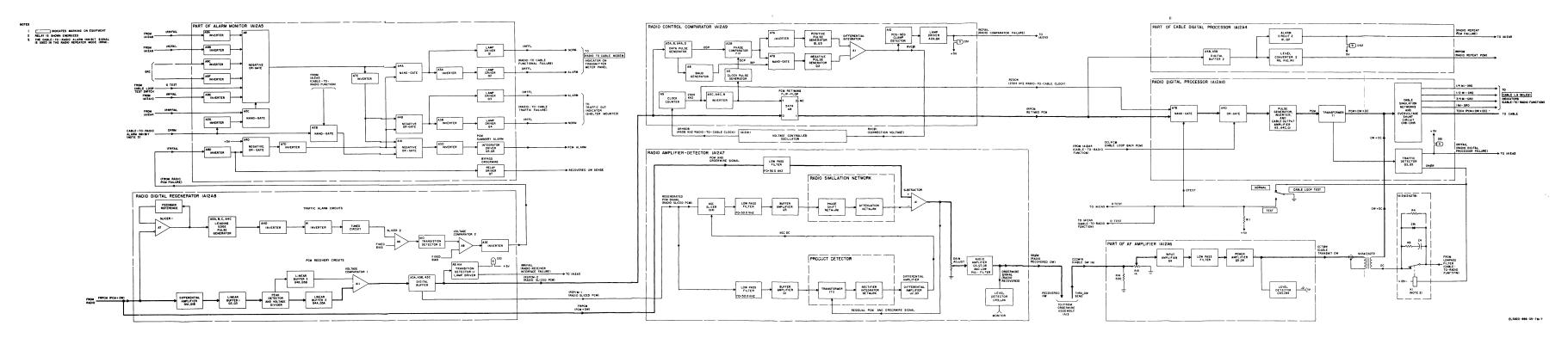

| 5-35                    | Radio-amplifier detector 1A12A7, schematic diagram                                                                             | 5-83    |

| 5-36                    | Radio digital regenerator 1A12A8, schematic diagram                                                                            | 5-85    |

| 5-37                    | Radio control comparator 1A12A9, schematic diagram                                                                             | 5-87    |

| 5-38                    | Radio digital processor 1A12A10, schematic diagram,<br>synchronous mode                                                        | 5-89    |

| 5-38.1                  | Radio digital processor 1A12A16, schematic diagram,                                                                            |         |

| 5-38.2                  | asynchronous mode<br>Digital data combiner 1A12, interconnecting diagram                                                       | 5-89.1  |

|                         |                                                                                                                                | 5-89.3  |

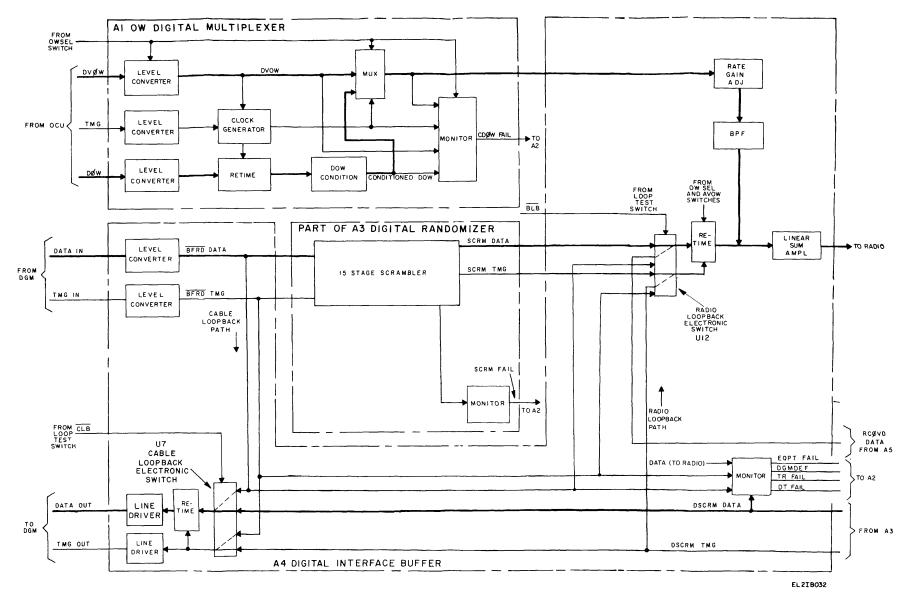

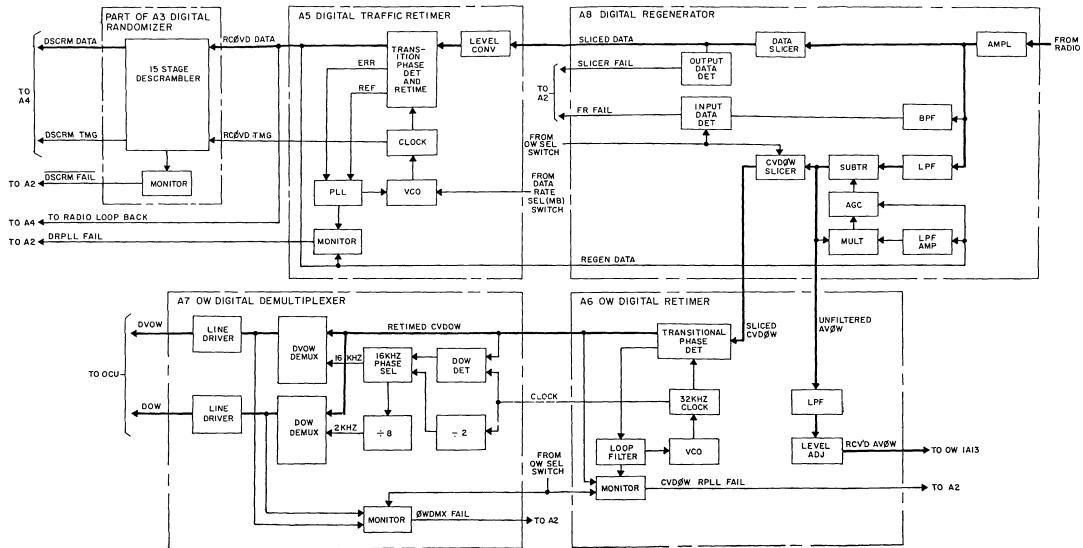

| 5-38.3(1)               | Multiplexer, digital orderwire 1A12A1, schematic<br>diagram (Sheet 1 of 2)<br>Multiplexer, digital orderwire 1A12A1, schematic | 5-89.5  |

| 5-38.3(2)               | Multiplexer, digital orderwire 1A12A1, schematic<br>diagram (Sheet 2 of 2)                                                     | 5-89.7  |

|   | <b>-</b> '              | LIST OF ILLUSTRATIONS - Continued                                                    |                 |

|---|-------------------------|--------------------------------------------------------------------------------------|-----------------|

|   | Figure<br><u>Number</u> | Title                                                                                | Page            |

|   | 5-38.4(1)               | Combiner alarm status 1A12A2, schematic diagram                                      | 5 90 0          |

|   | 5-38.4(2)               | (Sheet 1 of 2)<br>Combiner alarm status 1A12A2, schematic diagram                    | 5-89.9          |

|   | 5-38.5(1)               | (Sheet 2 of 2)<br>Digital randomizer 1A12A3, schematic diagram                       | 5-89.11         |

|   | 5-38.5(2)               | (Sheet 1 of 2)<br>Digital randomizer 1A12A3, schematic diagram                       | 5-89.13         |

|   | 5-38.6(1)               | (Sheet 2-of 2)<br>Buffer, digital interface 1A12A4, schematic diagram                | 5-89.15         |

|   | 5-38.6(2)               | (Sheet 1 of 3)<br>Buffer, digital interface 1A12A4, schematic diagram                | 5-89.17         |

|   |                         | (Sheet 2 of 3)                                                                       | 5-89.19         |

|   | 5-38.6(3)               | Buffer, digital interface 1A12A4, schematic diagram<br>(Sheet 3 of 3)                | 5-89.21         |

|   | 5-38.7(1)               | Retimer digital traffic 1A12AS, schematic diagram<br>(Sheet 1 of 2)                  | 5-89.23         |

|   | 5-38.7(2)               | Retimer digital traffic 1A12A5, schematic diagram<br>(Sheet 2 of 2)                  | 5-89.25         |

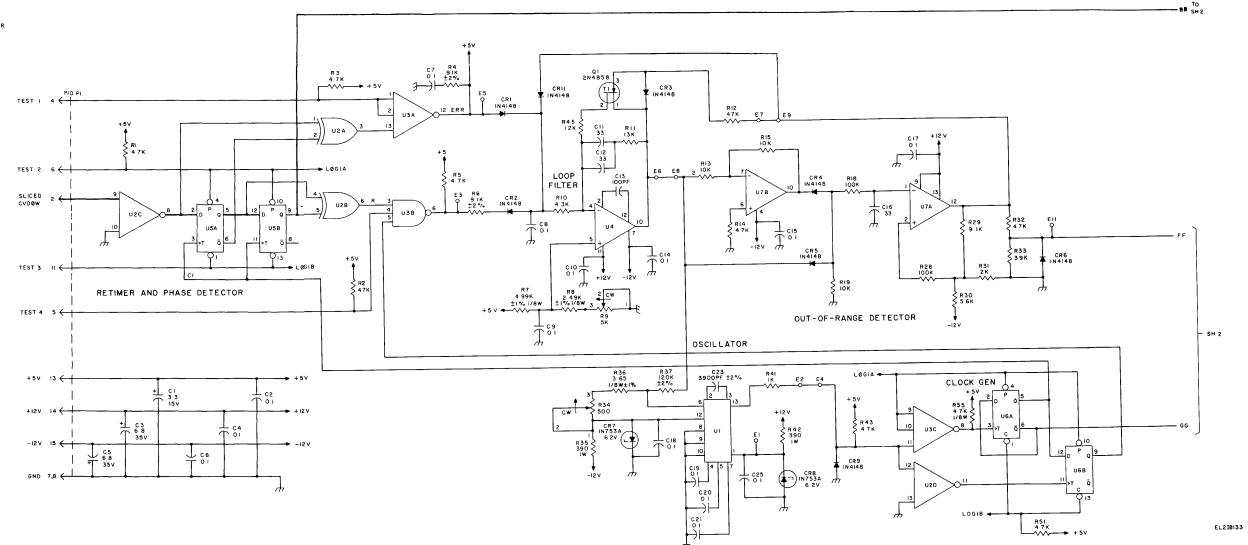

|   | 5-38.8(1)               | Retimer, digital orderwire 1A12A6, schematic diagram<br>(Sheet 1 of 2)               | 5-89.27         |

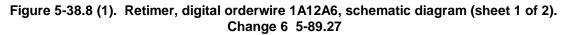

|   | 5-38.8(2)               | Retimer, digital orderwire 1A12A6, schematic diagram                                 | 5-89.29         |

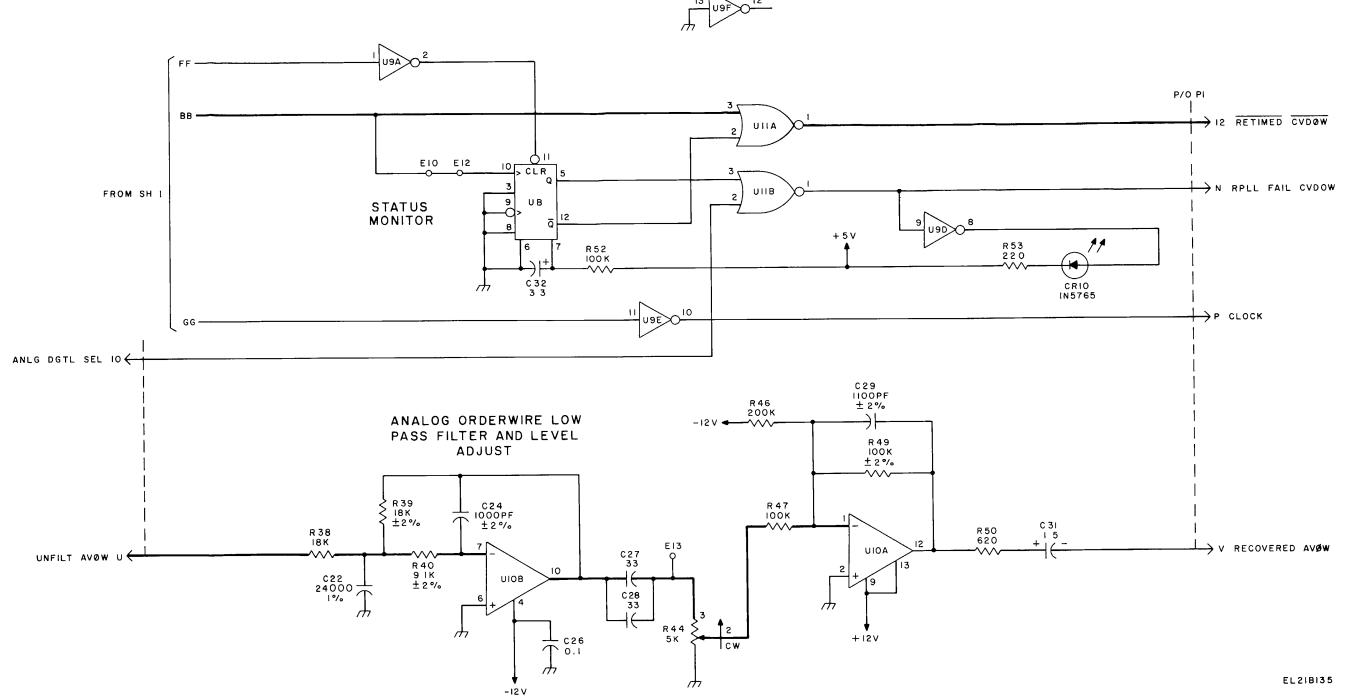

|   | 5-38.9                  | (Sheet 2 of 2)<br>Demultiplexer, digital orderwire, 1A12A7, schematic                |                 |

|   | 5-38.10(1)              | diagram<br>Regenerator, digital 1A12A8, schematic diagram                            | 5-89.31         |

|   | 5-38.10(2)              | (Sheet 1 of 2)<br>Regenerator, digital 1A12A8, schematic diagram                     | 5-89.33         |

|   | 5-39                    | (Sheet 2 of 2)<br>Orderwire assembly 1A13, interconnecting diagram                   | 5-89.35<br>5-91 |

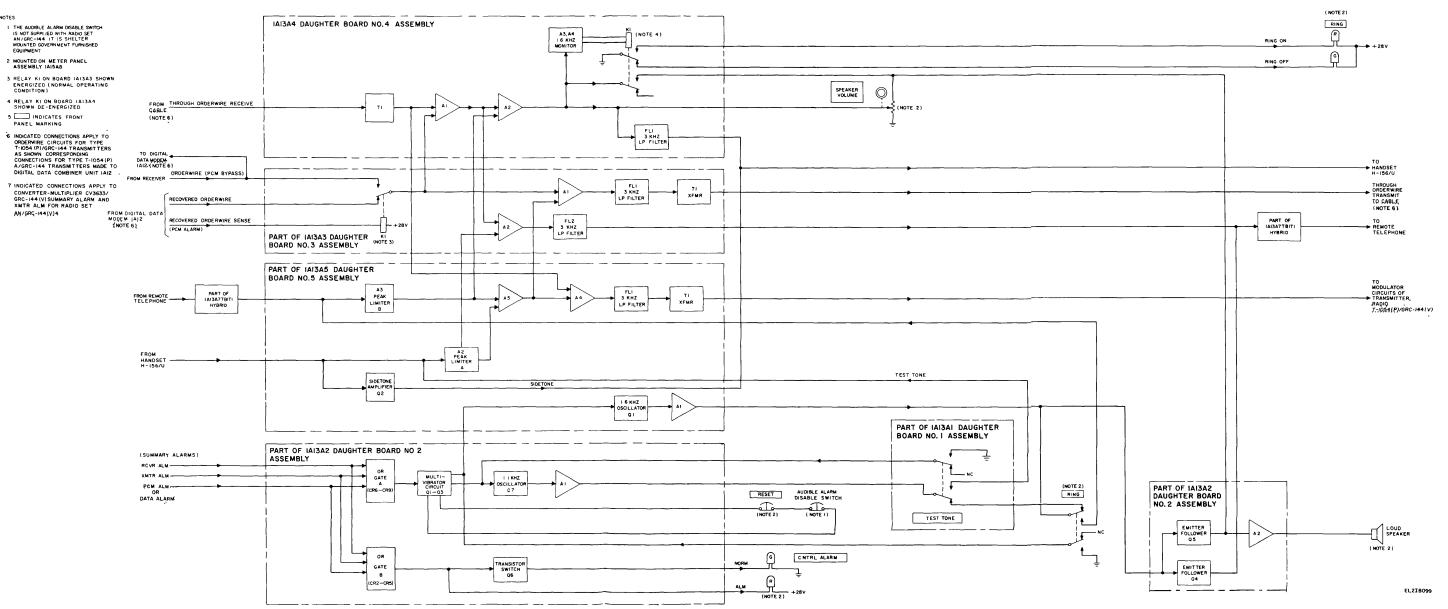

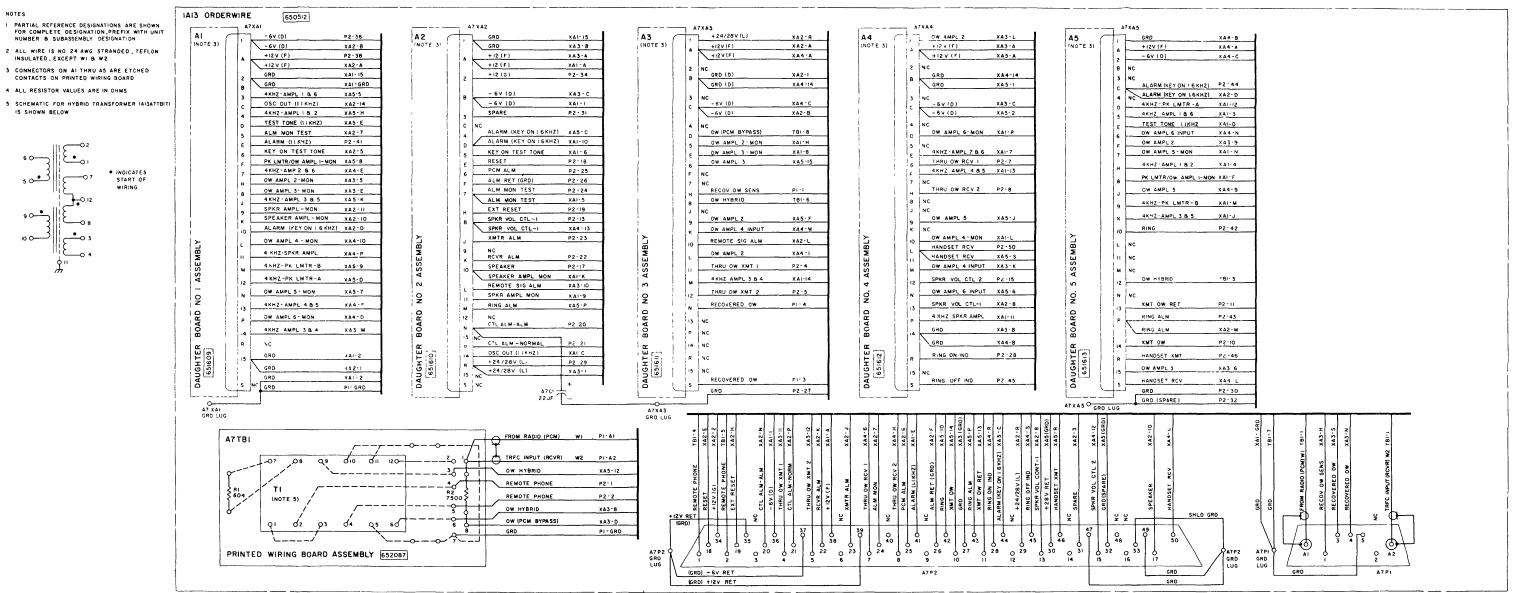

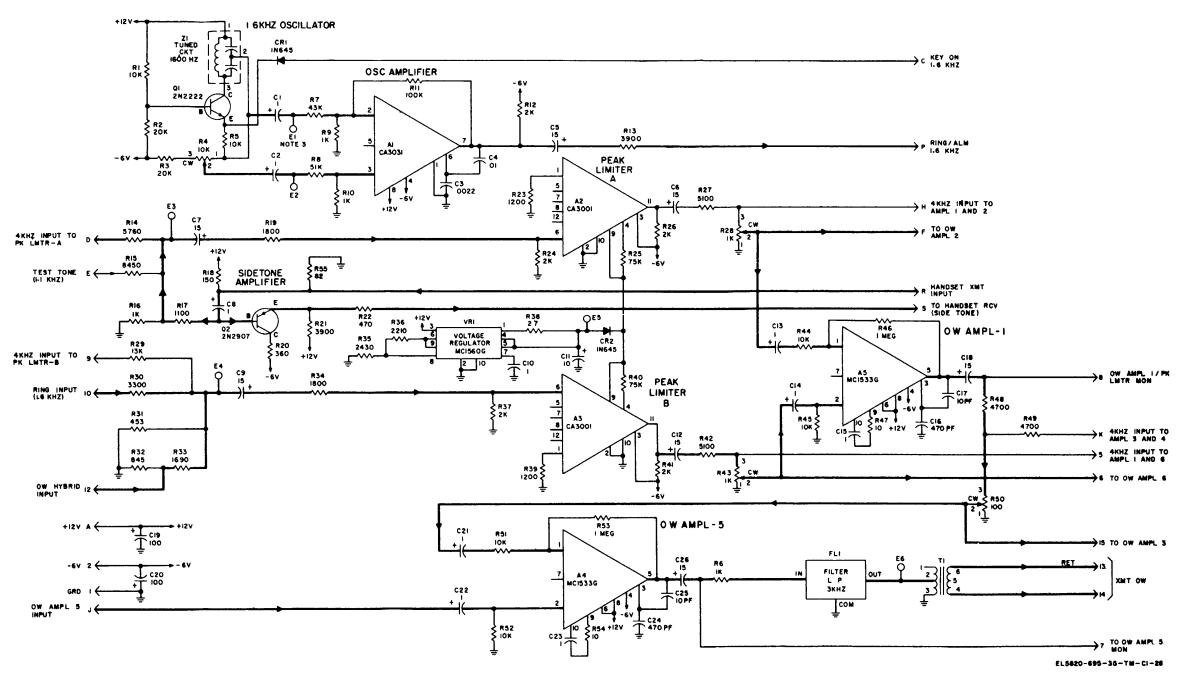

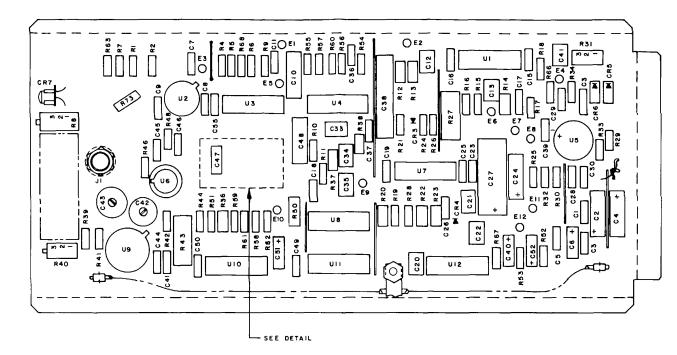

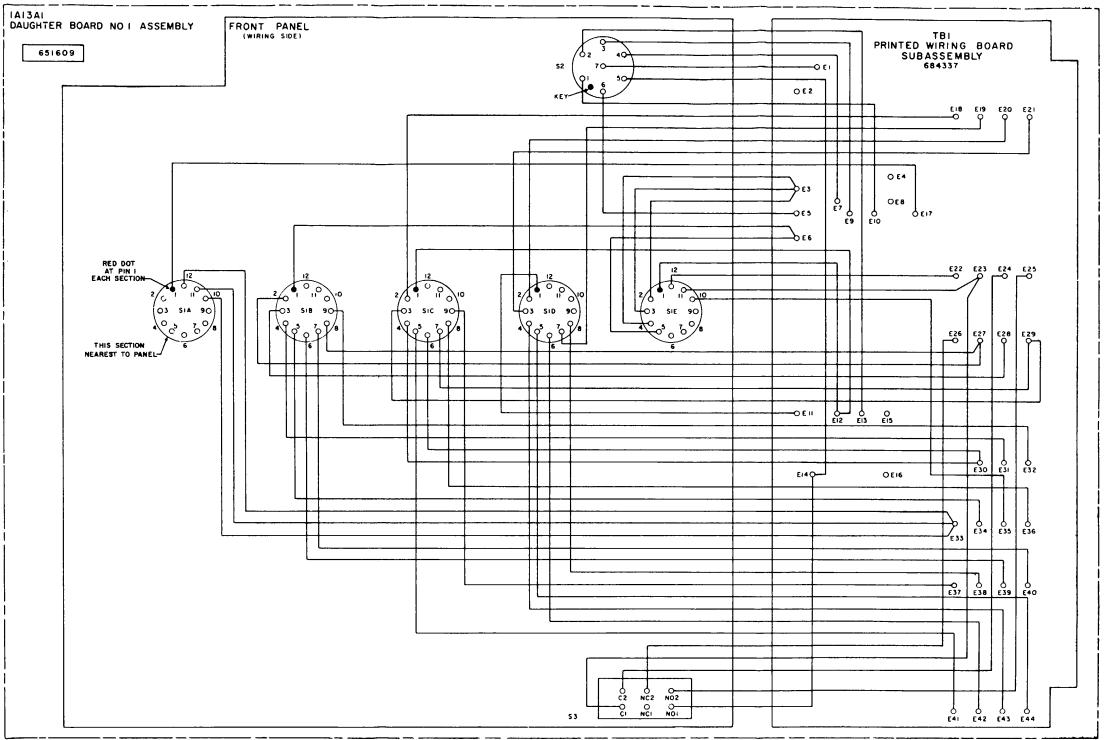

| 1 | 5-40                    | Daughter Board No. 1 assembly 1A13A1, schematic                                      |                 |

|   | 5-41                    | diagram<br>Daughter Board No. 2 assembly 1A13A2 schematic                            | 5-93            |

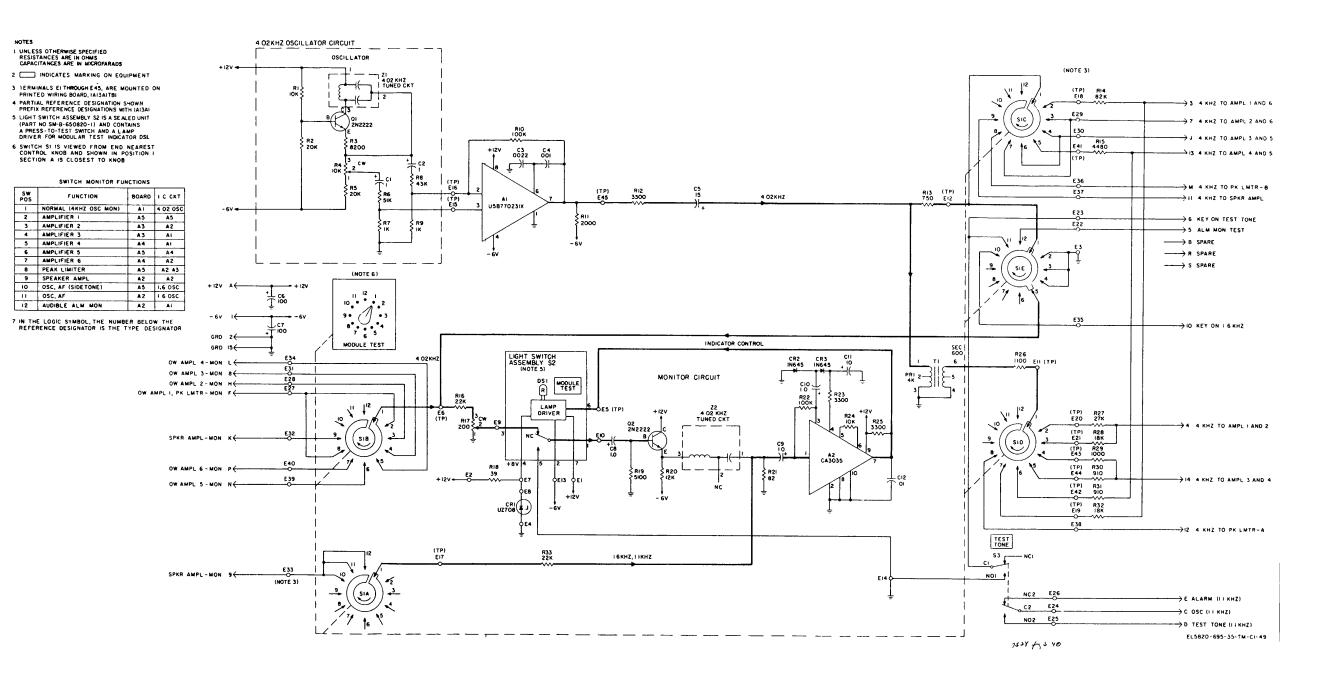

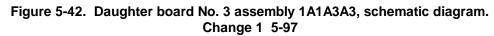

|   | 5-42                    | diagram<br>Daughter Board No. 3 assembly 1A13A3 schematic                            | 5-95            |

|   | 5-43                    | diagram<br>Daughter Board No. 4 assembly 1A13A4 schematic                            | 5-97            |

|   | 5-44                    | diagram<br>Daughter Board No. 5 assembly 1A13A5, schematic                           | 5-99            |

|   | 5-45(1)                 | diagram<br>Electrical frequency synthesizer 1A14/2A14,                               | 5-101           |

|   | 5-45(2)                 | interconnecting diagram (Part 1 of 3)<br>Electrical frequency synthesizer 1A14/2A14, | 5-103           |

|   |                         | interconnecting diagram (Part 2 of 3)                                                | 5-105           |

|   | 5-45(3)                 | Electrical frequency synthesizer 1A14/2A14,<br>interconnecting diagram (Part 3 of 3) | 5-107           |

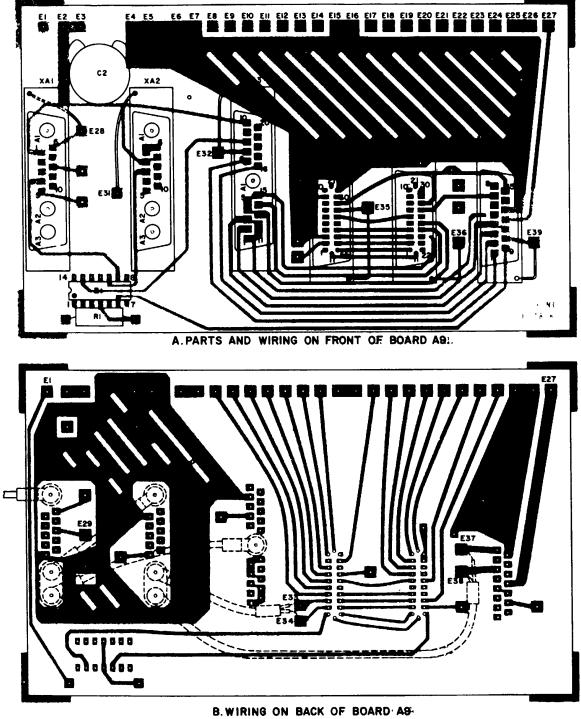

|   | 5-46                    | Radio frequency oscillator 1A14A1/2A14A1, schematic<br>diagram                       | 5-109           |

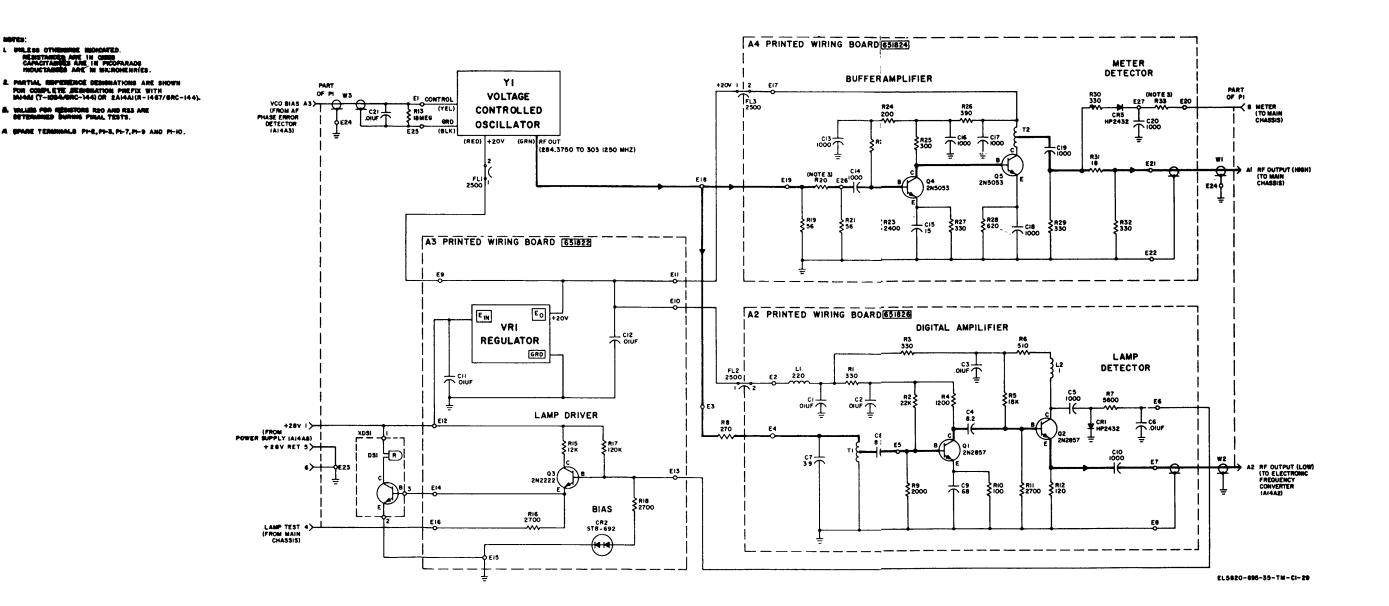

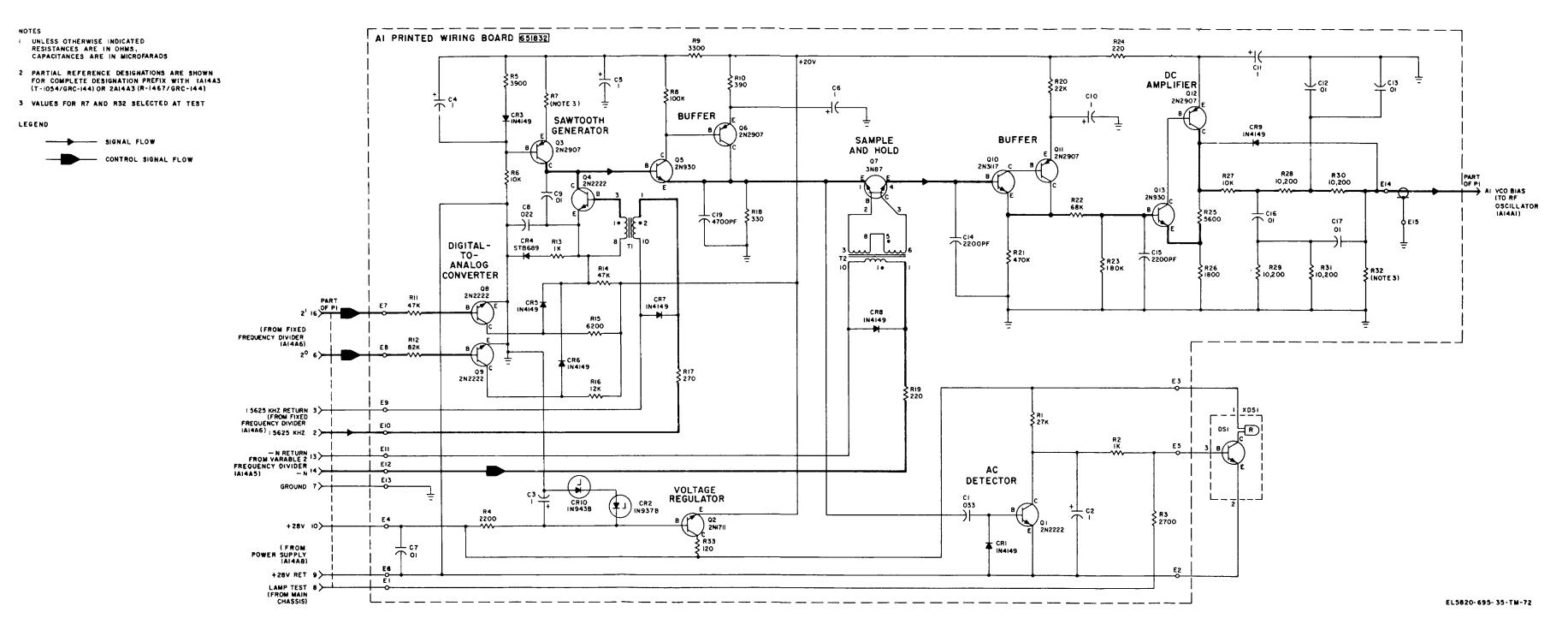

|   | 5-47                    | Electronic frequency converter board 1A14A2A1/2A14A2A1, schematic diagram            | 5-111           |

|   |                         |                                                                                      |                 |

|               | LIST OF ILLUSTRATIONS - Continued                                                                 |                |

|---------------|---------------------------------------------------------------------------------------------------|----------------|

| Figure        | Title                                                                                             | Dere           |

| <u>Number</u> | Title                                                                                             | <u>Page</u>    |

| 5-48          | Electronic frequency converter board 1A14A2A2/<br>2A14A2A2, schematic diagram                     | 5-113          |

| 5-49          | Audio frequency phase error detector 1A14A3/2A14A3,<br>schematic diagram                          | 5-115          |

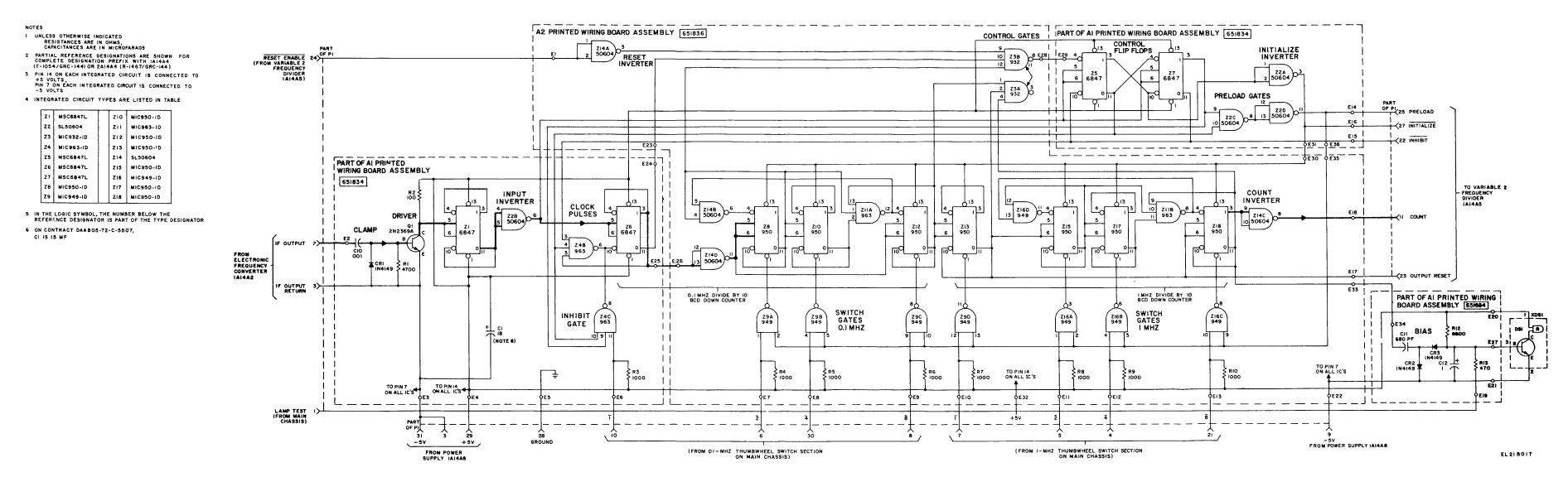

| 5-50          | Variable 1 frequency divider 1A14A4/2A14A4, schematic<br>diagram                                  | 5-117          |

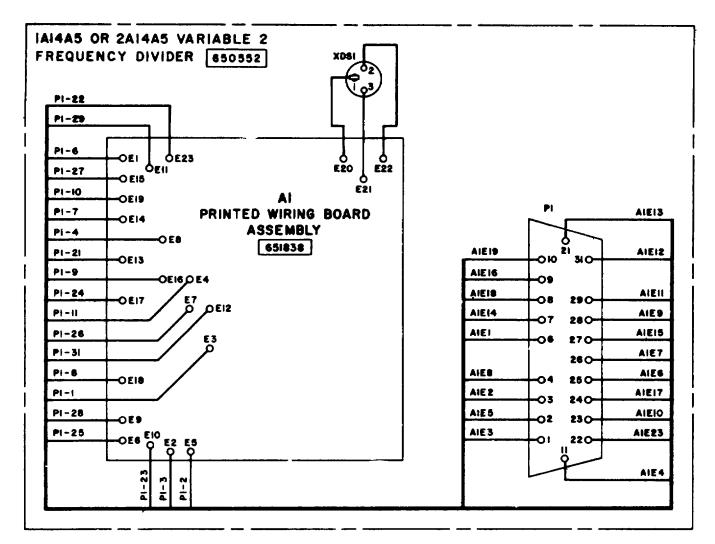

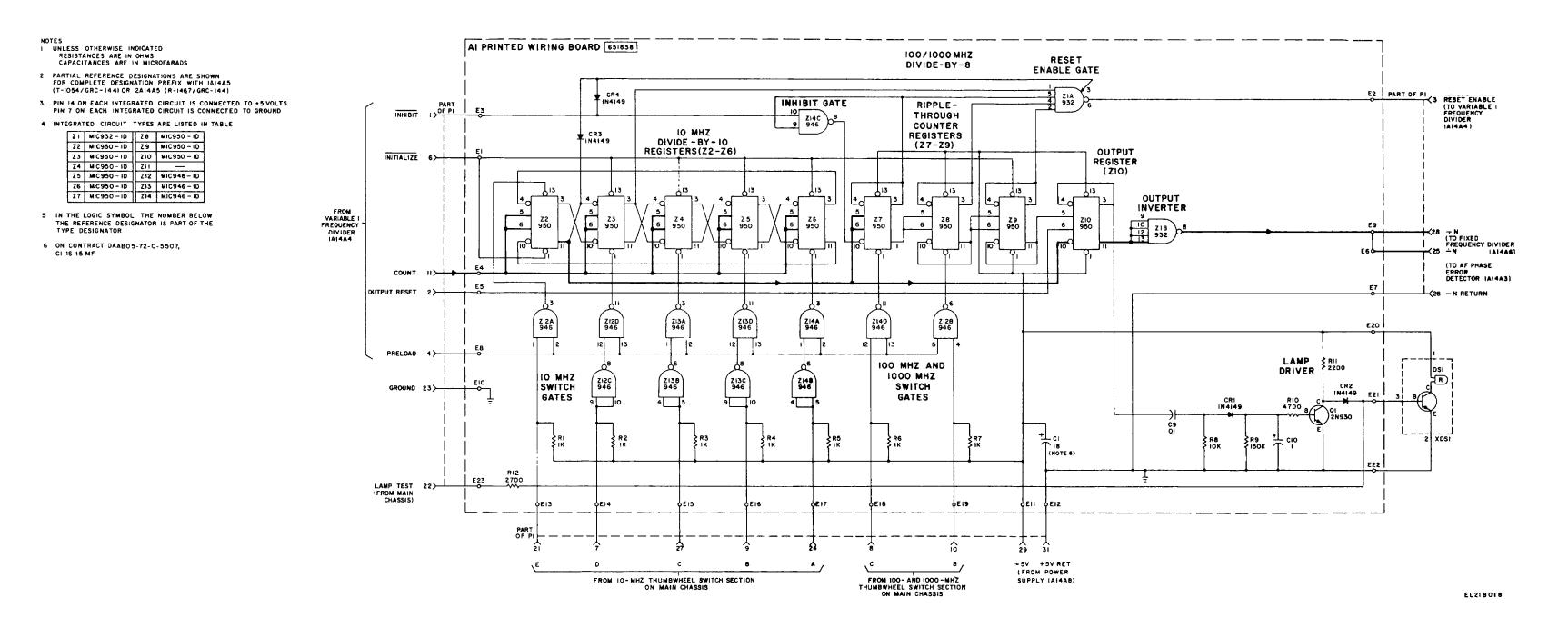

| 5-51          | Variable 2 frequency divider 1A14A5/2A14A5, schematic<br>diagram                                  | 5-119          |

| 5-52          | Variable 2 frequency divider 1A14A5/2A14A5 timing<br>during jump count                            | 5-121          |

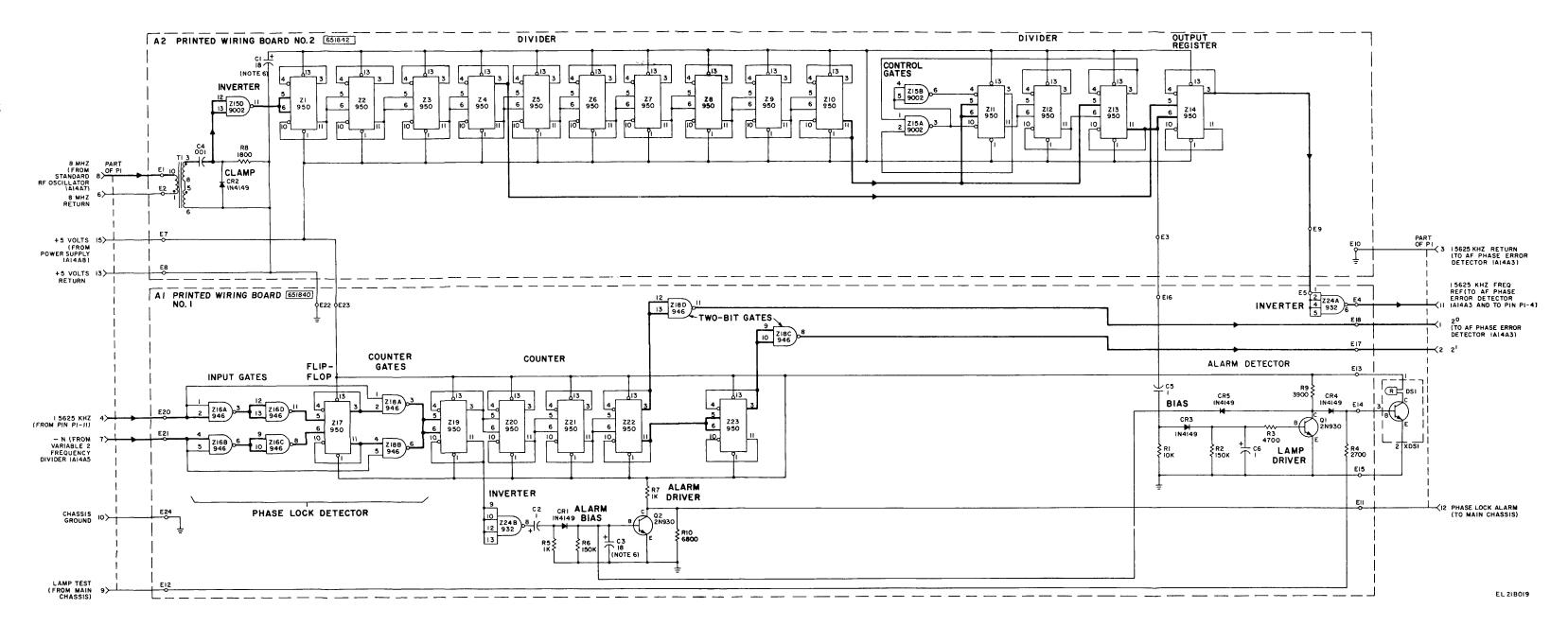

| 5-53          | Fixed frequency divider 1A14A6/2A14A6 schematic                                                   | E 400          |

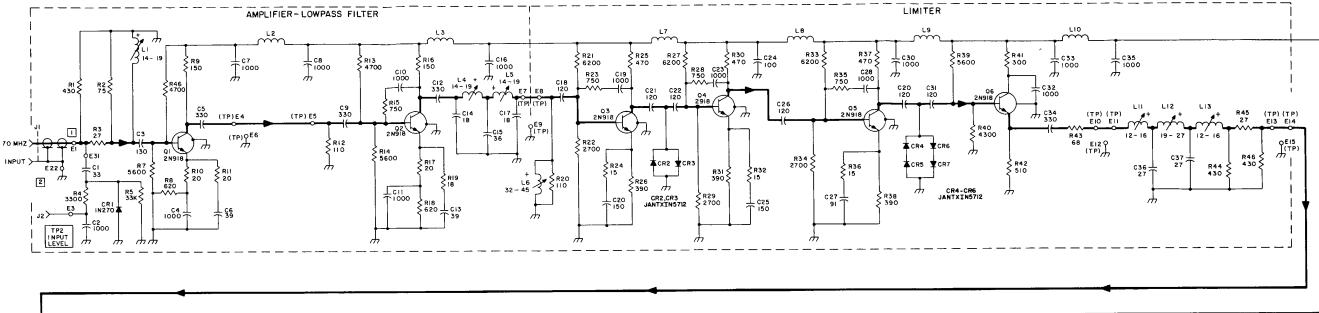

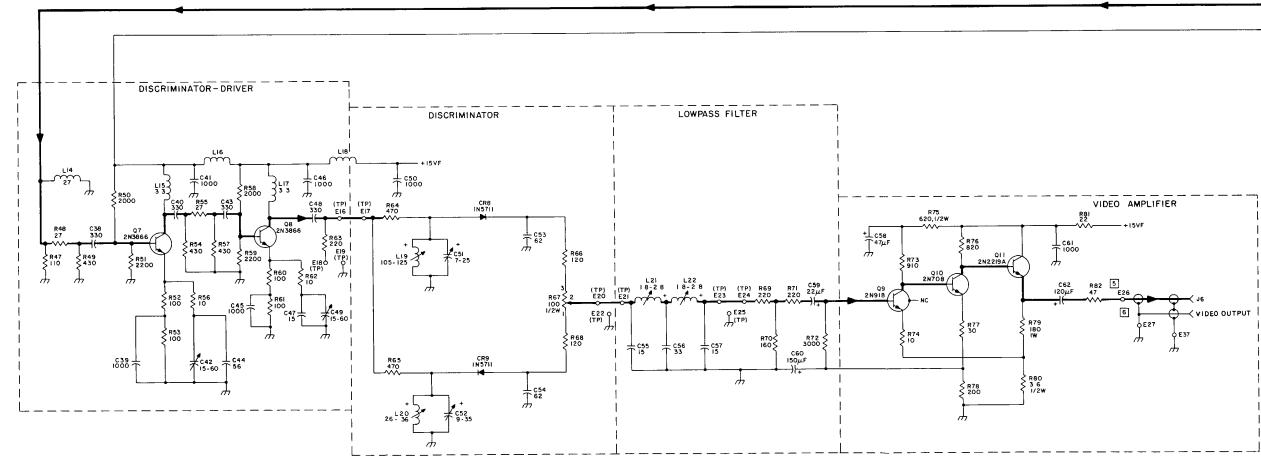

| 5-54          | diagram<br>Demodulator 2A4, schematic diagram                                                     | 5-123<br>5-125 |

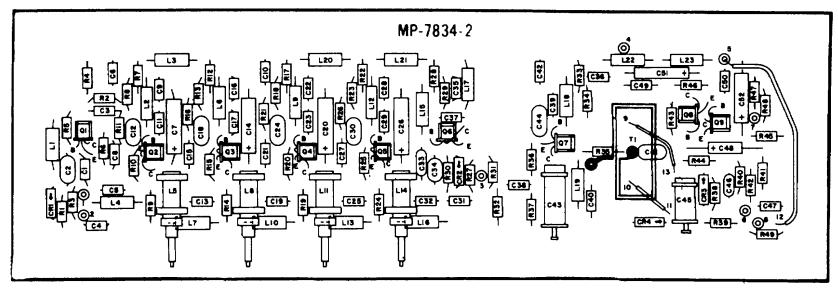

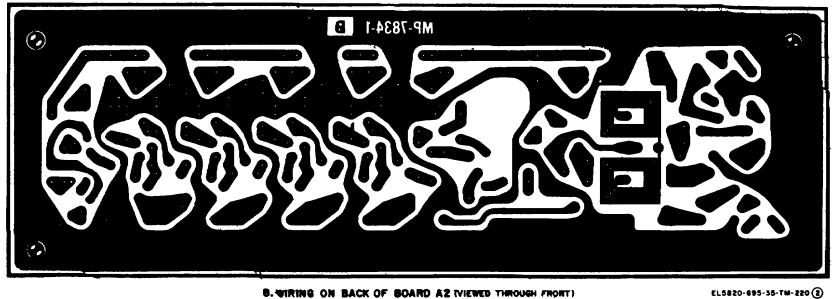

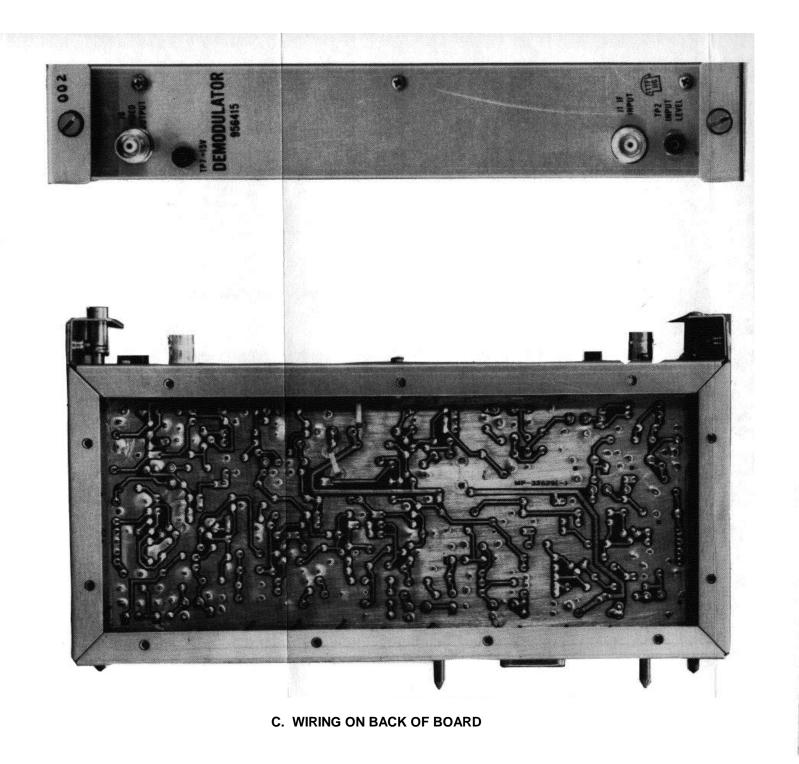

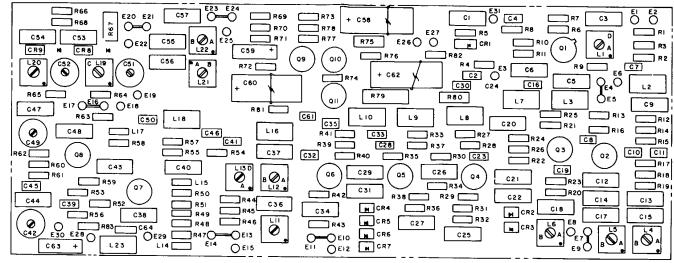

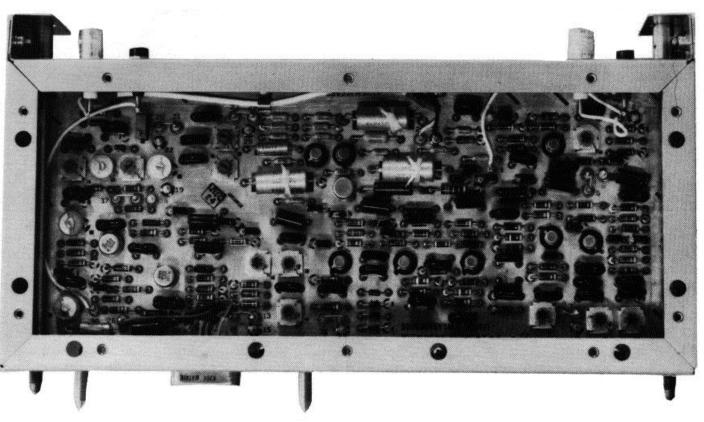

| 5-54.1        | Demodulator 2A4 (956415), schematic diagram                                                       | 5-125.1        |

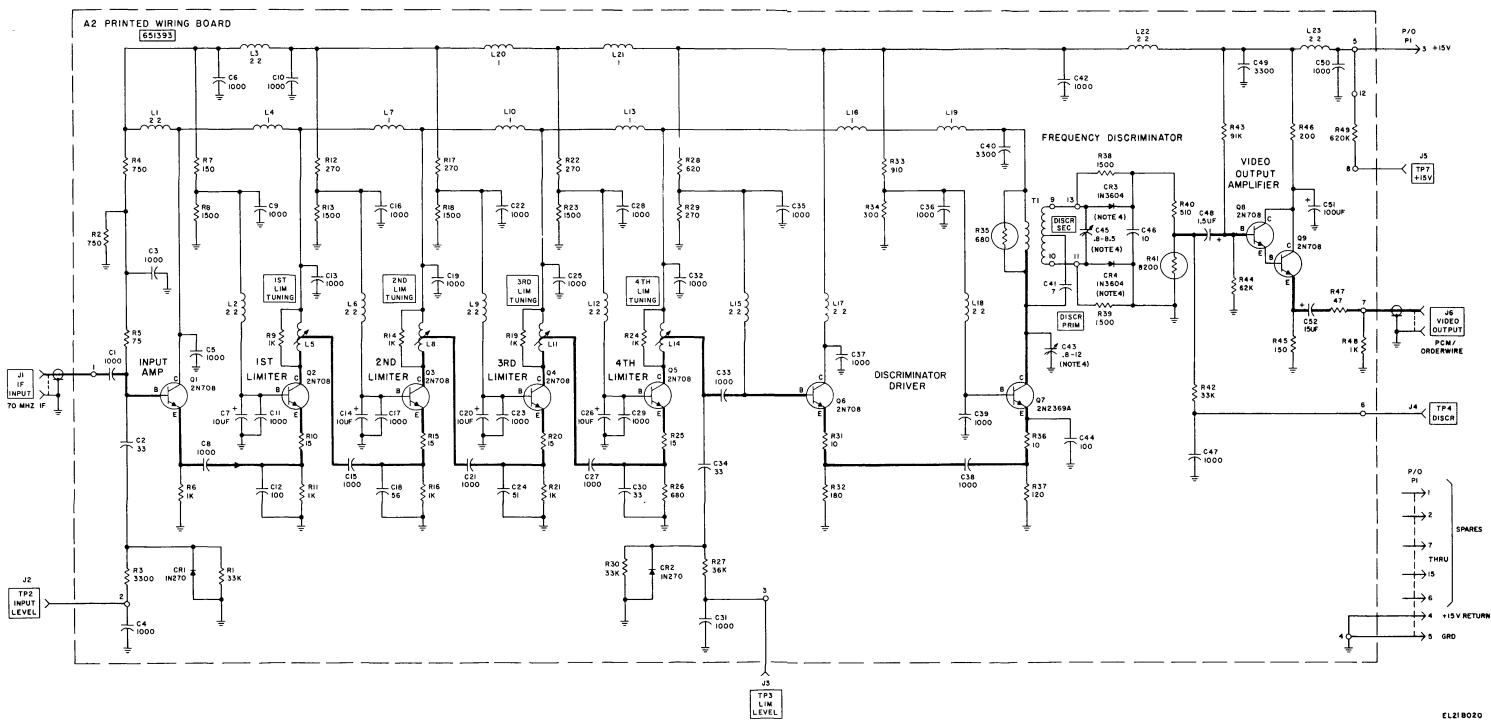

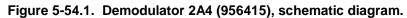

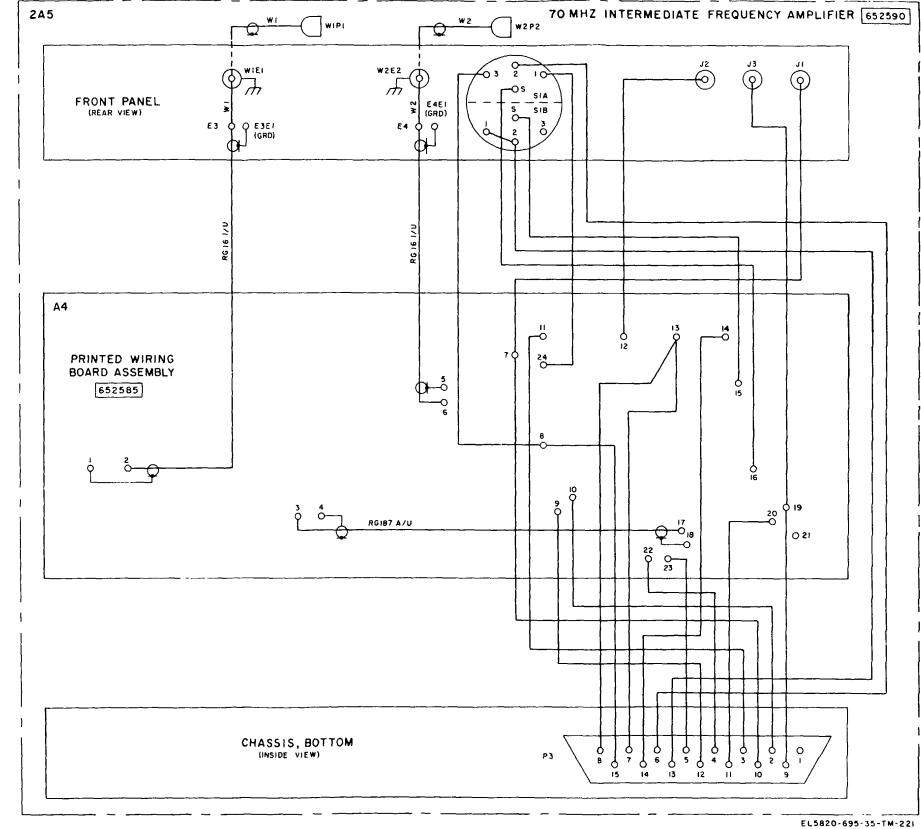

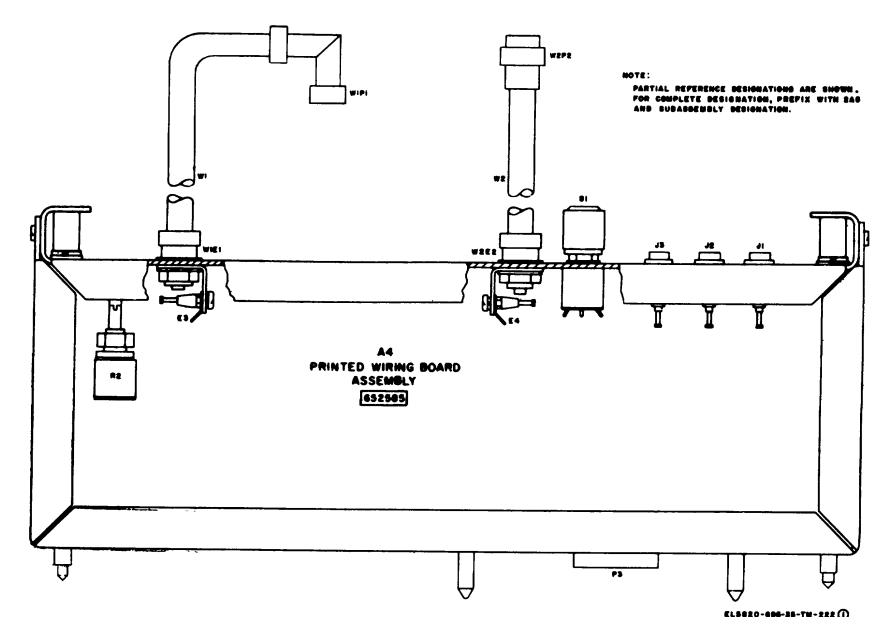

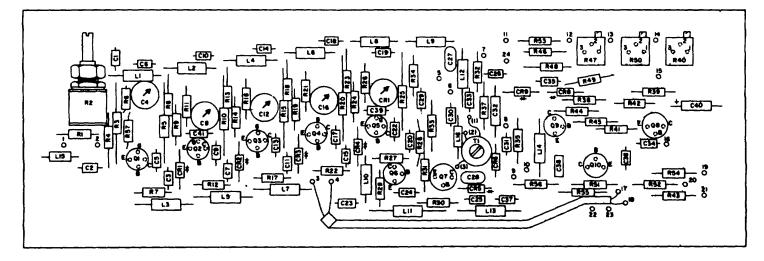

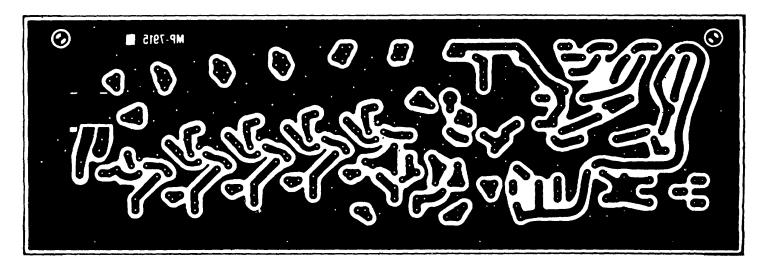

| 5-55          | 70 MHz intermediate frequency amplifier 2A5,                                                      | 5-125.1        |

| 5-55          | schematic diagram                                                                                 | 5-127          |

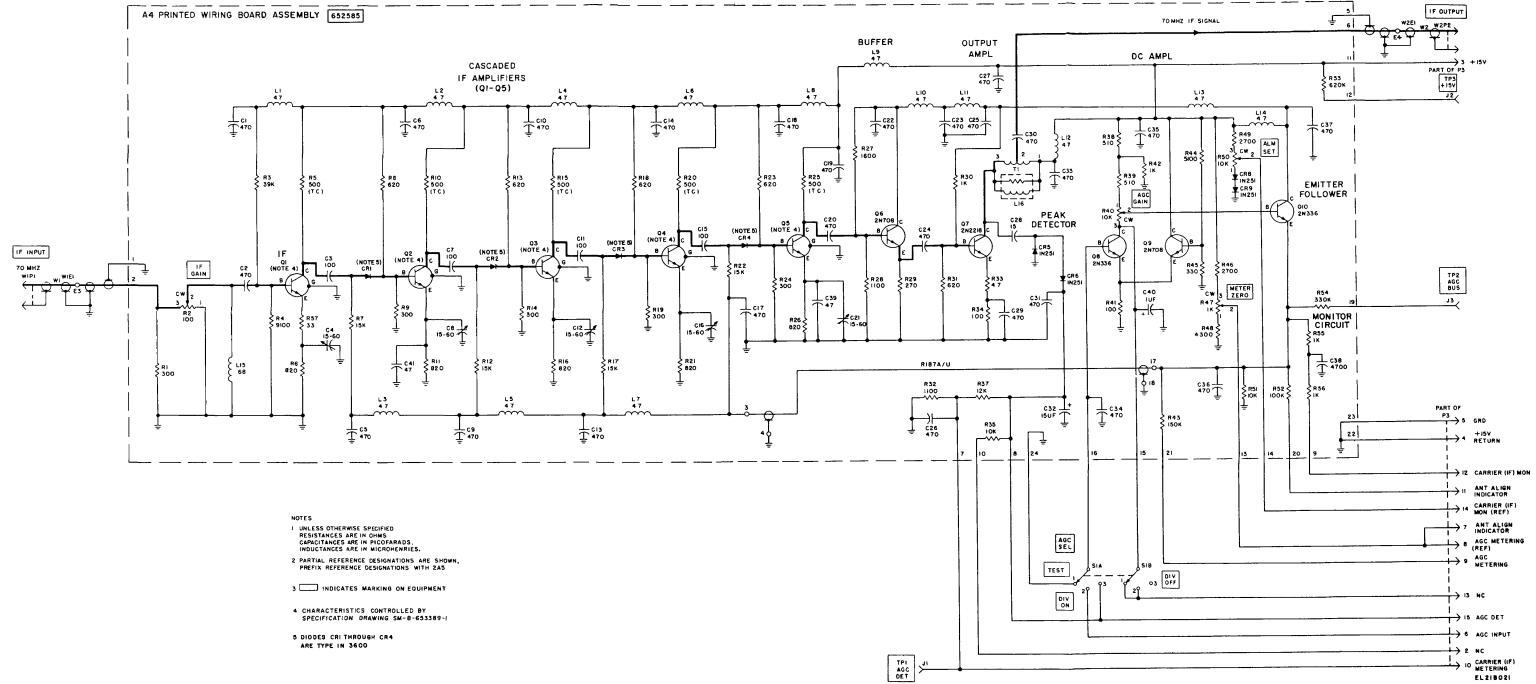

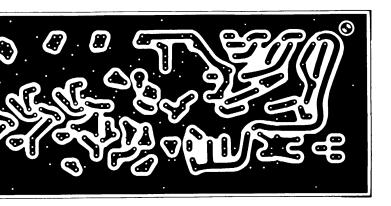

| 5-55.1        | 70 MHz intermediate frequency amplifier 2A5 (956423),                                             | 5-127          |

| 0 00.1        | schematic diagram                                                                                 | 5-127.1        |

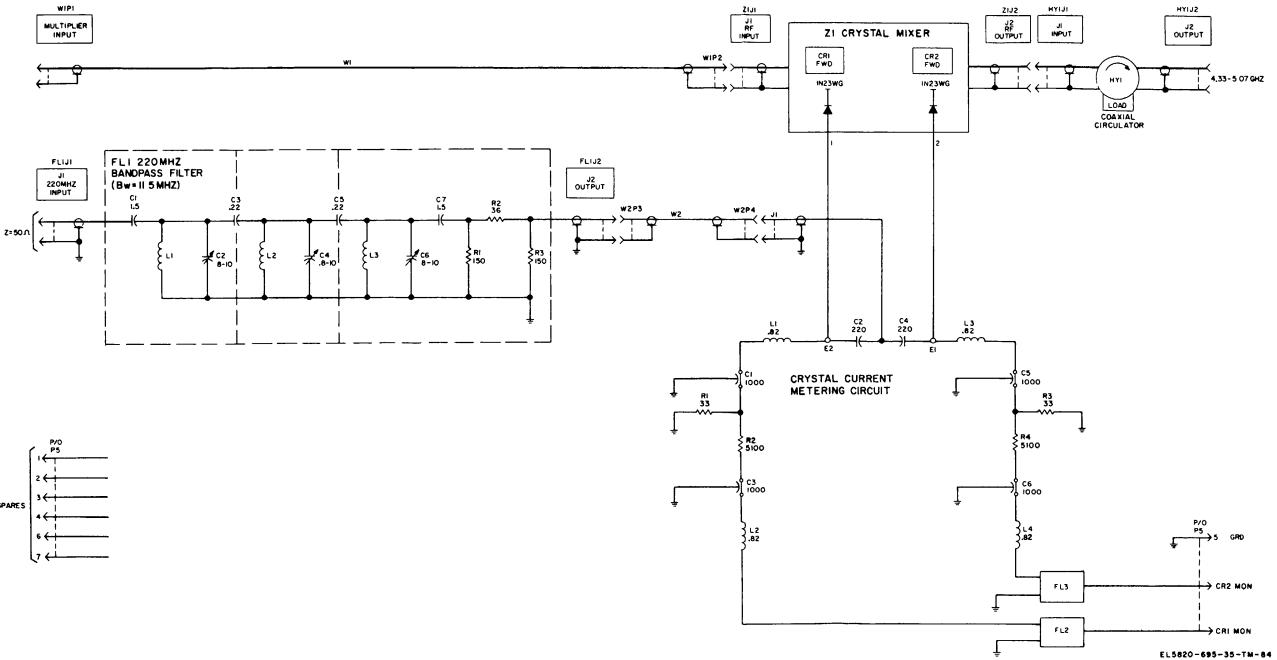

| 5-56          | Receiver frequency mixer stage 2A8, schematic diagram                                             | 5-129          |

| 5-57          | Amplifier-frequency multiplier 2A10, schematic                                                    | 0 120          |

| 0.01          | diagram                                                                                           | 5-131          |

| 5-58          | 220 MHz frequency multiplier-OSC 2A13, schematic                                                  | 0 101          |

|               | diagram                                                                                           | 5-133          |

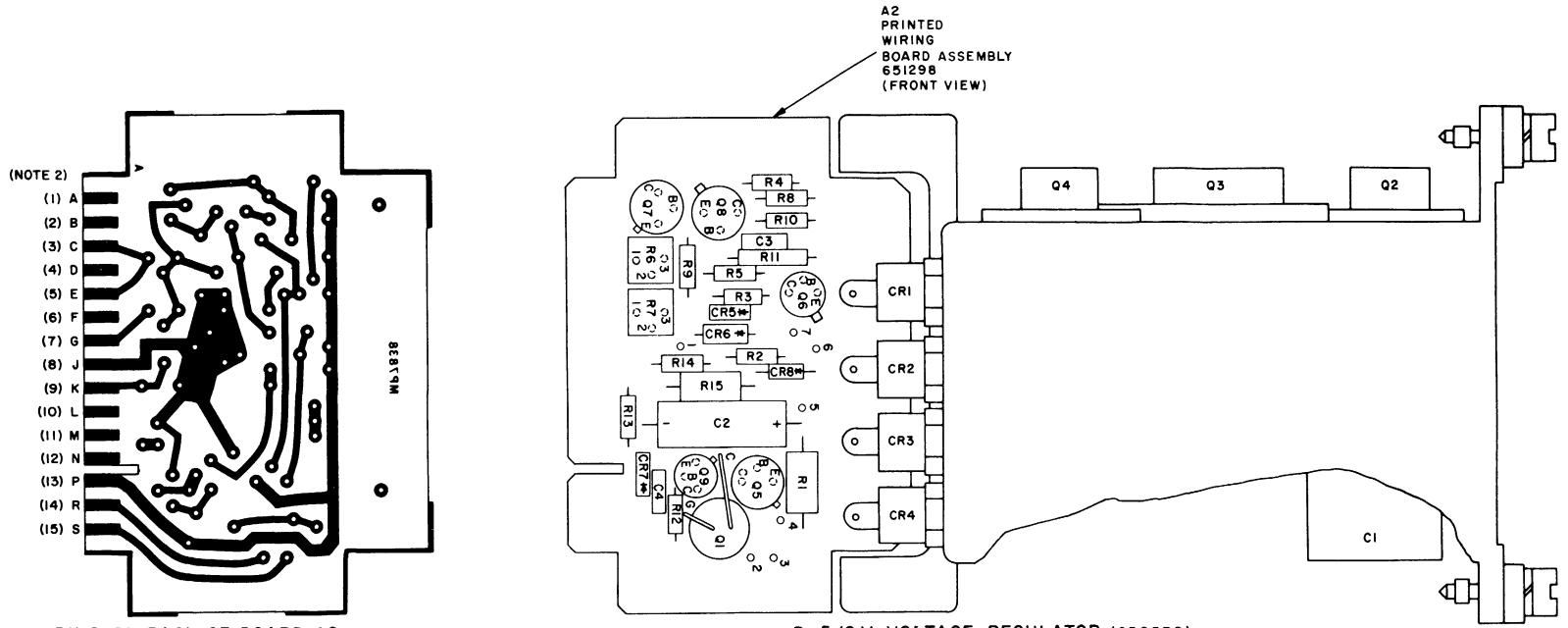

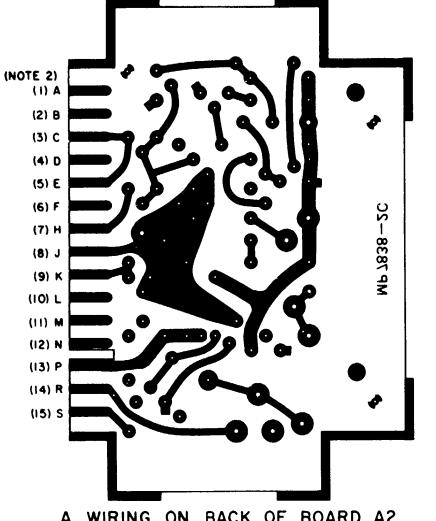

| 5-59(1)       | 5/6V voltage regulator 1A1A7 through 1A1A4, parts                                                 |                |

|               | location and printed wiring diagram (Part 1 of 2)                                                 | 5-135          |

| 5-59(2)       | 5/6V voltage regulator 1A1A7 through 1A1A4, parts                                                 |                |

|               | location and printed wiring diagram (Part 2 of 2)                                                 | 5-137          |

| 5-60(1)       | 12V voltage regulator 1A1A6 through 1A1A9 and 2A1A3,                                              |                |

|               | parts location and printed wiring diagram                                                         | E 400 4        |

| F 60(2)       | (Part 1 of 2)                                                                                     | 5-138.1        |

| 5-60(2)       | 12V voltage regulator 1A1A6 through 1A1A9 and 2A1A3,<br>parts location and printed wiring diagram |                |

|               | (Part 2 of 2)                                                                                     | 5-138.3        |

| 5-61(1)       | 15/28V voltage regulator 1A1A10 through 1A1A12,                                                   | 0 100.0        |

| 001(1)        | 2A1A1, 2A1A2 and 2A1A4 parts location and printed                                                 |                |

|               | wiring diagram (Part 1 of 2)                                                                      | 5-138.5        |

| 5-61(2)       | 15/28V voltage regulator 1A1A1D through 1A1A12,                                                   | 0 10010        |

| 0 0 1 (=)     | 2A1A1, 2A1A2 and 2A1A4 parts location and printed                                                 |                |

|               | wiring diagram (Part 2 of 2)                                                                      | 5-138.7        |

| 5-62          | 100 MHz radio frequency oscillator 1A2, wiring                                                    |                |

|               | diagram                                                                                           | 5-139          |

| 5-63          | 100 MHz radio frequency oscillator 1A2 parts location                                             | 5-141          |

| 5-64          | Attenuator assembly 1A3, parts location and printed                                               |                |

|               | wiring diagram                                                                                    | 5-143          |

| 5-64.1        | Attenuator assembly 1A3 (956429), parts location and                                              |                |

|               | printed wiring diagram                                                                            | 5-143.1        |

| 5-64.2        | Attenuator assembly 1A3 (956431), parts location and                                              |                |

|               | printed wiring diagram                                                                            | 5-143.3        |

| 5-65          | Alarm monitor 1A5/2A12, wiring diagram                                                            | 5-145          |

| 5-66(1)       | Alarm monitor 1A5/2A12, parts location and printed                                                |                |

|               | wiring diagram (Part 1 of 2)                                                                      | 5-147          |

|               |                                                                                                   |                |

| Figure                  | LIST OF ILLUSTRATIONS - Continued                                |                    |

|-------------------------|------------------------------------------------------------------|--------------------|

| Figure<br><u>Number</u> | Title                                                            | <u>Page</u>        |

| 5-66(2)                 | Alarm monitor 1A5/2A12, parts location and printed               |                    |

|                         | wiring diagram (Part 2 of 2)                                     | 5-148              |

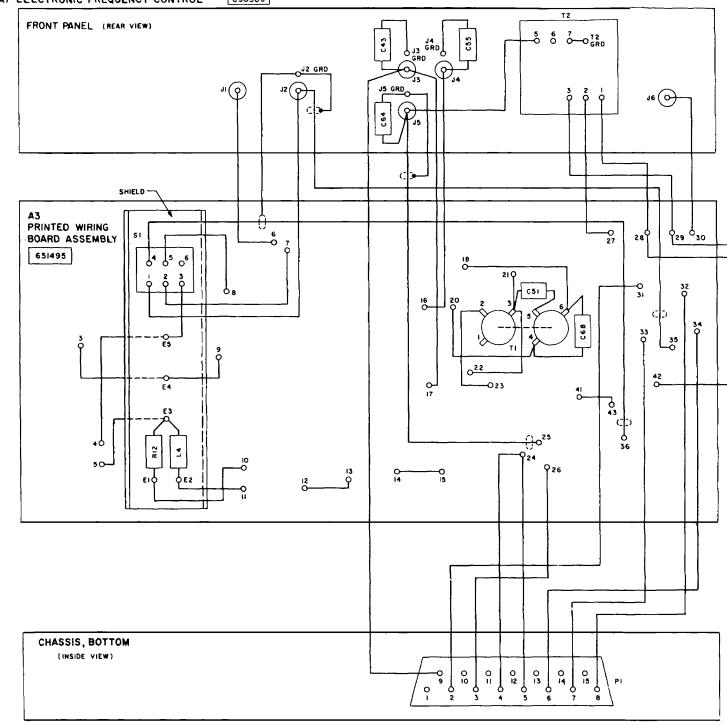

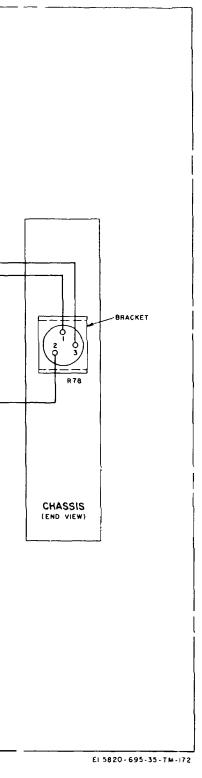

| 5-67                    | Electronic frequency control 1A7, wiring diagram                 | 5-149              |

| 5-68(1)                 | Electronic frequency control 1A7, parts location and             |                    |

|                         | printed wiring diagram (Part 1 of 2)                             | 5-151              |

| 5-68(2)                 | Electronic frequency control 1A7, parts location and             |                    |

|                         | printed wiring diagram (Part 2 of 2)                             | 5-153              |

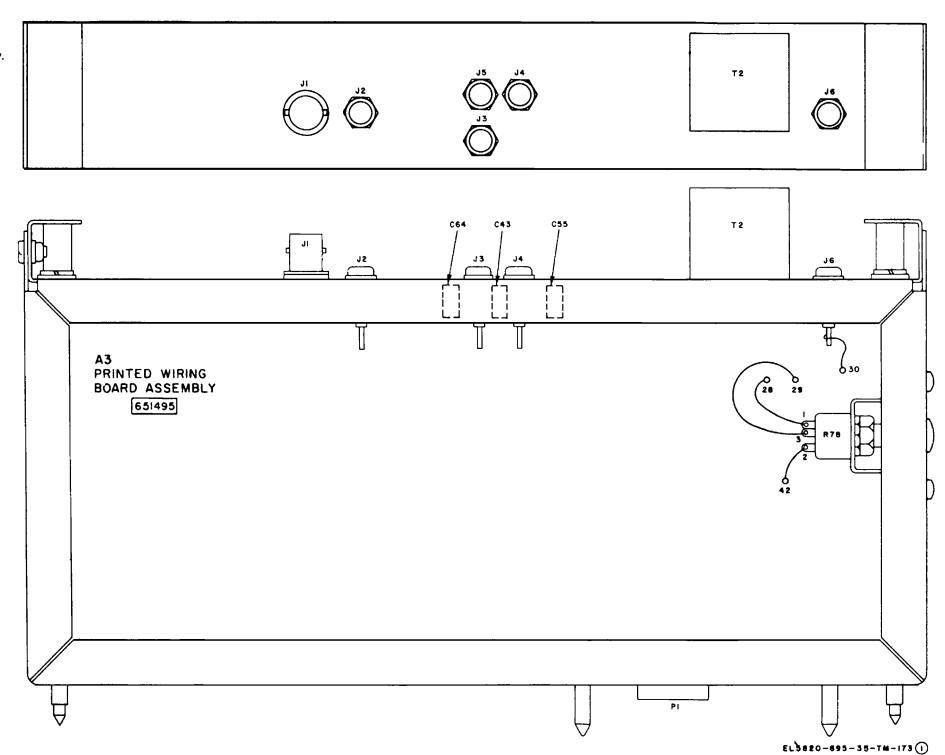

| 5-69                    | Radio transmitter modulator 1A8, wiring diagram                  | 5-155              |

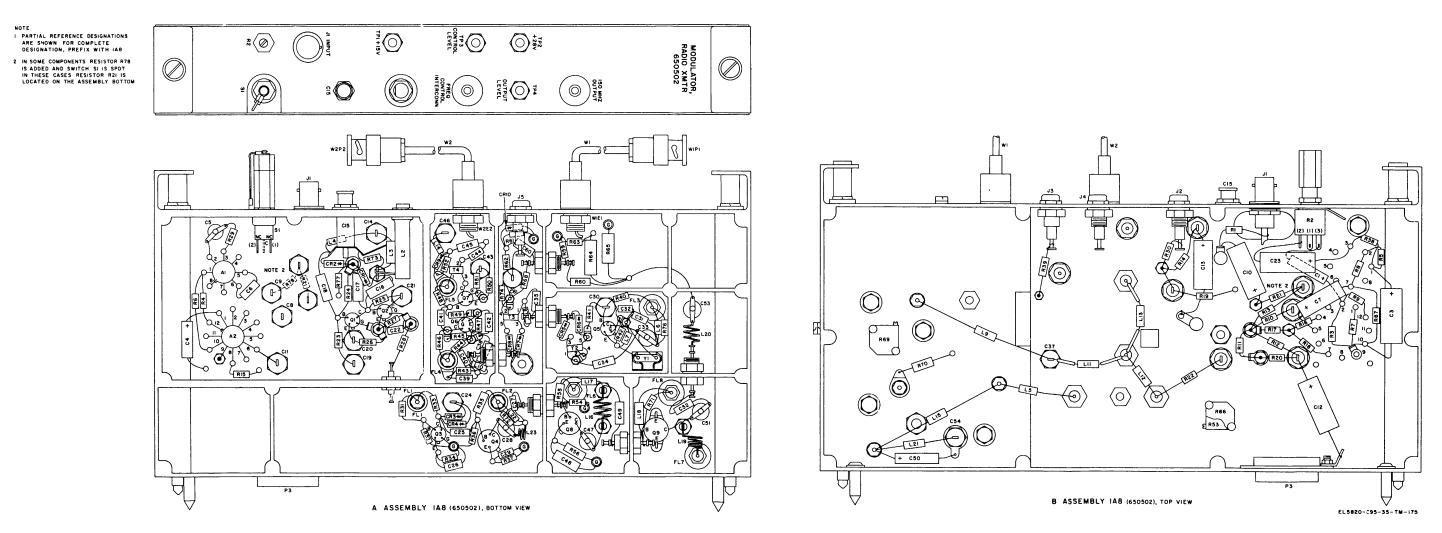

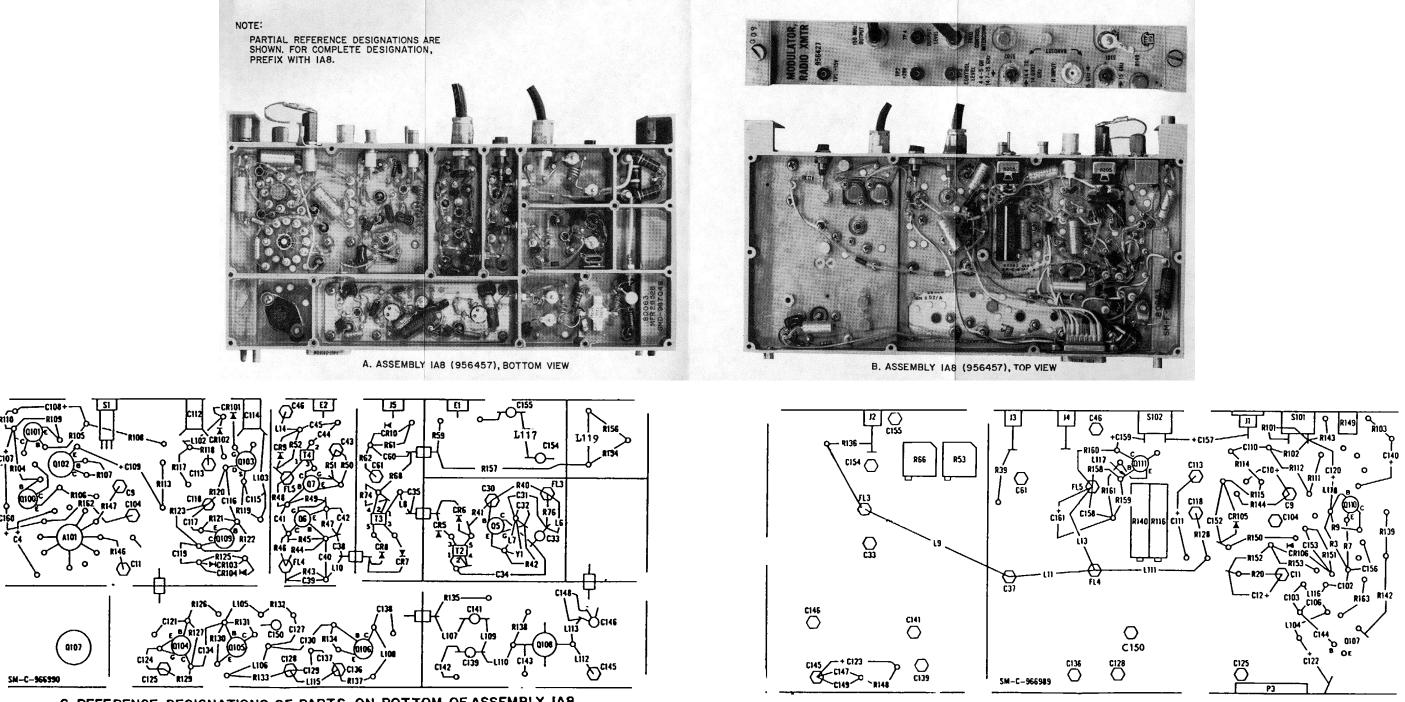

| 5-70                    | Radio transmitter modulator 1A8, parts location                  | 5-157              |

| 5-70.1                  | Radio transmitter modulator 1A8 (956427), parts location diagram | 5-157.1            |

| 5-71                    | Transmitter frequency mixer Stage 1A9, parts location            | 5-159              |

| 5-72                    | Transmitter frequency multiplier group 1A10, parts               |                    |

|                         | location                                                         | 5-161              |

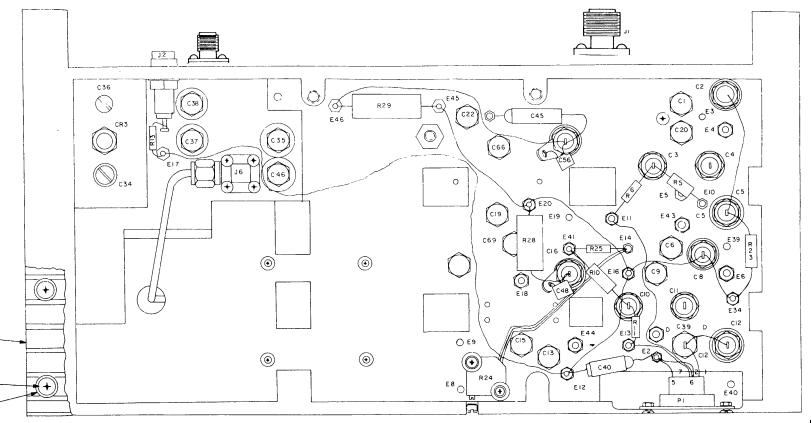

| 5-73                    | Transmitter amplifier-frequency multiplier 1A11,                 |                    |

|                         | wiring diagram                                                   | 5-163              |

| 5-74                    | Transmitter amplifier-frequency multiplier 1A11, parts location  | 5-165              |

| 5-75                    | Cable digital regenerator 1A12A2, parts location and             |                    |

|                         | printed wiring diagram, synchronous mode                         | 5-167              |

| 5-75.1                  | Cable digital regenerator 1A12A13, parts location and            |                    |

|                         | printed wiring diagram, asynchronous mode                        | 5-168.1            |

| 5-76                    | Cable Control-Comparator 1A12A3, Parts Location and              |                    |

|                         | printed wiring diagram, synchronous mode                         | 5-169              |

| 5-76.1                  | Cable control-comparator 1A12A14, parts location and             |                    |

|                         | printed wiring diagram, asynchronous mode                        | 5-170.1            |

| 5-77                    | Cable digital processor 1A12A4, parts location and               |                    |

|                         | printed wiring diagram                                           | 5-171              |

| 5-78                    | Alarm monitor 1A12A5, parts location and printed                 |                    |

|                         | wiring diagram, synchronous mode                                 | 5-173              |

| 5-78.1                  | Alarm monitor 1A12A15, parts location and printed                |                    |

|                         | Wiring diagram, asynchronous mode                                | 5-174.1            |

| 5-79                    | AF amplifier 1A12A6, parts location and printed                  |                    |

|                         | wiring diagram                                                   | 5-175              |

| 5-80                    | Radio amplifier-detector 1A12A7, parts location and              |                    |

| /                       | printed wiring diagram                                           | 5-177              |

| 5-81                    | Radio digital regenerator 1A12A8, parts location and             |                    |

|                         | printed wiring diagram                                           | 5-179              |

| 5-82                    | Radio control-comparator 1A12A9, parts location and              | <b>F</b> 404       |

| 5 00                    | printed wiring diagram                                           | 5-181              |

| 5-83                    | Radio digital processor 1A12A10, parts location and              | 5 400              |

|                         | printed wiring diagram, synchronous mode                         | 5-183              |

| 5-83.1                  | Radio digital processor 1A12A16, parts location and              | E 404 4            |

| E 92 2                  | printed wiring diagram, asynchronous mode                        | 5-184.1            |

| 5-83.2                  | Digital data combiner 1A12, parts location and printed           | E 101 0            |

| 5 00 0                  | wiring diagram                                                   | 5-184.3            |

| 5-83.3                  | Multiplexer, digital orderwire 1A12A1, parts location            | E 101 E            |